Technology of Enterprise Solid State Drive

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2020 ANNUAL MEMBERS MEETING October 22, 2020 8AM Pacific / 11AM Eastern – Teleconference (See Next Page for Dial-In and Zoom Instructions)

2020 ANNUAL MEMBERS MEETING October 22, 2020 8AM Pacific / 11AM Eastern – Teleconference (See Next Page for Dial-in and Zoom Instructions) 1 | ©2020 Storage Networking Industry Association. All Rights Reserved. Conference Call Dial-in and Zoom Info https://www.snia.org/annualmeeting Link will start Zoom meeting – afterwards, redirects to copy of the presentation materials Teleconference/Zoom coordinates: Zoom Meeting ID: 988 4674 5668 Passcode: 102220 https://zoom.us/j/98846745668?pwd=SW5BUzAxdUJZVDFhTmhPS2VNd0FKZz09 One tap mobile +16699009128,,98846745668#,,,,,,0#,,102220# US (San Jose) +13462487799,,98846745668#,,,,,,0#,,102220# US (Houston) +16465588656,,98846745668#,,,,,,0#,,102220# US (New York) Find your local number: https://zoom.us/u/aekOw6XZjj 2 | ©2020 Storage Networking Industry Association. All Rights Reserved. Zoom Format – Attendee Guidance . Enter Name (Company) on your Zoom Login/Attendee Info . Everyone will be on Mute, except the Moderator/Speaker . You can unmute yourself if you would like to say something . Voting Member Company Primary/Alternate representatives, please identify yourself when joining . Remain on Mute when not speaking . Use the Chat Icon to text message the group or a particular person . Use Raised Hand function under “participants” icon 3 | ©2020 Storage Networking Industry Association. All Rights Reserved. 2020 Annual Members Meeting Agenda . Greetings and Roll Call – Michael Oros, Executive Director . FY2019: Annual Report published . Motion to Approve 2019 Meeting Minutes – Jim Pappas, SNIA Secretary . Fiscal Report (2019 Annual Report) – Sue Amarin, SNIA Treasurer . FY2020: SNIA update and achievements to date – Michael Oros, Executive Director . FY2021: What’s ahead for SNIA – J Metz, Ph.D, SNIA Chairman . Special Guest Speakers: EPA: Ryan Fogle; DMTF: Jeff Hilland; NVM Express: Amber Huffman . -

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan Shozo Saito Chairman, ISSM2020 Organizing Committee Device & System Platform Development Center Co., Ltd. Shuichi Inoue, ATONARP INC. It is our great pleasure to announce that The 28th annual International Symposium on Semiconductor Manufacturing (ISSM) 2020 will be held on December 15-16, 2020 at KFC Hall, Ryogoku, Tokyo in cooperation with e-Manufacturing & Design Collaboration Symposium (eMDC) which is sponsored by TSIA with support from SEMI and GSA. The program will feature keynote speeches by world leading speakers, timely and highlighted topics and networking sessions focusing on equipment/materials/software/services with suppliers' exhibits. ISSM continues to contribute to the growth of the semiconductor industry through its infrastructure for networking, discussion, and information sharing among the world's professionals. We would like you to cooperate with us by supporting the ISSM 2020. Please see the benefit of ISSM2020 sponsorship. Conference Overview Date: December 15-16, 2020 Location: KFC (Kokusai Fashion Center) Hall 1-6-1 Yokoami Sumidaku, Tokyo 130-0015 Japan +81-3-5610-5810 Co-Sponsored by: IEEE Electron Devices Society Minimal Fab Semiconductor Equipment Association of Japan (SEAJ) Semiconductor Equipment and Materials International (SEMI) Taiwan Semiconductor Industry Association (TSIA) Endorsement by: The Japan Society of Applied Physics Area of Interest: Fab Management Factory Design & Automated Material -

Filesystem Considerations for Embedded Devices ELC2015 03/25/15

Filesystem considerations for embedded devices ELC2015 03/25/15 Tristan Lelong Senior embedded software engineer Filesystem considerations ABSTRACT The goal of this presentation is to answer a question asked by several customers: which filesystem should you use within your embedded design’s eMMC/SDCard? These storage devices use a standard block interface, compatible with traditional filesystems, but constraints are not those of desktop PC environments. EXT2/3/4, BTRFS, F2FS are the first of many solutions which come to mind, but how do they all compare? Typical queries include performance, longevity, tools availability, support, and power loss robustness. This presentation will not dive into implementation details but will instead summarize provided answers with the help of various figures and meaningful test results. 2 TABLE OF CONTENTS 1. Introduction 2. Block devices 3. Available filesystems 4. Performances 5. Tools 6. Reliability 7. Conclusion Filesystem considerations ABOUT THE AUTHOR • Tristan Lelong • Embedded software engineer @ Adeneo Embedded • French, living in the Pacific northwest • Embedded software, free software, and Linux kernel enthusiast. 4 Introduction Filesystem considerations Introduction INTRODUCTION More and more embedded designs rely on smart memory chips rather than bare NAND or NOR. This presentation will start by describing: • Some context to help understand the differences between NAND and MMC • Some typical requirements found in embedded devices designs • Potential filesystems to use on MMC devices 6 Filesystem considerations Introduction INTRODUCTION Focus will then move to block filesystems. How they are supported, what feature do they advertise. To help understand how they compare, we will present some benchmarks and comparisons regarding: • Tools • Reliability • Performances 7 Block devices Filesystem considerations Block devices MMC, EMMC, SD CARD Vocabulary: • MMC: MultiMediaCard is a memory card unveiled in 1997 by SanDisk and Siemens based on NAND flash memory. -

SATA 6Gb/S 3I+1 SSD Hybrid Pcie Quick Installation Guide

SATA 6Gb/s 3i+1 SSD Hybrid PCIe Quick Installation Guide Introduction The SATA 6Gb/s 3i+1 SSD Hybrid PCIe is a high performance SATA host adapter which adds three Serial ATA 6Gb/s channels and one SATA SSD socket to your PCIe-equipped computer and helps users to save more space in their computer. Features and Benefits • Compliant with Serial ATA specification, Revision 3.0 • Built-in socket for a 2.5" SATA SSD for space saving and superior drive performance • Hybrid (HyperDuo) enables 80% of SSD performance at one-third the cost • Hardware RAID to offload the host CPU for max performance. Supports RAID 0, 1 & 10 04-0897A 1 • Supports Port Multiplier FIS-based and Native Command Queuing (NCQ) • Supports TRIM to extend the life of SSDs for maximum durability System Requirements • Desktop PC with an available 4-lane (or more) PCIe slot • Windows® 8 (32-/64-bit) / 7 (32-/64-bit) / Vista (32-/64-bit) / XP (32-/64-bit) /Server 2003 & 2008 (32/64-bit) / Server 2008 R2 Package Contents • SATA 6Gb/s 3i+1 SSD Hybrid PCIe • SATA data cables (2) • Screws (4) • Driver CD • Quick installation guide 2 Layout + - HDD LED pins (Front chassis LED) 3 SATA internal connectors Screw holes SSD slot Figure 1: Layout Application Three HDDs or SSDs connected to the internal SATA channels One SSD installed to the SSD slot Figure 2: Application 3 Hardware Installation SSD Installation Install the 2.5" SATA SSD to the SATA 6Gb/s 3i+1 SSD Hybrid PCIe before card installation. 1. Simply insert the SATA SSD to end of the SSD slot. -

Federal Register/Vol. 85, No. 97/Tuesday, May 19, 2020/Notices

Federal Register / Vol. 85, No. 97 / Tuesday, May 19, 2020 / Notices 29975 DEPARTMENT OF JUSTICE Register pursuant to Section 6(b) of the No other changes have been made in Act on April 12, 2019 (84 FR 14973). either the membership or planned Antitrust Division activity of the group research project. Suzanne Morris, Membership in this group research Notice Pursuant to the National Chief, Premerger and Division Statistics, project remains open, and Pistoia Cooperative Research and Production Antitrust Division. Alliance, Inc. intends to file additional Act of 1993—Silicon Integration [FR Doc. 2020–10730 Filed 5–18–20; 8:45 am] written notifications disclosing all Initiative, Inc. BILLING CODE P changes in membership. On May 28, 2009, Pistoia Alliance, Notice is hereby given that, on April Inc. filed its original notification DEPARTMENT OF JUSTICE 23, 2020, pursuant to Section 6(a) of the pursuant to Section 6(a) of the Act. The Department of Justice published a notice National Cooperative Research and Antitrust Division Production Act of 1993, 15 U.S.C. 4301 in the Federal Register pursuant to et seq. (‘‘the Act’’), Silicon Integration Notice Pursuant to the National Section 6(b) of the Act on July 15, 2009 Initiative, Inc. (‘‘Si2’’) has filed written Cooperative Research and Production (74 FR 34364). notifications simultaneously with the Act of 1993—Pistoia Alliance, Inc. The last notification was filed with the Department on February 6, 2020. A Attorney General and the Federal Trade notice was published in the Federal Commission disclosing changes in its Notice is hereby given that, on April 24, 2020, pursuant to Section 6(a) of the Register pursuant to Section 6(b) of the membership. -

How Controllers Maximize SSD Life

SSSI TECH NOTES How Controllers Maximize SSD Life January 2013 by SNIA SSSI Member: Jim Handy Objective Analysis “The SSD Guy” www.snia.org1 About the Solid State Storage Initiative The SNIA Solid State Storage Initiative (SSSI) fosters the growth and success of the market for solid state storage in both enterprise and client environ- ments. Members of the SSSI work together to promote the development of technical standards and tools, educate the IT communities about solid state storage, perform market outreach that highlights the virtues of solid state storage, and collaborate with other industry associations on solid state stor- age technical work. SSSI member companies come from a wide variety of segments in the SSD industry www.snia.org/forums/sssi/about/members. How Controllers Maximize SSD Life by SNIA SSSI Member: Jim Handy “The SSD Guy”, Objective Analysis Table of Contents Introduction 2 How Controllers Maximize SSD Life 2 Better Wear Leveling 3 External Data Buffering 6 Improved ECC 7 Other Error Management 9 Reduced Write Amplification 10 Over Provisioning 11 Feedback on Block Wear 13 Internal NAND Management 14 1 Introduction This booklet contains a collection of posts from Jim Handy’s SSD Guy blog www.TheSSDGuy.com which explores the various techniques designers use to increase SSD life. How Controllers Maximize SSD Life How do controllers maximize the life of an SSD? After all, MLC flash has a lifetime of only 10,000 erase/write cycles or fewer and that is a very small number compared to the write traffic an SSD is expected to see in a high- workload environment, especially in the enterprise. -

Parafs: a Log-Structured File System to Exploit the Internal Parallelism of Flash Devices

ParaFS: A Log-Structured File System to Exploit the Internal Parallelism of Flash Devices Jiacheng Zhang, Jiwu Shu, Youyou Lu Tsinghua University 1 Outline • Background and Motivation • ParaFS Design • Evaluation • Conclusion 2 Solid State Drives – Internal Parallelism • Internal Parallelism – Channel Level, Chip Level, Die Level, Plane Level – Chips in one package share the same 8/16-bit-I/O bus, but have separated chip enable (CE) and ready/busy (R/B) control signals. – Each die has one internal R/B signal. – Each plane contains thousands of flash blocks and one data register. ü Internal Parallelism à High Bandwidth. Die Level Plane Level Channel Level Block 0 Block 0 Block 1 Block 1 H/W Interface Flash Flash Chip Chip Block ... Block ... Host FTL Register Register Interconnect Plane 0 Plane 1 Flash Flash Die 0 Die 1 Chip Chip Chip Level Flash File Systems • Log-structured File System – Duplicate Functions: Space Allocation, Garbage Collection. – Semantic Isolation: FTL Abstraction, Block I/O Interface, Log on Log. Log-structured File System Namespace Alloc. GC READ / WRITE / TRIM FTL Mapping Alloc. GC WL ECC Channel 0 Channel 1 Channel N … Flash Flash Flash Flash Memory 4 Observation • F2FS vs. EXt4 (under heavy write traffic) – YCSB: 1000w random Read and Update operations – 16GB flash space + 24GB write traffic 100 EXT4 F2FS 75 7 50 6 5 25 4 (%) Efficiency GC 0 3 1 4 8 16 32 25000 2 20000 1 Blocks Normalized Throughput Normalized 0 15000 1 4 8 16 32 10000 Number of Channels 5000 F2FS has poorer performance than Ext4 Recycled of # 0 on SSDs. -

SD Supported Media 08-03-2020 Hs

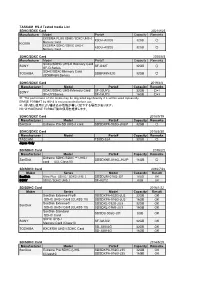

TASCAM HS-2 Tested media List SDHC/SDXC Card 2021/8/25 Manufacturer Model Parts# Capacity Remarks EXCERIA PLUS SDHC/SDXC UHS-I KSDH-A032G 32GB ○ Memory Card KIOXIA EXCERIA SDHC/SDXC UHS-I KSDU-A032G 32GB ○ Memory Card SDHC/SDXC Card 2020/8/3 Manufacturer Model Parts# Capacity Remarks SDXC/SDHC UHS-II IMemory Card SONY SF-G32T 32GB ○ SF-G Series SDHC/SDXCIMemory Card TOSHIBA SDBR48N32G 32GB ○ (SDBR48N Series) SDHC/SDXC Card 2019/4/8 Manufacturer Model Parts# Capacity Remarks SDXC/SDHC UHS-IMemory Card SF-32UY3 32GB ○*1 SONY SF-UY3Series SF-16UY3 16GB ○*1 *1: The performace of the media may be degraded significantly if it will be used repeatedly. ERASE FORMAT by HS-2 is recommended before use. *1: 繰り返し使用により書き込み性能が著しく低下する場合があります。 HS-2IでのERASE FORMAT後の使用を推奨します。 SDHC/SDXC Card 2018/9/19 Manufacturer Model Parts# Capacity Remarks SanDisk Extreme Pro SD UHS-II card SDSDXPK-032G-JNJIP 32GB ○ SDHC/SDXC Card 2018/5/30 Manufacturer Model Parts# Capacity Remarks TASCAM TSQD-32A 32GB ○ Japan Only SD/SDHC Card 2018/2/2 Manufacturer Model Parts# Capacity Remarks Extreme SDHC/SDXC™ UHS-I SanDisk SDSDXNE-016G-JNJIP 16GB ○ card (U3, Class10) SD/SDHC Card 2016/7/22 Maker Series Model Capacity Result SanDisk Ultra Plus SDHC/ SDXC UHS-I SDSDUM-016G-J01 16GB OK SONY SDXC/SDHC UHS-I SF-8UY2 8GB OK SD/SDHC Card 2016/1/22 Maker Series Model Capacity Result SanDisk Extreme Pro® SDSDXPA-032G-JU3 32GB OK SDHC UHS-I Card (CLASS 10) SDSDXPA-016G-JU3 16GB OK SanDisk Extreme® SDSDXL-032G-JU3 32GB OK SanDisk SDHC UHS-I Card (CLASS 10) SDSDXL-016G-JU3 16GB OK SanDisk Standard -

Improving Endurance with Garbage Collection, TRIM and Wear Leveling

® Application Note Solid State Storage and Memory AN07-0819-01 Improving Endurance with Garbage Collection, TRIM and Wear Leveling Introduction Prior to the advent of solid state drives (SSD), hard disk drives (HDD) were the primary storage medium. HDDs use heads and platters to store data and can be written to and erased an almost unlimited number of times, assuming no failure of mechanical or circuit components (one of the main drawbacks of HDDs for industrial applications). SSDs, on the other hand, have no moving parts, thus are much more durable; however, they only support a finite number of program/erase (P/E)1 operations. For single-level cell (SLC) NAND, each cell can be programmed/erased 60,000 to 100,000 times. Wear-leveling and other flash management techniques, while will use some of the cycles, provide protection for the NAND and the data on the SSD. These are part of the Write amplification factor (WAF)3. The final number is typically translated as Terabytes Written (TBW)2. For (industrial-grade) multi-level cell (MLC) and triple-level cell (TLC), each cell can be programmed/erased 3,000 to 10,000 times. These conventional NAND flash types use what is referred to as “floating gate” technology whereby during writing operations, tunnel current passes through the oXide layer of the floating gate in the NAND cell (Figure 1.). Figure 1. NAND Flash Floating Gate This occurrence, known as electron tunneling causes the oxide layer to degrade with each charged/trapped electron; the more the cell is programmed (written to or erased), the faster it degrades, eventually causing the cell block to wear out where it then cannot be programmed any longer and turns into a read-only device. -

UNIVERSITY of CALIFORNIA, SAN DIEGO Model and Analysis of Trim

UNIVERSITY OF CALIFORNIA, SAN DIEGO Model and Analysis of Trim Commands in Solid State Drives A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering (Intelligent Systems, Robotics, and Control) by Tasha Christine Frankie Committee in charge: Ken Kreutz-Delgado, Chair Pamela Cosman Philip Gill Gordon Hughes Gert Lanckriet Jan Talbot 2012 The Dissertation of Tasha Christine Frankie is approved, and it is acceptable in quality and form for publication on microfilm and electronically: Chair University of California, San Diego 2012 iii TABLE OF CONTENTS Signature Page . iii Table of Contents . iv List of Figures . vi List of Tables . x Acknowledgements . xi Vita . xii Abstract of the Dissertation . xiv Chapter 1 Introduction . 1 Chapter 2 NAND Flash SSD Primer . 5 2.1 SSD Layout . 5 2.2 Greedy Garbage Collection . 6 2.3 Write Amplification . 8 2.4 Overprovisioning . 10 2.5 Trim Command . 11 2.6 Uniform Random Workloads . 11 2.7 Object Based Storage . 13 Chapter 3 Trim Model . 15 3.1 Workload as a Markov Birth-Death Chain . 15 3.1.1 Steady State Solution . 17 3.2 Interpretation of Steady State Occupation Probabilities . 18 3.3 Region of Convergence of Taylor Series Expansion . 22 3.4 Higher Order Moments . 23 3.5 Effective Overprovisioning . 24 3.6 Simulation Results . 26 Chapter 4 Application to Write Amplification . 35 4.1 Write Amplification Under the Standard Uniform Random Workload . 35 4.2 Write Amplification Analysis of Trim-Modified Uniform Random Workload . 37 4.3 Alternate Models for Write Amplification Under the Trim-Modified Uniform Random Workload . -

Synnex Corporate 2021 Line Card

SYNNEX CORPORATE 2021 LINE CARD Corporate Headquarters Fremont, California* Sales Headquarters Greenville, South Carolina Warehouse Locations 1 Tracy, California 3 5 2 Chantilly, Virginia 6 10 3 Romeoville, Illinois 1 4 Richardson, Texas 2 5 Monroe, New Jersey 8 6 Grove City, Ohio 9 7 Miami, Florida 4 8 Southaven, Mississippi* 9 Chino, California 10 Columbus, Ohio 7 *ISO-9001:2015 Manufacturing Facilities ADVANCING IT INNOVATIONS SERVICES Map your destination to increased productivity, Sounds simple, but at • GSA Schedule cost savings and overall business success. Our SYNNEX we understand that • ECExpress Online Ordering true business growth requires • Software Licensing distribution centers are strategically located across access to meaningful, tangible the United States to provide you with product business infrastructure, tools, • Reseller Marketing Services where you need it when you need it. Each of our and resources. That’s why • Leasing distribution centers provides our customers with over the last year we’ve • Integration Services invested heavily in providing • Trade Up warehouse ratings of nearly 100% in accuracy and our partners with high-impact • A Menu of Financial Services business services, designed PPS (pick, pack and ship) performance. Couple that • SYNNEX Service Network with unsurpassed service from our infrastructure from the ground up to provide real value, and delivering on • ASCii Program support, giving you one more reason why you our commitment to provide • PRINTSolv should be doing business with SYNNEX. That’s -

RZ/V Series, Visionai ASSP RZ/V2M Datasheet

DATASHEET RZ/V Series, VisionAI_ASSP RZ/V2M R01DS0372EJ0100 Rev.1.00 Apr 28, 2021 Section 1 Overview 1.1 Features This LSI chip includes the AI dedicated accelerator (DRP-AI) and 4K-compatible image signal processor (ISP). This processor is vision-AI ASSP for real-time human and object recognition. The AI dedicated hardware IP, DRP-AI, configured with the dynamic reconfigurable processor (DRP) and AI-MAC, combines both a high-speed AI inference and low power consumption and realizes 1TOPS/W class power performance. In addition, the image signal processor (ISP) is highly robust, producing a stable image independent of the environment, allowing for a high AI recognition accuracy. With these features, this LSI realizes low power consumption, which is a critical factor for embedded devices, making heat dissipation measures easier. The result is that it is ideal for vision AI applications in a wide range of embedded markets, including surveillance security, retail, office automation (OA), industrial automation, and robotics. In addition, this LSI also features abundant high-speed communication interfaces such as USB 3.1, PCI Express®, Gigabit Ethernet, and many CPU peripheral functions, so it can also be used in a variety of applications. CPU and DDR Memory Interfaces High Speed Interfaces ● Cortex®-A53 Dual (996 MHz maximum) ● 1× Gigabit Ethernet ● 32-bit LPDDR4-3200 ● 1× USB3.1 Gen1 Host/Peripheral ® ● 1× PCIe Gen 2 (2 lanes) ● 2× SDIO 3.0 Vision and AI ● 1× NAND Flash Interface ONFI1.0 ● AI accelerator: DRP-AI (1.0 TOPS/W class) ● 1×