Introduction to High Performance Computing

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Software Development Career Pathway

Career Exploration Guide Software Development Career Pathway Information Technology Career Cluster For more information about NYC Career and Technical Education, visit: www.cte.nyc Summer 2018 Getting Started What is software? What Types of Software Can You Develop? Computers and other smart devices are made up of Software includes operating systems—like Windows, Web applications are websites that allow users to contact management system, and PeopleSoft, a hardware and software. Hardware includes all of the Apple, and Google Android—and the applications check email, share documents, and shop online, human resources information system. physical parts of a device, like the power supply, that run on them— like word processors and games. among other things. Users access them with a Mobile applications are programs that can be data storage, and microprocessors. Software contains Software applications can be run directly from a connection to the Internet through a web browser accessed directly through mobile devices like smart instructions that are stored and run by the hardware. device or through a connection to the Internet. like Firefox, Chrome, or Safari. Web browsers are phones and tablets. Many mobile applications have Other names for software are programs or applications. the platforms people use to find, retrieve, and web-based counterparts. display information online. Web browsers are applications too. Desktop applications are programs that are stored on and accessed from a computer or laptop, like Enterprise software are off-the-shelf applications What is Software Development? word processors and spreadsheets. that are customized to the needs of businesses. Popular examples include Salesforce, a customer Software development is the design and creation of Quality Testers test the application to make sure software and is usually done by a team of people. -

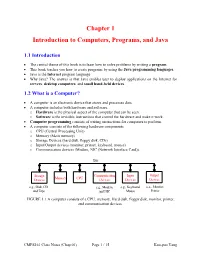

Chapter 1 Introduction to Computers, Programs, and Java

Chapter 1 Introduction to Computers, Programs, and Java 1.1 Introduction • The central theme of this book is to learn how to solve problems by writing a program . • This book teaches you how to create programs by using the Java programming languages . • Java is the Internet program language • Why Java? The answer is that Java enables user to deploy applications on the Internet for servers , desktop computers , and small hand-held devices . 1.2 What is a Computer? • A computer is an electronic device that stores and processes data. • A computer includes both hardware and software. o Hardware is the physical aspect of the computer that can be seen. o Software is the invisible instructions that control the hardware and make it work. • Computer programming consists of writing instructions for computers to perform. • A computer consists of the following hardware components o CPU (Central Processing Unit) o Memory (Main memory) o Storage Devices (hard disk, floppy disk, CDs) o Input/Output devices (monitor, printer, keyboard, mouse) o Communication devices (Modem, NIC (Network Interface Card)). Bus Storage Communication Input Output Memory CPU Devices Devices Devices Devices e.g., Disk, CD, e.g., Modem, e.g., Keyboard, e.g., Monitor, and Tape and NIC Mouse Printer FIGURE 1.1 A computer consists of a CPU, memory, Hard disk, floppy disk, monitor, printer, and communication devices. CMPS161 Class Notes (Chap 01) Page 1 / 15 Kuo-pao Yang 1.2.1 Central Processing Unit (CPU) • The central processing unit (CPU) is the brain of a computer. • It retrieves instructions from memory and executes them. -

インテル® Parallel Studio XE 2020 リリースノート

インテル® Parallel Studio XE 2020 2019 年 12 月 5 日 内容 1 概要 ..................................................................................................................................................... 2 2 製品の内容 ........................................................................................................................................ 3 2.1 インテルが提供するデバッグ・ソリューションの追加情報 ..................................................... 5 2.2 Microsoft* Visual Studio* Shell の提供終了 ........................................................................ 5 2.3 インテル® Software Manager .................................................................................................... 5 2.4 サポートするバージョンとサポートしないバージョン ............................................................ 5 3 新機能 ................................................................................................................................................ 6 3.1 インテル® Xeon Phi™ 製品ファミリーのアップデート ......................................................... 12 4 動作環境 .......................................................................................................................................... 13 4.1 プロセッサーの要件 ...................................................................................................................... 13 4.2 ディスク空き容量の要件 .............................................................................................................. 13 4.3 オペレーティング・システムの要件 ............................................................................................. 13 -

Applying the Roofline Performance Model to the Intel Xeon Phi Knights Landing Processor

Applying the Roofline Performance Model to the Intel Xeon Phi Knights Landing Processor Douglas Doerfler, Jack Deslippe, Samuel Williams, Leonid Oliker, Brandon Cook, Thorsten Kurth, Mathieu Lobet, Tareq Malas, Jean-Luc Vay, and Henri Vincenti Lawrence Berkeley National Laboratory {dwdoerf, jrdeslippe, swwilliams, loliker, bgcook, tkurth, mlobet, tmalas, jlvay, hvincenti}@lbl.gov Abstract The Roofline Performance Model is a visually intuitive method used to bound the sustained peak floating-point performance of any given arithmetic kernel on any given processor architecture. In the Roofline, performance is nominally measured in floating-point operations per second as a function of arithmetic intensity (operations per byte of data). In this study we determine the Roofline for the Intel Knights Landing (KNL) processor, determining the sustained peak memory bandwidth and floating-point performance for all levels of the memory hierarchy, in all the different KNL cluster modes. We then determine arithmetic intensity and performance for a suite of application kernels being targeted for the KNL based supercomputer Cori, and make comparisons to current Intel Xeon processors. Cori is the National Energy Research Scientific Computing Center’s (NERSC) next generation supercomputer. Scheduled for deployment mid-2016, it will be one of the earliest and largest KNL deployments in the world. 1 Introduction Moving an application to a new architecture is a challenge, not only in porting of the code, but in tuning and extracting maximum performance. This is especially true with the introduction of the latest manycore and GPU-accelerated architec- tures, as they expose much finer levels of parallelism that can be a challenge for applications to exploit in their current form. -

On the Cognitive Prerequisites of Learning Computer Programming

On the Cognitive Prerequisites of Learning Computer Programming Roy D. Pea D. Midian Kurland Technical Report No. 18 ON THE COGNITIVE PREREQUISITES OF LEARNING COMPUTER PROGRAMMING* Roy D. Pea and D. Midian Kurland Introduction Training in computer literacy of some form, much of which will consist of training in computer programming, is likely to involve $3 billion of the $14 billion to be spent on personal computers by 1986 (Harmon, 1983). Who will do the training? "hardware and software manu- facturers, management consultants, -retailers, independent computer instruction centers, corporations' in-house training programs, public and private schools and universities, and a variety of consultants1' (ibid.,- p. 27). To date, very little is known about what one needs to know in order to learn to program, and the ways in which edu- cators might provide optimal learning conditions. The ultimate suc- cess of these vast training programs in programming--especially toward the goal of providing a basic computer programming compe- tency for all individuals--will depend to a great degree on an ade- quate understanding of the developmental psychology of programming skills, a field currently in its infancy. In the absence of such a theory, training will continue, guided--or to express it more aptly, misguided--by the tacit Volk theories1' of programming development that until now have served as the underpinnings of programming instruction. Our paper begins to explore the complex agenda of issues, promise, and problems that building a developmental science of programming entails. Microcomputer Use in Schools The National Center for Education Statistics has recently released figures revealing that the use of micros in schools tripled from Fall 1980 to Spring 1983. -

Introduction to Intel Xeon Phi (“Knights Landing”) on Cori

Introduction to Intel Xeon Phi (“Knights Landing”) on Cori" Brandon Cook! Brian Friesen" 2017 June 9 - 1 - Knights Landing is here!" • KNL nodes installed in Cori in 2016 • “Pre-produc=on” for ~ 1 year – No charge for using KNL nodes – Limited access (un7l now!) – Intermi=ent down7me – Frequent so@ware changes • KNL nodes on Cori will soon enter produc=on – Charging Begins 2017 July 1 - 2 - Knights Landing overview" Knights Landing: Next Intel® Xeon Phi™ Processor Intel® Many-Core Processor targeted for HPC and Supercomputing First self-boot Intel® Xeon Phi™ processor that is binary compatible with main line IA. Boots standard OS. Significant improvement in scalar and vector performance Integration of Memory on package: innovative memory architecture for high bandwidth and high capacity Integration of Fabric on package Three products KNL Self-Boot KNL Self-Boot w/ Fabric KNL Card (Baseline) (Fabric Integrated) (PCIe-Card) Potential future options subject to change without notice. All timeframes, features, products and dates are preliminary forecasts and subject to change without further notification. - 3 - Knights Landing overview TILE CHA 2 VPU 2 VPU Knights Landing Overview 1MB L2 Core Core 2 x16 X4 MCDRAM MCDRAM 1 x4 DMI MCDRAM MCDRAM Chip: 36 Tiles interconnected by 2D Mesh Tile: 2 Cores + 2 VPU/core + 1 MB L2 EDC EDC PCIe D EDC EDC M Gen 3 3 I 3 Memory: MCDRAM: 16 GB on-package; High BW D Tile D D D DDR4: 6 channels @ 2400 up to 384GB R R 4 36 Tiles 4 IO: 36 lanes PCIe Gen3. 4 lanes of DMI for chipset C DDR MC connected by DDR MC C Node: 1-Socket only H H A 2D Mesh A Fabric: Omni-Path on-package (not shown) N Interconnect N N N E E L L Vector Peak Perf: 3+TF DP and 6+TF SP Flops S S Scalar Perf: ~3x over Knights Corner EDC EDC misc EDC EDC Streams Triad (GB/s): MCDRAM : 400+; DDR: 90+ Source Intel: All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice. -

Software Development a Practical Approach!

Software Development A Practical Approach! Hans-Petter Halvorsen https://www.halvorsen.blog https://halvorsen.blog Software Development A Practical Approach! Hans-Petter Halvorsen Software Development A Practical Approach! Hans-Petter Halvorsen Copyright © 2020 ISBN: 978-82-691106-0-9 Publisher Identifier: 978-82-691106 https://halvorsen.blog ii Preface The main goal with this document: • To give you an overview of what software engineering is • To take you beyond programming to engineering software What is Software Development? It is a complex process to develop modern and professional software today. This document tries to give a brief overview of Software Development. This document tries to focus on a practical approach regarding Software Development. So why do we need System Engineering? Here are some key factors: • Understand Customer Requirements o What does the customer needs (because they may not know it!) o Transform Customer requirements into working software • Planning o How do we reach our goals? o Will we finish within deadline? o Resources o What can go wrong? • Implementation o What kind of platforms and architecture should be used? o Split your work into manageable pieces iii • Quality and Performance o Make sure the software fulfills the customers’ needs We will learn how to build good (i.e. high quality) software, which includes: • Requirements Specification • Technical Design • Good User Experience (UX) • Improved Code Quality and Implementation • Testing • System Documentation • User Documentation • etc. You will find additional resources on this web page: http://www.halvorsen.blog/documents/programming/software_engineering/ iv Information about the author: Hans-Petter Halvorsen The author currently works at the University of South-Eastern Norway. -

Computer Programming and Database Management - Software Engineering Technology Major (SET)

Computer Programming and Database Management - Software Engineering Technology Major (SET) Program Chair: Robert (Bob) Nields, MBA • Email: [email protected] • Phone: (513) 569-1653 Co-Op Coordinator Chair: Noelle Grome, ME, MA • Email: [email protected] • Phone: (513) 569-4693 The Computer Programming and Database Management - Software Engineering Technology Major (SET) focuses on the design, development, implementation, and maintenance of software solutions used in a variety of industries and organizations. Students gain practical knowledge and experience in the software development process and methods using relevant, current programming languages, databases, and database query languages. Students also gain knowledge of core math and science concepts and skills. Graduates earn an Associate of Applied Science degree and are prepared to enter the workforce as skilled software developers/computer programmers. Graduates may continue their education in a bachelor's degree program in computer science, engineering technology, or mathematics. Although some required courses are available through evening and/or online classes, most of the required courses for the Software Engineering Technology Major are scheduled as in-person classes offered on Monday through Friday between 8 a.m. and 5 p.m. Employment Options GRADUATE STARTING SALARY Education Options PROJECTIONS: GRADUATES ARE PREPARED TO: $40,000 to $60,000 annual salary STRONG TRANSFER HISTORY: • Design and write computer programs Northern Kentucky University using programming languages NET, EMPLOYMENT OUTLOOK: University of Cincinnati Python, Java, C, and C++ Graduates of the Software Engineering Western Governors University • Develop applications using the Technology program are in demand by Wilmington College Object-Oriented Programming companies locally and nationally. Wright State University Methodology According to the U.S. -

Intel® Parallel Studio XE 2020 Update 2 Release Notes

Intel® Parallel StudIo Xe 2020 uPdate 2 15 July 2020 Contents 1 Introduction ................................................................................................................................................... 2 2 Product Contents ......................................................................................................................................... 3 2.1 Additional Information for Intel-provided Debug Solutions ..................................................... 4 2.2 Microsoft Visual Studio Shell Deprecation ....................................................................................... 4 2.3 Intel® Software Manager ........................................................................................................................... 5 2.4 Supported and Unsupported Versions .............................................................................................. 5 3 What’s New ..................................................................................................................................................... 5 3.1 Intel® Xeon Phi™ Product Family Updates ...................................................................................... 12 4 System Requirements ............................................................................................................................. 13 4.1 Processor Requirements........................................................................................................................ 13 4.2 Disk Space Requirements ..................................................................................................................... -

Effectively Using NERSC

Effectively Using NERSC Richard Gerber Senior Science Advisor HPC Department Head (Acting) NERSC: the Mission HPC Facility for DOE Office of Science Research Largest funder of physical science research in U.S. Bio Energy, Environment Computing Materials, Chemistry, Geophysics Particle Physics, Astrophysics Nuclear Physics Fusion Energy, Plasma Physics 6,000 users, 48 states, 40 countries, universities & national labs Current Production Systems Edison 5,560 Ivy Bridge Nodes / 24 cores/node 133 K cores, 64 GB memory/node Cray XC30 / Aries Dragonfly interconnect 6 PB Lustre Cray Sonexion scratch FS Cori Phase 1 1,630 Haswell Nodes / 32 cores/node 52 K cores, 128 GB memory/node Cray XC40 / Aries Dragonfly interconnect 24 PB Lustre Cray Sonexion scratch FS 1.5 PB Burst Buffer 3 Cori Phase 2 – Being installed now! Cray XC40 system with 9,300 Intel Data Intensive Science Support Knights Landing compute nodes 10 Haswell processor cabinets (Phase 1) 68 cores / 96 GB DRAM / 16 GB HBM NVRAM Burst Buffer 1.5 PB, 1.5 TB/sec Support the entire Office of Science 30 PB of disk, >700 GB/sec I/O bandwidth research community Integrate with Cori Phase 1 on Aries Begin to transition workload to energy network for data / simulation / analysis on one system efficient architectures 4 NERSC Allocation of Computing Time NERSC hours in 300 millions DOE Mission Science 80% 300 Distributed by DOE SC program managers ALCC 10% Competitive awards run by DOE ASCR 2,400 Directors Discretionary 10% Strategic awards from NERSC 5 NERSC has ~100% utilization Important to get support PI Allocation (Hrs) Program and allocation from DOE program manager (L. -

Intel® Xeon Phi™ Processor: Your Path to Deeper Insight

PRODUCT BRIEF Intel® Xeon Phi™ Processor: Your Path to Deeper Insight Intel Inside®. Breakthroughs Outside. Unlock deeper insights to solve your biggest challenges faster with the Intel® Xeon Phi™ processor, a foundational element of Intel® Scalable System Framework (Intel® SSF) What if you could gain deeper insight to pursue new discoveries, drive business innovation or shape the future using advanced analytics? Breakthroughs in computational capability, data accessibility and algorithmic innovation are driving amazing new possibilities. One key to unlocking these deeper insights is the new Intel® Xeon Phi™ processor – Intel’s first processor to deliver the performance of an accelerator with the benefits of a standard host CPU. Designed to help solve your biggest challenges faster and with greater efficiency, the Intel® Xeon Phi™ processor enables machines to rapidly learn without being explicitly programmed, in addition to helping drive new breakthroughs using high performance modeling and simulation, visualization and data analytics. And beyond computation, as a foundational element of Intel® Scalable System Framework (Intel® SSF), the Intel® Xeon Phi™ processor is part of a solution that brings together key technologies for easy-to-deploy and high performance clusters. Solve Your Biggest Challenges Faster1 Designed from the ground up to eliminate bottlenecks, the Intel® Xeon Phi™ processor is Intel’s first bootable host processor specifically designed for highly parallel workloads, and the first to integrate both memory and fabric technologies. Featuring up to 72 powerful and efficient cores with ultra-wide vector capabilities (Intel® Advanced Vector Extensions or AVX-512), the Intel® Xeon Phi™ processor raises the bar for highly parallel computing. -

Computer Programming

d. Ballpoint pens or sharpened pencils e. Blank notebook paper COMPUTER f. All competitors must create a one-page résumé and submit a hard copy to the PROGRAMMING technical committee chair at orientation. Failure to do so will result in a 10-point penalty. PURPOSE To evaluate each contestant’s preparation for Note: Your contest may also require a hard employment and to recognize outstanding copy of your résumé as part of the actual students for excellence and professionalism in contest. Check the Contest Guidelines the field of computer programming. and/or the updates page on the SkillsUSA website: http://updates.skillsusa.org. First, download and review the General Regulations at: http://updates.skillsusa.org. SCOPE OF THE CONTEST The contest uses competencies identified by the ELIGIBILITY Computing Technology Industry Association. Open to active SkillsUSA members enrolled in The specific projects chosen for national programs with computer programming as the competition will be determined by the occupational objective. Computer Programming technical committee. Knowledge Performance CLOTHING REQUIREMENTS The contest includes a written knowledge test Class E: Contest specific — Business Casual assessing knowledge of Visual Basic, Java, C++ • Official SkillsUSA white polo shirt or RPG or “other approved language.” Check • Black dress slacks (accompanied by black the Contest Guidelines and/or the updates page dress socks or black or skin-tone seamless on the SkillsUSA website: updates.skillsusa.org. hose) or black dress skirt (knee-length, accompanied by black or skin-tone Skill Performance seamless hose) The contest includes a computer programming • Black leather closed-toe dress shoes problem consisting of background information and program specifications with accompanying These regulations refer to clothing items that reference materials and description of program are pictured and described at: output requirements.