Youngsoo Shin

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Asian Development Bank–Japan Scholarship Program Brochure For

MESSAGE FROM THE DIRECTOR GENERAL The Asian Development Bank (ADB)–Japan Scholarship Program (JSP) was established in April 1988 with financing from the Government of Japan. The program has so far provided more than 3,000 students from ADB’s developing member countries with an opportunity to pursue postgraduate studies in economics, business and management, science and technology, and other development-related fields at participating academic institutions in Asia and the Pacific. The 2014/2015 academic year marks the 21st anniversary of Mongolian citizens’ acceptance into the program. In the last 20 years, the ADB–JSP has helped 125 Mongolian citizens to advance their education in various academic institutions in Asia and the Pacific. Today, the ADB–JSP scholars are working in both the government and the private sector across Mongolia—in education, business, banking and finance, and other sectors—and are making positive contributions to the country’s development. We are proud of our scholars and we continue to stay in touch with them as they progress in their chosen careers. This ADB–JSP publication for Mongolia contains general information about the program, as well as success stories of some Mongolian ADB–JSP scholars and alumni. We believe that their stories will encourage many more Mongolian citizens to become ADB–JSP scholars and realize their dreams for Mongolia’s development. Together with the Mongolian ADB–JSP alumni, I wish to express our sincere gratitude to the government and the people of Japan for their generous contribution and continued support to the ADB–JSP. Ayumi Konishi Director General East Asia Department Asian Development Bank 3 THE SCHOLARSHIP Who are Eligible? • Must be a national of an ADB-borrowing member country (applicants from countries that are no longer ADB borrowers are not eligible for the scholarship). -

Curriculum Vitae

CURRICULUM VITAE CRISTIAN VIRDOL Address Yonsei University Department of Mathematics Office Phone +82-2-2123-2584 Room 208 [email protected] Seoul 120-749 www2.math.kyushu-u.ac.jp/ virdol/ Korea Personal Data Citizenship: Romanian Employment 2013-present Yonsei University, South Korea Associate Professor 2010-2013 Kyushu University, Japan Assistant Professor 2006-2010 Columbia University, USA Ritt Assistant Professor 2005-2006 Nagoya University, Japan Researcher Education 1999-2005 UCLA, USA Ph. D. in Mathematics Advisor: Haruzo Hida 1994-1998 Bucharest University, Romania B.A. in Mathematics Visiting Positions 2014 January-February Max-Planck-Institut fur Mathematik, Germany 2013 July Institut des Hautes Etudes Scientifiques, France 2012 June Institut des Hautes Etudes Scientifiques, France 2011 June Max-Planck-Institut fur Mathematik, Germany 2010 August-November National Taiwan University, Taiwan 2010 June-July Max-Planck-Institut fur Mathematik, Germany 2009 May-August Max-Planck-Institut fur Mathematik, Germany 2005-2006 December-January Academia Sinica, Taiwan 2005 July-August University of Sydney, Australia 2004 March-October University of Sydney, Australia Short visits (up to four weeks) 2013 April Shandong University, China 2012 October Kumamoto University, Japan 2012 October Waseda University, Japan 2012 September Yonsei University, South Korea 2012 July Tohoku University, Japan 2012 April Osaka University, Japan 2012 April Hong Kong University, China 2011 October Rikkyo University, Japan 2011 October Kyoto University, Japan 2011 September Yonsei University, South Korea 2011 July Sophia University, Japan 2011 April Nagoya University, Japan 2011 February-March National Center for Theoretical Sciences (Taipei Office), Taiwan 1 CRISTIAN VIRDOL CURRICULUM VITAE Papers (1) C. Virdol, Zeta functions of twisted modular curves, Journal of the Australian Mathematical Society 80 (2006), no. -

Nagoya University PROFILE 2011-2012

Nagoya University Profile 2011–2012 Furo-cho, Chikusa-ku, Nagoya, 464-8601, Japan Phone: +81-52-789-2044 http://www.nagoya-u.ac.jp/en/ Profile 2011–2012 Table of Contents 02 Greeting from the President 03 The Hamaguchi Plan 04 Excellence in Research Fostered by a Free and Vibrant Academic Culture 19 Nurturing Future Global Leaders 30 International Cooperation 34 Nagoya University's Global Network 42 Nagoya University Outline Greeting from the President Dr. Michinari HAMAGUCHI President The Hamaguchi Plan As the President of Nagoya University, I offer you my most Nagoya University sincere greetings. I feel the magnitude of responsibility of this Education, Research, Transforming Nagoya University Administration and Finance office, which I assumed in April 2009. and Social Contribution to a World Class Institution Throughout its history, Nagoya University has done its utmost to Cultivation of Globally Effective Leaders Making Administrative and Support Functions 1. Cultivation of Globally Effective Leaders maintain a free and vibrant academic culture. As an educational • Improving the core curriculum : Strengthening More Efficient to Enable Effective Education the Institute of Liberal Arts and Sciences and Through our core curriculum, Global 30 Project, and Research institution, we aim to cultivate what we call “courageous improving learning support systems and the increase in international students to • Evaluating and reorganizing functions to ensure over 2,000 within 5 years intellectuals”: social contributors endowed with the powers of -

JAPAN Nagoya University, Tohoku University (Synthetic Chemistry, Natural Products, Coordination Chemistry, Polymer Chemistry, Etc.)

ASEAN+3 Higher Education Quality Assurance Forum Session II: Campus Asia Student Mobility in East Asia Cutting Edge Science and Technology in Chemistry and Materials - A Cooperative Asian Education Gateway for a Sustainable Society Nagoya University* and Tohoku University Project Leaders Takahiro Seki* Nagoya University*, Graduate School of Engineering, Professor Kentaro Tanaka Nagoya University, Graduate School of Science, Professor Tohoku Leaders Akihiro Morita* Tohoku University, Graduate School of Science, Professor Takayuki Doi Tohoku University, Graduate School of Pharmaceutical Sciences, Professor Creating an Organization for Innovative Education in the Fields of Chemistry and Material Science in Asia to Contribute to Sustainable Society Pohang University of Seoul National University Science and Technology Tohoku University Nanjing University Education of chemistry specialists from a central Asian base Producing leaders with a global approach in the fields of Shanghai Jiao Tong Chemistry and Material Nagoya University 2 University Science Current Conditions and Strong Points for the Establishment of the Educational Organization Nurturing Chemists with a Global Mindset for the Development of Sustainable Society JAPAN Nagoya University, Tohoku University (Synthetic Chemistry, Natural Products, Coordination Chemistry, Polymer Chemistry, etc.) CHINA KOREA Shanghai Jiao Tong University, Seoul National University, Nanjing University Pohang University of Science and Technology (Solid State Chemistry, Materials Engineering, (Nanomaterials, -

Nagoya University Profile 2019

NAGOYA 曇 NAGOYA UNIVERSITY UNIくERSITY Furo-cho, Chikusa-ku, Nagoya、464-8601, Japan Phone: +81-52-789-2044 PROFILE 2019 http://en.nagoya-u.ac.jp/ PROFILE NAGOYA UNIVERSITY 2019 .. (P も .. • . . ‘ . � / 4, "" "・ .. : 戸 “ 鼻 · ^鴫 . F .7• ・ , 鳥 / ` y-..ら 99 '1 ; ‘り 0 ♦ 9•i 9 t 1 ▲ ぃ, • · り 、1.9ー ・鳴 ‘. ー ぶ '“a , 'l , .' .I ;- /“ � ぃ ァ ' 4 、 ..... n 一ー ,ー -;., .9 b し. . i― . 胃 " _ . ‘ Iけ 偏・ ト”" t 贔 0 The Nagoya University Academic Charter In recognition of the unique role of seats of learning and 3) Nagoya University shall promote international academic their historical and social missions, this document co-operation and the education of international students. It establishes the guiding principles for scholarship at Nagoya will contribute to educational and cultural exchange with University. Nagoya University maintains a culture of free other countries, especially those in Asia. and open-minded academic endeavor and aspires to contribute to the prosperity and happiness of all people through research and education in those fields studying 3 Fundamental Policies: human beings, society, and the natural world. Above all, it Research and Education System aims to foster the harmonious development of humanity 1) Nagoya University shall study the humanities, society, and science, to conduct advanced research, and to provide and nature from an inclusive viewpoint, respond to an education that encompasses the full range of the contemporary issues, and change and enrich its education humanities, the social sciences, and the natural sciences. and research system to generate new values and a body of To these ends, we outline below the goals and guidelines knowledge based on humanitarian values. -

Editorial Board List

Publication Committee Hiroaki Masuzaki University of the Ryukyus Hiroshi Itoh Keio University Akihiro Sakurai Sapporo Medical University Takayoshi Suganami Nagoya University Toshinari Takamura Kanazawa University Kenichiro Morohashi Kyushu University Editor-in-Chief Hiroaki Masuzaki University of the Ryukyus Adrenal, Cardiovascular, Diabetes, Lipid, Obesity Associate Editor-in-Chief Tadahiro Kitamura Gunma University Hypothalamus, pituitary, Diabetes, Lipid, Obesity Kenichiro Morohashi Kyushu University Hypothalamus, pituitary, Reproductive organs, Adrenal, Cardiovascular Editors Yumiko Abe Gunma University Reproductive organs, Hypothalamus, pituitary Maki Fukami National Center for Child Health and Development Reproductive organs, Pediatric endocrinology, Molecular endocrinology, Hypothalamus, pituitary Izumi Fukuda Nippon Medical School Hypothalamus, pituitary Hidenori Fukuoka Kobe University Hypothalamus, pituitary, Molecular endocrinology, Adrenal, Cardiovascular Tomonobu Hasegawa Keio University Adrenal, Cardiovascular, Pediatric endocrinology Koshi Hashimoto Dokkyo Medical University Thyroid, Diabetes, Lipid, Obesity, Hypothalamus, pituitary, Adrenal, Cardiovascular, Molecular endocrinology Yuuki Imai Ehime University Molecular endocrinology Yasuo Imanishi Osaka City University Parathyroid, Vitamin D, Bone Daisuke Inoue Teikyo University Parathyroid, Vitamin D, Bone Yasushi Ishigaki Iwate University Diabetes, Lipid, Obesity Yasuhiro Ito Kuma Hospital Thyroid, Parathyroid, Vitamin D, Bone Shintaro Iwama Nagoya University Hypothalamus, -

Minutes of KJDB2010 Working Group Committee Meeting

Minutes of KJDB2010 Working Group Committee Meeting Date: May 29, 2010 Time: 11:00a.m.-11:30a.m. Venue: ShineVille Luxury Resort, Seogwipo-si, Jeju Self-governing Provice, Korea Present: Kyu-Young Whang Katsumi Tanaka Eui-Kyeong Hong 1. Welcome Kyu-Young Whang called the meeting at 11:30a.m. and the members approved membership of 10 new and 1 dropped member as well as new executive committee members. 2. 2010 New Members Chiemi Watanabe, Ochanomizu University, Japan Hayato Yamana, Waseda University, Japan Hiroshi Ishikawa, Shizuoka University, Japan Hwanjo Yu, POSTECH, Korea Miyuki Nakano, The University of Tokyo, Japan Toshiyuki Amagasa, University of Tsukuba, Japan Woong-Kee Loh, Sungkyul University, Korea Yongchul Oh, Korea Polytecnic University, Korea Yoshiharu Ishikawa, Nagoya University, Japan Yukiko Kawai, Kyoto Sangyo University, Japan 3. Dropped Members Byung-Kee Yi was absent for three consecutive KJDB workshops and no apology for absence was received. dropped from the membership Shojiro Nishio and Wan-Sup Cho were absent for three consecutive KJDB workshops, but apologies for absence were received. The working group chair will send them a warning message. If they do not attend the next KJDB workshop, they will be dropped from the membership without further consideration. 4. New Executive Committee Members elected Advisor: Kyu-Young Whang, KAIST Chair: Katsumi Tanaka, Kyoto University Vice Chair: Masaru Kitsuregawa, University of Tokyo Vice Chair: Eui-Kyeong Hong, University of Seoul Secretary: Jinho Kim, Kangwon National -

List of 'CAMPUS Asia' Pilot Programs

List of ‘CAMPUS Asia’ Pilot Programs Program Provider (University) Program Name Japan China Korea Beijing-Seoul-Tokyo Dual Degree The University of Peking University Seoul National Master's Program on Tokyo University International and Public Policy Studies (BESETO DDMP) TKT CAMPUS Asia Consortium Tokyo Institute of Tsinghua University KAIST Technology Asia Business Leaders Program Hitotsubashi Peking University Seoul National (ABLP) University University Northeast Asian Consortium for National Graduate Tsinghua University KDI School of Policy Studies Institute for Policy Public Policy and Studies (GRIPS) Management Training Human Resources for Nagoya University Renmin University Sungkyunkwan the Development of an of China University Epistemic Community in Law Tsinghua University Seoul National and Political Science to Promote Shanghai Jiao Tong University the Formation of "jus commune" University in East Asia A Cooperative Asian Education Nagoya University Nanjing University POSTECH Gateway for a Sustainable Tohoku University Shanghai Jiao Tong Seoul National Society: Expanding the University University Frontiers in Science and Technology of Chemistry and Material Program for Careers on Risk Kobe University Fudan University Korea University Management Experts in East Asia Program for Core Human Okayama Jilin University Sungkyunkwan Resources Development: For the University University Achievement of the Common Good and a Re-evaluation of Classical Culture in East Asia Cooperational Graduate Kyushu University Shanghai Jiao Tong Pusan National -

Graduate School Overview

AY 2019 Graduate School Overview <Reference Only> Osaka City University Table of Contents Page History ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 1 Enrollment Quotas ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 1 Research Fields and Classes Graduate School of Business ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 2 Graduate School of Economics ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 4 Graduate School of Law ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 5 Graduate School of Literature and Human Sciences ・・・・・・・・・・・・・・・ 7 Graduate School of Science ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 12 Graduate School of Engineering ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 15 Graduate School of Medicine ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 19 Graduate School of Nursing ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 26 Graduate School of Human Life Science ・・・・・・・・・・・・・・・・・・・・・・・・・・・28 Graduate School for Creative Cities ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 31 Graduate School of Urban Management ・・・・・・・・・・・・・・・・・・・・・・・・・・・32 Degrees ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・34 Entrance Examinations ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・35 Alma Maters of Enrollees ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 40 Graduate School Exam Schedule (tentative) ・・・・・・・・・・・・・・・・・・・・・・・・・・・42 Directions ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・44 History■ History Osaka City University, the foundation of this graduate school, was established using a reform of the Japanese educational system in 1949 as an opportunity to merge the former -

Mechanical Engineering Letters Associate Editor SMM Masahiro ARAI

Mechanical Engineering Letters Associate Editor SMM Masahiro ARAI (Nagoya University), Yoshinobu SHIMAMURA (Shizuoka University), Kenji HIROHATA (Toshiba Corp.), Dai OKUMURA (Osaka University), Kohji MINOSHIMA (Osaka University), Takahiro KUBO (Toshiba Corp.), Hiroshi NOGUCHI (Kyusyu University), Katsuyoshi KONDOH (Osaka University), Yukio MIYASHITA (Nagaoka University of Technology), Kazuhiro OGAWA (Tohoku University), Hiroki AKASAKA (Tokyo Institute of Technology), Yoshiaki AKINIWA (Yokohama National University), Wataru NAKAO (Yokohama National University), Msaatake OHMIYA (Keio University), Toru IKEDA (Kagoshima University), Tadahiro SHIBUTANI (Yokohama National University), Hironori TOMYOH (Tohoku University), Seiichi HATA (Nagoya University), Susume TAKAHASHI (Nihon University), Satoshi KOBAYASHI (Tokyo Metropolitan University), Junpei SAKURAI (Nagoya University), Satoshi YONEYAMA (Aoyama Gakuin University), Osamu KUWAZURU (Fukui University), Fumio NARITA (Tohoku University), Takenobu SAKAI (Saitama University), Atsushi HOSOI (Waseda Univeristy), Yoji OKABE (The Univeristy of Tokyo), Shiro BIWA (Kyoto University), Tetsuya MATSUDA (University of Tsukuba), Yuko AONO (Tokyo Institute of Technology), Ryo MATSUMOTO (Osaka University), Takayuki TOKOROYAMA (Nagoya University), Hiroyuki Kousaka (Gifu University), Tetsuhide SHIMIZU (Tokyo Metropolitan University), Kazuhiro SUGA (Kogakuin University) TEP Fumiteru AKAMATSU (Osaka University), Shoji TSUSHIMA (Osaka University), Hidenori KOSAKA (Tokyo Institute of Technology), Naoki SHIKAZONO -

MIRAI Seminar 2018

MIRAI: Sweden-Japan Academic Consortium MIRAI Seminar 2018 “Sustainable Social System and Technology for Ageing Society” MIRAI is an academic consortium consisting of seven Swedish universities and eight Japanese universities; it was initiated based on the discussion at the "Japan-Sweden University Presidents’ Summit" held in October of 2015. To further expand and strengthen academic exchanges and research collaborations between the two countries, MIRAI holds an annual seminar, where researchers and students from the member universities meet to seek further collaborations. 2018 coincides with the 150th Anniversary of the diplomatic relations between Sweden and Japan. Commemorating this milestone, MIRAI seminar 2018 in Tokyo will invite not only top-level researchers, but also distinguished guests from the governments and funding agencies, in order to discuss opportunities to further expand collaborative research and academic exchanges between the two countries. Date: Wed, Oct 10th, 2018 –Fri, Oct 12th Venue: Tokyo 10th: Hongo Campus, Tokyo University 11th -12th Hongo Campus, Yotsuya Campus, Sophia University Waseda Campus, Waseda University Program: https://nagoyauniv.wixsite.com/mirai2018 Language: English Participants: 10th: Open to ALL(admission free) 11th -12th: Interested researchers and students are welcomed(JPY 5,000 registration fee for participants from NON-MIRAI member universities) Registration: Please sign up for the event through the following online registration website. (Registration will close on Fri, September 14th, 2018) -

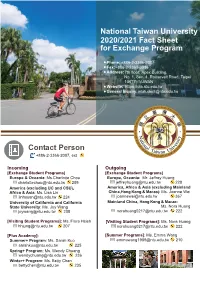

National Taiwan University 2020/2021 Fact Sheet for Exchange Program

National Taiwan University 2020/2021 Fact Sheet for Exchange Program Phone: +886-2-3366-2007 Fax:+886-2-2362-0096 Address: 7th floor, Apex Building, No. 1, Sec. 4, Roosevelt Road, Taipei 10617, TAIWAN Website: https://oia.ntu.edu.tw General Inquiry: [email protected] Contact Person +886-2-3366-2007, ext Incoming Outgoing [Exchange Student Programs] [Exchange Student Programs] Europe & Oceania: Ms.Charlotte Chou Europe, Oceania: Mr. Jeffrey Huang [email protected] 209 [email protected] 228 America (excluding UC and CSU), America, Africa & Asia (excluding Mainland Africa & Asia: Ms. Lisa Lin China,Hong Kong & Macao): Ms. Joanne Wei [email protected] 224 [email protected] 367 University of California and California Mainland China, Hong Kong & Macao: State University: Ms. Joy Wang Ms. Nora Huang [email protected] 208 [email protected] 222 [Visiting Student Programs]: Ms. Flora Hsieh [Visiting Student Programs]: Ms. Nora Huang [email protected] 207 [email protected] 222 [Plus Academy]: [Summer Programs]: Ms. Emma Wang Summer+ Program: Ms. Sarah Kuo [email protected] 210 [email protected] 225 Spring+ Program: Ms. Wendy Chuang [email protected] 236 Winter+ Program: Ms. Betty Chen [email protected] 235 Application Online student application period Term structure of the academic year First Semester Entry: March 15 to April 15 2020/2021 1st Semester (Fall) Second Semester Entry: October 01 to 31 early-September to mid-January Qualification 2020/2021 2nd Semester (Spring) Both undergraduate and graduate students mid-February to late-June Exchange quota Students with only Taiwanese nationality are The exchange quota should follow the not eligible.