Supermicro Superstorage Server SSG-6049P-E1CR36L 4U DP 36Xlff LSI 3008 RED PSU

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intelligent Systems and Platforms Transforming the Industrial Cloud Era

Intelligent Systems and Platforms Transforming the Industrial Cloud Era With innovative technologies from cloud computing (industrial server, video server), edge computing (fanless, slim & portable devices), to high performance embedded systems. Advantech transforms embedded systems into intelligent systems with smart, secure, energy-saving features, built with Industrial Cloud Services and professional Overview System Design-To-Order Services (System DTOS). Advantech’s intelligent systems are designed to target vertical markets in intelligent transportation, factory automation/machine automation, cloud infrastructure, intelligent video application. Industrial Server & Storage Industrial Cloud Intelligent Vision Systems Intelligent Video Systems Intelligent Systems Data Acquisition Modules Intelligent Transportation Systems 0-4 Star Products Intelligent Video Solution DVP-7011UHE DVP-7011MHE DVP-7017HE DVP-5311D Overview 1-ch H.264 4K HDMI 2.0 PCIe 1-ch Full HD H.264 M.2 Video 1-ch Full HD H.264 Mini PCIe Video (DVI-DVI), Control and Video Capture Card with SDK Capture Card with SDK Video Capture Card with SDK Data Transmission Extender • 1-channel 4K HDMI 2.0 video input with • 1 channel HDMI/DVI-D/DVI-A/YPbPr • 1 channel SDI channel video inputs with • Supports High Resolution 1920x1200 @ H.264 software compression channel video inputs with H.264 software H.264 software compression 60Hz WUXGA compression • 60/50 fps (NTSC/PAL) at up to • 30/25 fps (NTSC/PAL) at up to full HD • Zero pixel loss with TMDS signal correction 4096 x 2160p -

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components the FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED in THIS CHAPTER

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components THE FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED IN THIS CHAPTER: Ûß1.2 Explain motherboard components, types and features Nß Form Factor Nß ATX / BTX, Nß micro ATX Nß NLX Nß I/O interfaces Material Nß Sound Nß Video Nß USB 1.1 and 2.0 Nß Serial Nß IEEE 1394 / FireWire Nß Parallel Nß NIC Nß Modem Nß PS/2 Nß Memory slots Nß RIMM Nß DIMM Nß SODIMM CopyrightedNß SIMM Nß Processor sockets Nß Bus architecture 86498book.indb 1 7/22/09 5:37:17 AM Nß Bus slots Nß PCI Nß AGP Nß PCIe Nß AMR Nß CNR Nß PCMCIA Chipsets Nß BIOS / CMOS / Firmware Nß POST Nß CMOS battery Nß Riser card / daughterboard Nß [Additional subobjectives covered in chapter 2] Ûß1.4 Explain the purpose and characteristics of CPUs and their features Nß Identify CPU types Nß AMD Nß Intel Nß Hyper threading Nß Multi core Nß Dual core Nß Triple core Nß Quad core Nß Onchip cache Nß L1 Nß L2 Nß Speed (real vs. actual) Nß 32 bit vs. 64 bit Ûß1.5 Explain cooling methods and devices Nß Heat sinks Nß CPU and case fans 86498book.indb 2 7/22/09 5:37:18 AM Nß Liquid cooling systems Nß Thermal compound Ûß1.6 Compare and contrast memory types, characteristics and their purpose Nß Types Nß DRAM Nß SRAM Nß SDRAM Nß DDR / DDR2 / DDR3 Nß RAMBUS Nß Parity vs. Non-parity Nß ECC vs. non-ECC Nß Single sided vs. double sided Nß Single channel vs. -

SEP8253 User Manual

SEP8253 User Manual Revision 0.2 May 16, 2019 Copyright © 2019 by Trenton Systems, Inc. All rights reserved. PREFACE The information in this user’s manual has been carefully reviewed and is believed to be accurate. Trenton Systems assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. Please Note: For the most up-to-date version of this manual, please visit our website at: www.trentonsystems.com. Trenton Systems, Inc. reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software and documentation, is the property of Trenton Systems and/or its licensors, and is supplied only under a license. Any use or reproduction of this product is not allowed, except as expressly permitted by the terms of said license. IN NO EVENT WILL TRENTON SYSTEMS, INC. BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, TRENTON SYSTEMS, INC. SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA. Contact Information Trenton Systems, Inc. 1725 MacLeod Drive Lawrenceville, GA 30043 (770) 287-3100 [email protected] [email protected] [email protected] www.trentonsystems.com 2 INTRODUCTION Warranty The following is an abbreviated version of Trenton Systems’ warranty policy for High Density Embedded Computing (HDEC®) products. -

3308900 User's Manual Version 1.0 Full Size PICMG 1.0 with Socket P

3308900 User’s Manual Full Size PICMG 1.0 with Socket P Version 1.0 Copyrights This document is copyrighted and all rights are reserved. It does not allow any non authorization in copied, photocopied, translated or reproduced to any electronic or machine readable form in whole or in part without prior written consent from the manufacturer. In general, the manufacturer will not be liable for any direct, indirect, special, incidental or consequential damages arising from the use of inability to use the product or documentation, even if advised of the possibility of such damages. The manufacturer keeps the rights in the subject to change the contents of this document without prior notices in order to improve the function design, performance, quality and reliability. The author assumes no responsibility for any errors or omissions, which may appear in this document, nor does it make a commitment to update the information contained herein. Trademarks Intel is a registered trademark of Intel Corporation. Award is a registered trademark of Award Software, Inc. All other trademarks, products and or product's name mentioned herein are mentioned for identification purposes only, and may be trademarks and/or registered trademarks of their respective companies or owners. Packing List: Please check the package content before you starting using the board. Hardware: 3308900 Full-size PICMG CPU Card x 1 Cable Kit: PS/2 Keyboard & Mouse Cable x 1 HD Audio Port Cable x 1 SATA Cable x 2 DVI module with DVI Cable x 1 ( USB Cable x 2 FDD cable x 1 CPU Cooler -

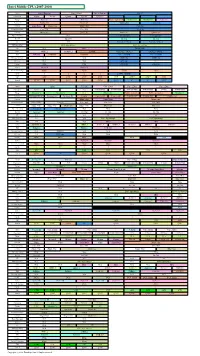

Intel Mobile CPU (2007-2010)

Intel Mobile CPU (2007-2010) Brand Core 2 Extreme Core 2 Quad Core 2 Extreme Core i7 Processor # X9000 X9100 Q9000 Q9100 QX9xxx Voltage Extreme Extreme Power optimized Standard V Standard V Extreme Codename Penryn 6M Penryn QC Auburndale Clarksfield Platform Santa Rosa Montevina Montevina Calpella Micro-architecture Core MA Core MA Nehalem # of Core Dual Core Quad Core Dual Core Quad Core Hyper-Threading N/A 2 threads/core 2 threads/core Intel 64 Intel 64 Intel 64 Intel 64 VT VT Extended VT-x/d Extended VT-x/d EIST(SpeedStep) EIST(SpeedStep) EIST(SpeedStep) IDA N/A IDA Turbo Mode Cache 6MB L2 2x3MB L2 2x6MB 512KB L2+4MB L3 1MB L2+8MB L3 FSB FSB 800 FSB1066 FSB1066 PCIe x16/DMI PCIe x16/DMI Memory interface N/A N/A DDR3 x2 DDR3 x2 GPU core N/A N/A GPU core N/A Package PGA PGA rPGA989 rPGA989 Socket Socket P Socket P Process Technology 45nm 45nm 45nm 45nm # of Die 1 2 2 2 2(CPU+GMCH) 1 TDP 44W 45W 45W 45W 35W 45W? 45W? 55W Launch Q1'08 Q2'08 Q1'09 Q3'08 Q3'08 Q3'09 09 09 Q3'09 Brand Atom Celeron Core 2 Duo Core 2 Duo Core 2 Duo Processor # N2xx 7xx T8100/8300 T9300/9500 SP9200/9400 P8400/8600 P9500 T9400/9600 Voltage Standard V Standard V ULV Standard V Power optimized Power optimized Standard V Codename Diamondville SC Pineview SC Pineview DC Penryn Penryn 3M Penryn 6M Penryn 6M Penryn 3M Penryn 6M Platform Montevina Santa Rosa Montevina Micro-architecture Silverthorne Lincroft Core MA Core MA Core MA # of Core Single Core Single Core Dual Core Single Core Dual Core Dual Core Hyper-Threading 2 threads/core 2 threads/core N/A N/A N/A Intel -

Investigations of Various HPC Benchmarks to Determine Supercomputer Performance Efficiency and Balance

Investigations of Various HPC Benchmarks to Determine Supercomputer Performance Efficiency and Balance Wilson Lisan August 24, 2018 MSc in High Performance Computing The University of Edinburgh Year of Presentation: 2018 Abstract This dissertation project is based on participation in the Student Cluster Competition (SCC) at the International Supercomputing Conference (ISC) 2018 in Frankfurt, Germany as part of a four-member Team EPCC from The University of Edinburgh. There are two main projects which are the team-based project and a personal project. The team-based project focuses on the optimisations and tweaks of the HPL, HPCG, and HPCC benchmarks to meet the competition requirements. At the competition, Team EPCC suffered with hardware issues that shaped the cluster into an asymmetrical system with mixed hardware. Unthinkable and extreme methods were carried out to tune the performance and successfully drove the cluster back to its ideal performance. The personal project focuses on testing the SCC benchmarks to evaluate the performance efficiency and system balance at several HPC systems. HPCG fraction of peak over HPL ratio was used to determine the system performance efficiency from its peak and actual performance. It was analysed through HPCC benchmark that the fraction of peak ratio could determine the memory and network balance over the processor or GPU raw performance as well as the possibility of the memory or network bottleneck part. Contents Chapter 1 Introduction .............................................................................................. -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

Modeling Many-Core Processor Interconnect Scalability for the Evolving Performance, Power and Area Relation NIVERSITEIT VAN David Smelt —U June 9, 2018 NFORMATICA I

BACHELOR INFORMATICA MSTERDAM A Modeling many-core processor interconnect scalability for the evolving performance, power and area relation NIVERSITEIT VAN David Smelt —U June 9, 2018 NFORMATICA I Supervisor(s): drs. T.R. Walstra Signed: Abstract Novel chip technologies continue to face power and thermal limits accompanied by the evolving performance, power and area relation. CPU architectures are moving towards ever-increasing core counts to sustain compute performance growth. The imminent many-core era necessitates an efficient and scalable interconnection network. This thesis elaborates on the underlying causes for compelled energy efficiency and its impacts on microarchitecture evolution. Scalability of various interconnect topologies is evaluated; pragmatically by means of x86 benchmarks and theoretically by means of synthetic traffic. Performance scalability statistics for both existing Intel x86 interconnects and alternative topologies are obtained by means of Sniper and gem5/Garnet2.0 simulations. Power and area models are obtained through McPAT for Sniper simulations and through DSENT for detailed gem5/Garnet2.0 NoC simulations. Garnet2.0 is extended for modeling of NoC power consumption and area with DSENT. For three existing Intel x86 CPU architectures, microarchitectural details pertaining to scalability and interconnects are laid out. This illustrates the evolution of Intel’s x86 CPU interconnection net- works, from bus to increasingly more scalable point-to-point interconnects. Scalability of performance, power and area in select Intel x86 processors is examined with the Sniper x86 computer architecture simulator. Interconnect scalability of various bus, ring (NoC) and mesh (NoC) topologies in the sim- ulated Haswell architecture is compared by means of Sniper’s results, which include a power and area model by McPAT. -

Unstructured Computations on Emerging Architectures

Unstructured Computations on Emerging Architectures Dissertation by Mohammed A. Al Farhan In Partial Fulfillment of the Requirements For the Degree of Doctor of Philosophy King Abdullah University of Science and Technology Thuwal, Kingdom of Saudi Arabia May 2019 2 EXAMINATION COMMITTEE PAGE The dissertation of M. A. Al Farhan is approved by the examination committee Dissertation Committee: David E. Keyes, Chair Professor, King Abdullah University of Science and Technology Edmond Chow Associate Professor, Georgia Institute of Technology Mikhail Moshkov Professor, King Abdullah University of Science and Technology Markus Hadwiger Associate Professor, King Abdullah University of Science and Technology Hakan Bagci Associate Professor, King Abdullah University of Science and Technology 3 ©May 2019 Mohammed A. Al Farhan All Rights Reserved 4 ABSTRACT Unstructured Computations on Emerging Architectures Mohammed A. Al Farhan his dissertation describes detailed performance engineering and optimization Tof an unstructured computational aerodynamics software system with irregu- lar memory accesses on various multi- and many-core emerging high performance computing scalable architectures, which are expected to be the building blocks of energy-austere exascale systems, and on which algorithmic- and architecture-oriented optimizations are essential for achieving worthy performance. We investigate several state-of-the-practice shared-memory optimization techniques applied to key kernels for the important problem class of unstructured meshes. We illustrate -

ICE�-�GM45A Duo Processor,VGA/LVDS, Gbe, SATAII, USB and Audio

Single board computer / Industrial motherboard www.ieiworld.com COM Express Basic Type 2 Module, Intel® 45nm Core™ ICE - GM45A Duo Processor,VGA/LVDS, GbE, SATAII, USB and Audio 45nm Penryn VS 65nm Merom Performance ● Intel® Core™ 2 Duo T7500 (2.2 GHz, 800 MHz FSB) w/ GME965 Chipset and 667 MHz DDR2 ● Intel® Core™ 2 Duo processor (Penryn) (2.53 GHz, 1066MHz FSB) w/ GM45 Chipset and 667 MHz DDR2 Specifications CPU 1066 DDR2 FSB 800 Socket P Intel® Core™ Duo Processor with a 1066/800MHz FSB PCIePCI-E Socket P Intel® Celeron® M Processor with a 667MHz FSB System Chipset Intel® GM45 / ICH9-M Features BIOS 1. Intel® 45nm mobile Core™ 2 Duo processor(Penryn) supported AMI BIOS 2. High performance MPEG-2 decoding, WMV9 (VC-1) and H.264 (AVC) System Memory supported Two 200-pin 800/667MHz DDR2 SO-DIMM support up to 4GB 3. DDR2 800/667Mhz dual channel SD RAM supported up to 4GB Ethernet One Intel® 82574L PCIe GbE Chipset 4. 18/24-bit dual channel LVDS, Analog CRT, HDTV supported I/O Interface 8 x USB 2.0 (to Base Board) 4 x SATAII (to Base Board) Audio Dimensions (mm) HD Audio Signal to Base Board (Audio Codec on Base Board) Expansion 1x PCIe x16 or 2 x SDVO signal to Base Board 5 x PCIe x1 signal to Base Board 4 x PCI , 32 bit / 33 MHz PCI bus to Base Board" Display Interface VGA/HDTV Integrated in Intel® GM45 Signal (to Base Board) 18/24-bit Dual channel LVDS Signal (to Base Board)" Watchdog Timer Software programmable supports 1 ~255 sec. -

ASUS Server and Workstation PRODUCT PORTFOLIO the Wall Street Journal Asia N0.1 in Quality and Services

ASUS Server and Workstation PRODUCT PORTFOLIO The Wall Street Journal Asia N0.1 in Quality and Services Over 24 years of experience building high-quality servers and workstations Received 137 benchmark world records for fastest 2P and 1P server performance* Ranked No.1 on the Green500 list of energy-efficient supercomputers in 2014 One of only two server manufactures to win a 2017 Computex Best Choice Award ASUS is a multinational company known for the world’s best motherboards, PCs, monitors, graphics cards and routers, and driven to become the most-admired innovative leading technology enterprise. With a global workforce that includes more than 5,000 R&D professionals, ASUS leads the industry through cutting-edge design and innovations made to create the most ubiquitous, intelligent, heartfelt and joyful smart life for everyone. Inspired by the In Search of Incredible brand spirit, ASUS won more than 11 prestigious awards every day in 2018 and ranked as one of Forbes’ Global 2000 Top Regarded Companies, Thomson Reuters’ Top 100 Global Tech Leaders and Fortune’s World’s Most Admired Companies. In ASU t rodu S Serve c tio n r 01 Green ASUS 02 New 2nd Generation Intel® Xeon® Latest Intel Optane™ DC persistent Scalable processors memory - 1.33X average performance improvement in Technology – delivers an unique combination of power consumption and clock speed affordable large capacity and persistence - Enhanced deep learning capabilities (non-volatility) - Support up to 6 channel DDR4 2933 2n d G ener Exclusive Thermal Rader ASUS Control Center ation Intel® A SUS Ser - Automatically reduce consumption of overall Server remote management to safeguard all of Xeo ver fan capacity your devices s and n® Sca - Effectively enhance system reliability and thermal efficiency Workstationswit lable processor h s 05 fo r * * Pr ofess io *Selected Models na l Content Creators 06 TM Platform Solutions AMD EPYC 07 67 Benchmark world Records No.1 ASUS Server and Workstation January 31, 2019 08 OCP Mezz. -

A Case for Packageless Processors

A Case for Packageless Processors Saptadeep Pal∗, Daniel Petrisko†, Adeel A. Bajwa∗, Puneet Gupta∗, Subramanian S. Iyer∗, and Rakesh Kumar† ∗Department of Electrical and Computer Engineering, University of California, Los Angeles †Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign fsaptadeep,abajwa,s.s.iyer,[email protected], fpetrisk2,[email protected] Abstract—Demand for increasing performance is far out- significantly limit the number of supportable IOs in the pacing the capability of traditional methods for performance processor due to the large size and pitch of the package- scaling. Disruptive solutions are needed to advance beyond to-board connection relative to the size and pitch of on- incremental improvements. Traditionally, processors reside inside packages to enable PCB-based integration. We argue chip interconnects (∼10X and not scaling well). In addition, that packages reduce the potential memory bandwidth of a the packages significantly increase the interconnect distance processor by at least one order of magnitude, allowable thermal between the processor die and other dies. Eliminating the design power (TDP) by up to 70%, and area efficiency by package, therefore, has the potential to increase bandwidth a factor of 5 to 18. Further, silicon chips have scaled well by at least an order of magnitude(Section II). Similarly, while packages have not. We propose packageless processors - processors where packages have been removed and dies processor packages are much bigger than the processor itself directly mounted on a silicon board using a novel integra- (5 to 18 times bigger). Removing the processor package tion technology, Silicon Interconnection Fabric (Si-IF).