A Report on Semiconductor Foundry Access by US Academics (Discussion Held at a Meeting Virtually Held at the National Science Foundation on Dec 16, 2020)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Section 10 Flash Technology

10 FLASH TECHNOLOGY Overview Flash memory technology is a mix of EPROM and EEPROM technologies. The term “flash” was chosen because a large chunk of memory could be erased at one time. The name, therefore, distinguishes flash devices from EEPROMs, where each byte is erased individually. Flash memory technology is today a mature technology. Flash memory is a strong com- petitor to other memories such as EPROMs, EEPROMs, and to some DRAM applications. Figure 10-1 shows the density comparison of a flash versus other memories. 64M 16M 4M DRAM/EPROM 1M SRAM/EEPROM Density 256K Flash 64K 1980 1982 1984 1986 1988 1990 1992 1994 1996 Year Source: Intel/ICE, "Memory 1996" 18613A Figure 10-1. Flash Density Versus Other Memory How the Device Works The elementary flash cell consists of one transistor with a floating gate, similar to an EPROM cell. However, technology and geometry differences between flash devices and EPROMs exist. In particular, the gate oxide between the silicon and the floating gate is thinner for flash technology. It is similar to the tunnel oxide of an EEPROM. Source and INTEGRATED CIRCUIT ENGINEERING CORPORATION 10-1 Flash Technology drain diffusions are also different. Figure 10-2 shows a comparison between a flash cell and an EPROM cell with the same technology complexity. Due to thinner gate oxide, the flash device will be more difficult to process. CMOS Flash Cell CMOS EPROM Cell Mag. 10,000x Mag. 10,000x Flash Memory Cell – Larger transistor – Thinner floating gate – Thinner oxide (100-200Å) Photos by ICE 17561A Figure 10-2. -

The Impacts of Technological Invention on Economic Growth – a Review of the Literature Andrew Reamer1 February 28, 2014

THE GEORGE WASHINGTON INSTITUTE OF PUBLIC POLICY The Impacts of Technological Invention on Economic Growth – A Review of the Literature Andrew Reamer1 February 28, 2014 I. Introduction In their recently published book, The Second Machine Age, Erik Brynjolfsson and Andrew McAfee rely on economist Paul Krugman to explain the connection between invention and growth: Paul Krugman speaks for many, if not most, economists when he says, “Productivity isn’t everything, but in the long run it’s almost everything.” Why? Because, he explains, “A country’s ability to improve its standard of living over time depends almost entirely on its ability to raise its output per worker”—in other words, the number of hours of labor it takes to produce everything, from automobiles to zippers, that we produce. Most countries don’t have extensive mineral wealth or oil reserves, and thus can’t get rich by exporting them. So the only viable way for societies to become wealthier—to improve the standard of living available to its people—is for their companies and workers to keep getting more output from the same number of inputs, in other words more goods and services from the same number of people. Innovation is how this productivity growth happens.2 For decades, economists and economic historians have sought to improve their understanding of the role of technological invention in economic growth. As in many fields of inventive endeavor, their efforts required time to develop and mature. In the last five years, these efforts have reached a point where they are generating robust, substantive, and intellectually interesting findings, to the benefit of those interested in promoting growth-enhancing invention in the U.S. -

Timeline of the Semiconductor Industry in South Portland

Timeline of the Semiconductor Industry in South Portland Note: Thank you to Kathy DiPhilippo, Executive Director/Curator of the South Portland Historical Society and Judith Borelli, Governmental Relations of Texas Inc. for providing some of the information for this timeline below. Fairchild Semiconductor 1962 Fairchild Semiconductor (a subsidiary of Fairchild Camera and Instrument Corp.) opened in the former Boland's auto building (present day Back in Motion) at 185 Ocean Street in June of 1962. They were there only temporarily, as the Western Avenue building was still being constructed. 1963 Fairchild Semiconductor moves to Western Avenue in February 1963. 1979 Fairchild Camera and Instrument Corp. is acquired/merged with Schlumberger, Ltd. (New York) for $363 million. 1987 Schlumberger, Ltd. sells its Fairchild Semiconductor Corp. subsidiary to National Semiconductor Corp. for $122 million. 1997 National Semiconductor sells the majority ownership interest in Fairchild Semiconductor to an investment group (made up of Fairchild managers, including Kirk Pond, and Citcorp Venture Capital Ltd.) for $550 million. Added Corporate Campus on Running Hill Road. 1999 In an initial public offering in August 1999, Fairchild Semiconductor International, Inc. becomes a publicly traded corporation on the New York Stock Exchange. 2016 Fairchild Semiconductor International, Inc. is acquired by ON Semiconductor for $2.4 billion. National Semiconductor 1987 National Semiconductor acquires Fairchild Semiconductor Corp. from Schlumberger, Ltd. for $122 million. 1995 National Semiconductor breaks ground on new 200mm factory in December 1995. 1996 National Semiconductor announces plans for a $600 million expansion of its facilities in South Portland; construction of a new wafer fabrication plant begins. 1997 Plant construction for 200mm factory completed and production starts. -

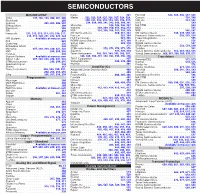

SEMICONDUCTORS MCU/MPU/DSP Kionix

SEMICONDUCTORS MCU/MPU/DSP Kionix . 321 Fairchild . 534 . , 535, 536, 537, 538 Atmel . 197, 198, 199, 200, 201, 202 Maxim . 322 . , 323, 324, 325, 326, 327, 328, 329, Genesic . 539. , 540 Blackhawk . 203 . 330, 331, 332, 333, 334, 335, 336, 337, Infineon . 541, 542 Cypress . 204 . , 205, 206, 207 . 338, 339, 340, 341, 342, 343, 380, 381 IXYS . 543. Energy Micro . 208 Microchip . 344, 345, 346, 347 MA-COM . 544 . Elprotronic . 209 National . 348 . , 349, 350, 351, 352, 353 MCC . 545. FDI . 210 . NXP . 354. , 355, 356, 357, 358, 359 NXP . .546 . , 547 Freescale . 211, 212, 213, 214, 215, 216, 217, ON Semiconductor . .360, 361, 362 ON Semiconductor . 548, 549, 550, 551 . 218, 219, 220, 221, 222, 223, 224 Pericom . 363. , 364 Panasonic Semiconductor . .552 . , 553, 554 IAR Systems . .Available . at mouser.com PLX Technology . .365 . , 366 Power Integrations . 555 Keil . 225 ROHM Semiconductor . 367, 368 Rectron . 556 Code Red . 226. Silicon Labs . 369 . , 370 ROHM Semiconductor . 557 Embedded Artists . 226 . SMSC . 371 . STMicroelectronics . .558, 559, 560 Microchip . 227, 228, 229, 230, 231, 232 STMicroelectronics . 372, 373, 374, 375, 376 Toshiba . 561 NXP . 233 . , 234, 235 Supertex . .377 . , 378, 379 Vishay General Semiconductor .562, 563, 564, 565 Parallax . 236 Texas Instruments . 382, 383, 384, 385, 386, 387, Vishay Semiconductor . 566, 567, 568, 569, 570, 571 Signum Systems . Available at mouser.com . 388, 389, 390, 391, 392, 393, 394, 395, 396 Transistors Silicon Labs . .237 . , 238, 239, 240, 241, 242 THAT Corporation . 397 . Renesas/CEL . 572. , 573 STMicroelectronics . .243, 244, 245 Vishay/Siliconix . .398, 399, 400 Central . .574, 575 Spectrum Digital . -

Final Report of the NASA Technology Readiness Assessment (TRA) Study Team

NASA Technology Readiness Assessment (TRA) Study Team Final Report of the NASA Technology Readiness Assessment (TRA) Study Team March 2016 Authors: HQ Office of the Chief Engineer/Steven Hirshorn and HQ Office of the Chief Technologist/Sharon Jefferies Contributors: ARC/Kenny Vassigh, AFRC/David Voracek, GSFC/Michael Johnson, GSFC/Deborah Amato, JPL/Margaret (Peg) Frerking, JPL/Pat Beauchamp, JSC/Ronnie Clayton, KSC/Doug Willard, LaRC/Jim Dempsey, LaRC/Bill Luck, MSFC/Mike Tinker, SSC/Curtis (Duane) Armstrong NASA Technology Readiness Assessment (TRA) Study Team Acknowledgements The authors of this report wish to acknowledge and thank the members of the Technology Readiness Assessment (TRA) team for their participation, dedication, effort, hard work and brilliant insights throughout the course of this study. We deeply appreciate their willingness to contribute their knowledge, experience, and time, which was the fundamental attribute leading to the success of this study. You all have been brilliant!! Disclaimer The purpose of this report is to document the observations, findings, and recommendations of the NASA-wide Technology Readiness Assessment (TRA) team that conducted its work in 2014. While suggested guidance and recommendations are included, the contents of this report should not be construed as Agency-accepted practice. Establishment of an Agency-accepted practice on TRA may eventually stem from the report’s contents, but at this time the report simply constitutes an outbriefing of the team’s activities. 2 of 63 NASA Technology -

Mckinsey on Semiconductors

McKinsey on Semiconductors Creating value, pursuing innovation, and optimizing operations Number 7, October 2019 McKinsey on Semiconductors is Editorial Board: McKinsey Practice Publications written by experts and practitioners Ondrej Burkacky, Peter Kenevan, in McKinsey & Company’s Abhijit Mahindroo Editor in Chief: Semiconductors Practice along with Lucia Rahilly other McKinsey colleagues. Editor: Eileen Hannigan Executive Editors: To send comments or request Art Direction and Design: Michael T. Borruso, copies, email us: Leff Communications Bill Javetski, McKinsey_on_ Semiconductors@ Mark Staples McKinsey.com. Data Visualization: Richard Johnson, Copyright © 2019 McKinsey & Cover image: Jonathon Rivait Company. All rights reserved. © scanrail/Getty Images Managing Editors: This publication is not intended to Heather Byer, Venetia Simcock be used as the basis for trading in the shares of any company or for Editorial Production: undertaking any other complex or Elizabeth Brown, Roger Draper, significant financial transaction Gwyn Herbein, Pamela Norton, without consulting appropriate Katya Petriwsky, Charmaine Rice, professional advisers. John C. Sanchez, Dana Sand, Sneha Vats, Pooja Yadav, Belinda Yu No part of this publication may be copied or redistributed in any form without the prior written consent of McKinsey & Company. Table of contents What’s next for semiconductor How will changes in the 3 profits and value creation? 47 automotive-component Semiconductor profits have been market affect semiconductor strong over the past few years. companies? Could recent changes within the The rise of domain control units industry stall their progress? (DCUs) will open new opportunities for semiconductor companies. Artificial-intelligence hardware: Right product, right time, 16 New opportunities for 50 right location: Quantifying the semiconductor companies semiconductor supply chain Artificial intelligence is opening Problems along the the best opportunities for semiconductor supply chain semiconductor companies in are difficult to diagnose. -

Needham's Semiconductor Expertise What Does The

The Growth Factor - Commentary by John Barr, [email protected] June 23, 2021 - Vol. 32 The Opportunity We See in Semiconductor Manufacturing (6 minute read) 2020 brought an unprecedented economic shutdown. The pandemic accelerated trends that we have been focused on for a long me; we call this the Great Digital and Life Sciences Acceleration. I would like to zero in on the opportunities in semiconductor manufacturing. I’ve long felt the semiconductor industry has moved beyond a cyclical, PC-driven industry to one of strategic importance. The confluence of manufacturing semiconductors for automotive, data center, machine learning, and remote work electronic systems; remaking the supply chain, and securing supplies for geopolitical needs have created a positive scenario for semiconductor manufacturing technology companies. Needham's Semiconductor Expertise Needham Funds have been owners of semiconductor manufacturing companies since our start in 1996. Needham Funds are an affiliate of Needham & Company, which has completed over 580 underwritings and M&A transactions for semiconductor companies since 1985. Addionally, prior to my Wall Street career, I spent 12 years in sales and markeng for Electronic Design Automaon companies, selling to semiconductor and electronic systems companies. I also spent 8 years as a sell-side senior research analyst following semiconductor design and technical soware companies. I served on the board of directors of venture capital-backed Coventor, Inc., which provided simulaon and modeling soluons for semiconductor process technology and was sold to Lam Research, Inc. in 2017. What Does the Opportunity in Semiconductor Manufacturing Mean for Needham Funds? Growth in advanced semiconductor manufacturing has been a dominant investment theme for Needham Funds for over 10 years. -

A Study on the Deduction and Diffusion of Promising Artificial

sustainability Article A Study on the Deduction and Diffusion of Promising Artificial Intelligence Technology for Sustainable Industrial Development Hong Joo Lee * and Hoyeon Oh Department of Industrial and Management, Kyonggi University, Suwon 443760, Gyeonggi, Korea; [email protected] * Correspondence: [email protected] Received: 14 May 2020; Accepted: 8 July 2020; Published: 13 July 2020 Abstract: Based on the rapid development of Information and Communication Technology (ICT), all industries are preparing for a paradigm shift as a result of the Fourth Industrial Revolution. Therefore, it is necessary to study the importance and diffusion of technology and, through this, the development and direction of core technologies. Leading countries such as the United States and China are focusing on artificial intelligence (AI)’s great potential and are working to establish a strategy to preempt the continued superiority of national competitiveness through AI technology. This is because artificial intelligence technology can be applied to all industries, and it is expected to change the industrial structure and create various business models. This study analyzed the leading artificial intelligence technology to strengthen the market’s environment and industry competitiveness. We then analyzed the lifecycle of the technology and evaluated the direction of sustainable development in industry. This study collected and studied patents in the field of artificial intelligence from the US Patent Office, where technology-related patents are concentrated. All patents registered as artificial intelligence technology were analyzed by text mining, using the abstracts of each patent. The topic was extracted through topic modeling and defined as a detailed technique. Promising/mature skills were analyzed through a regression analysis of the extracted topics. -

Why Technology Is the Strategic Issue of Our Time

Why technology is the strategic issue of our time And what CEOs and their leadership teams should do about it Today’s fastest-growing companies have one thing in common—they harness technology and innovation to their advantage. Cloud, artificial intelligence (AI), machine learning (ML), and faster connectivity fuel business model disruption and industry transformation. Yet for every shining star, we see a struggling one. Newspapers. Travel agencies. Taxis. Film photography. Landline phone service. Cable television. Video rentals. They too invested in technology. What did they miss? Winning in today’s market requires teams to go beyond using technology for the core of their businesses. It requires chief executive officers (CEOs) and their teams to actively and aggressively build new businesses, business models, products, and services using these powerful, rapidly maturing technologies, A broad set of robust and rapidly and it requires breaking through five myths that permeate management thinking in this space. maturing technologies—from cloud to AI to 5G—is rapidly and fundamentally Believing in a single myth impedes an organization’s prospects for growth and breakthrough thinking. Buying into multiple of these changing what is possible for companies myths can erase those opportunities altogether. and how they compete. Five myths that permeate management thinking 1 2 3 4 5 Technology is the Technology is Technology > strategy All tech companies should Newcomers will responsibility of Chief a silver bullet act like Silicon Valley disrupt -

The New Plastics Economy Rethinking the Future of Plastics

THE NEW PLASTICS ECONOMY • • • 1 The New Plastics Economy Rethinking the future of plastics THE NEW PLASTICS ECONOMY RETHINKING THE FUTURE OF PLASTICS 2 • • • THE NEW PLASTICS ECONOMY THE NEW PLASTICS ECONOMY • • • 3 CONTENTS Preface 4 Foreword 5 In support of the New Plastics Economy 6 Project MainStream 8 Disclaimer 9 Acknowledgements 10 Global partners of the Ellen MacArthur Foundation 14 EXECUTIVE SUMMARY 15 PART I SUMMARY OF FINDINGS AND CONCLUSIONS 22 1 The case for rethinking plastics, starting with packaging 24 2 The New Plastics Economy: Capturing the opportunity 31 3 The New Plastics Economy demands a new approach 39 PART II CREATING AN EFFECTIVE AFTER-USE PLASTICS ECONOMY 44 4 Recycling: Drastically increasing economics, uptake and quality through compounding and mutually reinforcing actions 46 5 Reuse: Unlocking material savings and beyond 62 6 Compostable packaging: Returning nutrients to the soil for targeted packaging applications 68 PART III DRASTICALLY REDUCING LEAKAGE OF PLASTICS INTO NATURAL SYSTEMS AND MINIMISING OTHER EXTERNALITIES 74 7 Drastically reducing leakage into natural systems and associated negative impacts 76 8 Substances of concern: Capturing value with materials that are safe in all product phases 79 PART IV DECOUPLING PLASTICS FROM FOSSIL FEEDSTOCKS 86 9 Dematerialisation: Doing more with less plastic 88 10 Renewably sourced plastics: Decoupling plastics production from fossil feedstocks 92 Appendix 97 Appendix A. Global material flow analysis: definitions and sources 98 Appendix B. Biodegradation 100 Appendix C. Anaerobic digestion 101 Glossary 102 List of Figures and Boxes 105 Endnotes 106 About the Ellen MacArthur Foundation 117 4 • • • THE NEW PLASTICS ECONOMY PREFACE The circular economy is gaining growing attention as a potential way for our society to increase prosperity, while reducing demands on finite raw materials and minimising negative externalities. -

Texas Instruments Incorporated

A Progressive Digital Media business COMPANY PROFILE Texas Instruments Incorporated REFERENCE CODE: AFDA1C52-BBF2-41FA-A70D-DE34086443A9 PUBLICATION DATE: 20 Oct 2017 www.marketline.com COPYRIGHT MARKETLINE. THIS CONTENT IS A LICENSED PRODUCT AND IS NOT TO BE PHOTOCOPIED OR DISTRIBUTED Texas Instruments Incorporated TABLE OF CONTENTS TABLE OF CONTENTS Company Overview ........................................................................................................3 Key Facts.........................................................................................................................3 SWOT Analysis ...............................................................................................................4 Texas Instruments Incorporated Page 2 © MarketLine Texas Instruments Incorporated Company Overview Company Overview COMPANY OVERVIEW Texas Instruments Incorporated (Texas Instruments, TI or 'the company') is a designer and producer of semiconductors. The company primarily provides analog integrated circuits (ICs) and embedded processors. TI sells its products to original equipment manufacturers (OEMs), original design manufacturers (ODMs), contract manufacturers and distributors through direct sales force and third-party sales representatives. It has business presence across the Americas, Asia, Europe, the Middle East and Africa. The company is headquartered in Dallas, Texas, the US. The company reported revenues of (US Dollars) US$13,370 million for the fiscal year ended December 2016 (FY2016), an increase of 2.8% -

Apple Inc.: Managing a Global Supply Chain1

For the exclusive use of T. Ausby, 2015. W14161 APPLE INC.: MANAGING A GLOBAL SUPPLY CHAIN1 Ken Mark wrote this case under the supervision of Professor P. Fraser Johnson solely to provide material for class discussion. The authors do not intend to illustrate either effective or ineffective handling of a managerial situation. The authors may have disguised certain names and other identifying information to protect confidentiality. This publication may not be transmitted, photocopied, digitized or otherwise reproduced in any form or by any means without the permission of the copyright holder. Reproduction of this material is not covered under authorization by any reproduction rights organization. To order copies or request permission to reproduce materials, contact Ivey Publishing, Ivey Business School, Western University, London, Ontario, Canada, N6G 0N1; (t) 519.661.3208; (e) [email protected]; www.iveycases.com. Copyright © 2014, Richard Ivey School of Business Foundation Version: 2014-06-12 INTRODUCTION Jessica Grant was an analyst with BXE Capital (BXE), a money management firm based in Toronto.2 It was February 28, 2014, and Grant was discussing her U.S. equity mandate with BXE’s vice president, Phillip Duchene. Both Grant and Duchene were trying to identify what changes, if any, they should make to BXE’s portfolio. “Apple is investing in its next generation of products, potentially the first new major product lines since Tim Cook took over from Steve Jobs,” she said. Apple Inc., the world’s largest company by market capitalization, had introduced a series of consumer products during the past dozen years that had transformed it into the industry leader in consumer devices.