Wide Frequency Range Superheterodyne Receiver Design and Simulation

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

US2959674.Pdf

Nov. 8, 1960 T. R. O "MEARA 2,959,674 GAIN CONTROL FOR PHASE AND GAIN MATCHED MULTI-CHANNEL RADIO RECEIVERS Filed July 2, 1957 2. Sheets-Sheet 2 PETARD CONVERTER TUBE Ë????Q. F SiGNAL OUTPUT OSC. S. G. INPUT INVENTOR. 77/OMAS A. O’MEAAA AT 7OAPWA 3 2,959,674 United States Patent Office Patented Nov. 8, 1960 1. 2 linear type. By a linear type frequency changer is meant a device with output current or voltage which is a linear 2.959,674 function of either the RF input signal or local oscillator GAIN CONTROL FOR PHASE AND GAN signal alone and with a conversion transconductance MATCHED MULT-CHANNELRADIO RE. 5 characteristic which varies linearly with the magnitude of CEIVERS the voltage at the local oscillator input to the device. Thomas R. O'Meara, Los Angeles, Calif., assignor, by This means that, if instead of being an alternating voltage, meSne assignments, to the United States of America as the RF signal input to the device were maintained at a represented by the Secretary of the Navy constant D.C. voltage and the oscillator signal were re 0. placed by a D.C. voltage excursion, then a plot of the Filed July 2, 1957, Ser. No. 669,691 output current or voltage of the device versus the local oscillator signal voltage would be a straight line. Simi 3 Claims. (Cl. 250-20) larly, if the local oscillator signal voltage input to the device were kept at a constant D.C. value, instead of This invention relates to a gain control for electronic 5 being an A.C. -

Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10

EE447 Lecture 6 Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10 HW7;5-4,5-7,5-13a-d,5-23,5-31 Due next Monday, 29th 1 Figure 4–29 Superheterodyne receiver. m(t) 2 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 1 EE447 Lecture 6 Synchronous Demodulation s(t) LPF m(t) 2Cos(2πfct) •Only method for DSB-SC, USB-SC, LSB-SC •AM with carrier •Envelope Detection – Input SNR >~10 dB required •Synchronous Detection – (no threshold effect) •Note the 2 on the LO normalizes the output amplitude 3 Figure 4–24 PLL used for coherent detection of AM. 4 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 2 EE447 Lecture 6 Envelope Detector C • Ac • (1+ a • m(t)) Where C is a constant C • Ac • a • m(t)) 5 Envelope Detector Distortion Hi Frequency m(t) Slope overload IF Frequency Present in Output signal 6 3 EE447 Lecture 6 Superheterodyne Receiver EE445-09 7 8 4 EE447 Lecture 6 9 Super-Heterodyne AM Receiver 10 5 EE447 Lecture 6 Super-Heterodyne AM Receiver 11 RF Filter • Provides Image Rejection fimage=fLO+fif • Reduces amplitude of interfering signals far from the carrier frequency • Reduces the amount of LO signal that radiates from the Antenna stop 2/22 12 6 EE447 Lecture 6 Figure 4–30 Spectra of signals and transfer function of an RF amplifier in a superheterodyne receiver. 13 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. -

A Wide-Band RF Front-End with Linear Active Notch Filter for Mobile

RMO2B-5 A Wide-Band RF Front-End with Linear Active Notch Filter for Mobile TV Applications Seung Hwan Jung, Kang Hyuk Lee, Young Jae Lee1, Hyun Kyu Yu1, Yun Seong Eo Radio Frequency Circuits and Systems Laboratory Kwangwoon University, Seoul Korea 1Electronics and Telecommunications Research Institute (ETRI), Daejeon Korea Abstract — This paper presents a wide-band RF front-end inductor has a poor linearity and cannot withstand the with linear active notch filter covering both T-DMB and strong GSM interferer even with the external GSM band DVB-H. A single to differential converter with the low amplitude/phase error and 6dB step RF VGA using the rejection SAW filter. To overcome these drawbacks, a capacitor are implemented. Also, highly linear and Q- newly proposed linear Q-enhanced active notch filter is enhanced tunable active inductor is proposed. The linear presented in this paper. In order to obtain a high linearity active notch filter rejects GSM band up to 23dB and achieves of the active inductor, the MGTR (Multiple Gated 20dB linearity improvement. The RF front-end is fabricated Transistor) topology is adopted to the gyrator’s trans- on 90nm CMOS technology and consumes 29.7mW. conductor cell and push-pull type negative resistor circuit is also used, which maintain the constant inductance and Index Terms — Wide-band LNA, Single to differential converter, High linear active inductor, Notch filter, CMOS. quality factor in spite of very strong GSM input interferer. I. INTRODUCTION II. THE PROPOSED ARCHITECTURE Nowadays, the mobile TV markets such as Terrestrial- Fig. 1 illustrates the proposed wide-band RF front-end Digital Multimedia Broadcasting (T-DMB) in Korea and with linear active notch filter. -

Suitability of a Commercial Software Defined Radio System for Passive Coherent Location

Suitability of a Commercial Software Defined Radio System for Passive Coherent Location Aadil Volkwin A dissertation submitted to the Department of Electrical Engineering, University of Cape Town, in fulfilment of the requirements for the degree of Master of Science in Engineering. Cape Town, May 2008 Dedicated to: My Parents, my Sister and my Wife. 2 Declaration I declare that this work done is my own, unaided work. This dissertation is being submitted to the Department of Electrical Engineering, University of Cape Town, in fulfilment of the requirements for the degree of Master of Science in Engineering. It has not been submitted for any degree or examination in any other university. ................................................................................ Signature of Author Cape Town 2008 3 Abstract This dissertation provides a comprehensive discussion around bistatic radar with specific reference to PCL, highlighting existing literature and work, examining the various performance metrics. In particular the performance of commercial FM radio broadcasts as the radar waveform is examined by implementation of the ambiguity function. The FM signals show desirable characteristics in the context of our application, the average range resolution obtained is 5.98km, with range and doppler peak sidelobe levels measured at -25.98dB and -33.14dB respectively. Furthermore, the SDR paradigm and technology is examined, with discussion around the design considerations. The USRP, the TVRx daughterboard and GNURadio are examined further as a potential receiver and development environment, in this light. The system meets the low cost ambitions costing just over US$1000.00 for the USRP motherboard and a single daughterboard. Furthermore it performs well, displaying desirable characteristics, The receiver's frontend provides a bandwidth of 6MHz and a tunable range between 50MHz and 800MHz, with a tuning step size as low as 31.25kHz. -

Design of Reconfigurable Radio Front-Ends

Design of Reconfigurable Radio Front-Ends Xiao Xiao Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2018-142 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-142.html December 1, 2018 Copyright © 2018, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Design of Reconfigurable Radio Front-Ends by Xiao Xiao A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Borivoje Nikolic, Chair Professor Ali Niknejad Professor Paul Wright Spring 2016 Design of Reconfigurable Radio Front-Ends Copyright 2016 by Xiao Xiao 1 Abstract Design of Reconfigurable Radio Front-Ends by Xiao Xiao Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Borivoje Nikolic, Chair Modern and future mobile devices must support increasingly more wireless standards and bands. Currently, multi-band coexistence is enabled by a network of discrete, off-chip com- ponents that are bulky, expensive, and narrowband. As transceivers are required to accom- modate an increasing number of wireless bands, the required number of discrete components increases accordingly, resulting in greater bill of materials (BoM) cost and front-end module (FEM) area. -

Front-End Receiver: Recent and Emerging Trend Ulrich L

Front-End Receiver: Recent and Emerging Trend Ulrich L. Rohde Ajay K. Poddar Enrico Rubiola Marius A. Silaghi BTU Cottbus 03046 Germany Synergy Microwave NJ USA FEMTO-ST Inst. Besancon France University of Oradea, Romania Abstract—This paper describes the recent trend of front-end receiver systems for the application in radio monitoring. The 650 MHz to 1300 MHz receiver implementation is optimized for applications such as 20 MHz to 650 MHz hunting and detecting unknown signals, identifying interference, Vin =−117 dBm (0.3 μV) ≥10 dB Vin=−47 dBm (1 mV) ≥50 dB spectrum monitoring and clearance, and signal search over wide LSB/USB, IF bandwidth 500 frequency ranges, producing signal content and direction finding Hz, of identified signals. Δf=500 Hz 0.5 MHz to 20 MHz, ≥10 dB Keywords—Receivers, Real time FFT Processing Vin=0.4μV 20 to 30 MHz, Vin= 0.5 μV ≥10 dB I. INTRODUCTION LSB/USB, IF bandwidth The emerging security threats demand an intensive data 2.5kHz, Δf=1kHz gathering for fiber or radio communication [1]. Besides the 0.5 MHz to 20 MHz, ≥10 dB fiber technology, there are varieties of wireless activities, Vin=0.6μV which are typically analyzed by off the air monitoring [2]-[9]. 20 to 30 MHz, Vin= 0.7 μV ≥10 dB The spectral density of signals these days is very high and Vin= 100 μV ≥46 dB therefore such monitoring receivers require high performance. AM, IF Bandwidth 2.5kHz, The technique in designing such receivers is a composition of fmod=1 kHz, m=0.5 0.5 MHz to 20 MHz, ≥10 dB microwave engineering of the building blocks preamplifier, Vin=1μV mixer, synthesizer and necessary filters, this paper describes 20 to 30 MHz, Vin= 1.2 μV ≥10 dB critical aspects of important building blocks of radio Crossmodulation interfering monitoring receives [10]-[20]. -

Master's Thesis

Eindhoven University of Technology MASTER Mapping a China Digital Radio (CDR) receiver on a software-defined-radio platform Cheng, Y. Award date: 2017 Link to publication Disclaimer This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration. General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study or research. • You may not further distribute the material or use it for any profit-making activity or commercial gain Department of Mathematics and Computer Science Algorithm & Software Innovation Mapping a China Digital Radio (CDR) receiver on a Software-Defined-Radio platform Master Thesis Yan Cheng Supervisors: prof.dr.ir.C.H.(Kees) van Berkel Dr.Hong Li Eindhoven, August 2017 Abstract With the launch of the China Digital Radio (CDR) standard in hundreds of cities in China, CDR radio receiver chips are required in market. To explore fast and efficient embedded Software- Defined-Radio (SDR) CDR receiver design and realization, this thesis project used Data-Flow (DF) modeling to study architectural options of a CDR receiver design for an existing NXP SDR chip. -

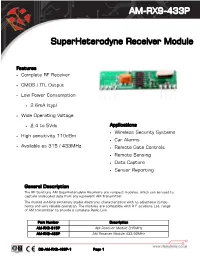

AM-RX9-433P Superheterodyne Receiver Module

AM-RX9-433P SuperHeterodyne Receiver Module Features Complete RF Receiver CMOS / TTL Output Low Power Consumption 2.6mA (typ) Wide Operating Voltage 2.4 to 5Vdc Applications Wireless Security Systems High sensitivity 110dBm Car Alarms Available as 315 / 433MHz Remote Gate Controls Remote Sensing Data Capture Sensor Reporting General Description The RF Solutions AM Superheterodyne Receivers are compact modules, which can be used to capture undecoded data from any equivalent AM Transmitter The module exhibits extremely stable electronic characteristics with no adjustable compo- nents and very reliable operation. The modules are compatible with R F solutions Ltd. range of AM transmitter to provide a complete Radio Link. Part Number Description AM-RX9-315P AM Receiver Module 315MHz AM-RX9-433P AM Receiver Module 433.92MHz DS-AM-RX9-433P-1 Page 1 AM-RX9-433P Mechanical Data Pin Decriptions Pin Description 1 Antenna In 2, 3, 8 Ground 4, 5 Supply voltage 6,7 Data Output Electrical Characteristics Ambient temp = 25°C unless otherwise stated. Characteristic Min Typical Max Dimensions Supply Voltage 2.4 5 5.5 Vdc Supply Current 2.6 mA RF Sensitivity (Vcc=5V, 1Kbps AM 99% -109 dBm @433MHz Square wave modulation) 315 Working Frequency MHz 433.92 High Level Output 0.7Vcc V Low Level Output 0.3Vcc V IF Bandwidth 280 KHz Data Rate 1 10 Kbps DS-AM-RX9-433P-1 Page 2 AM-RX9-433P Typical Application Vcc 1K 15K 13 14 4 Sleep Vcc 17 RX3 Receiver L Vcc OP1 O/P 1 12 Option 1 2 3 7 11 13 15 Status LKIN 18 LED Link OP2 O/P 2 M 1 OP3 O/P 3 2 OP4 O/P 4 10 3 LRN LB Transmitter RF600D Low Battery 1K 11 Serial Data Learn SD1 Output Switch 9 7 IN ECLK GND 5 22K RF Meter RF Multi Meter is a versatile handheld test meter checking Radio signal strength or interference in a given area. -

Superheterodyne Receiver

Superheterodyne Receiver The received RF-signals must transformed in a videosignal to get the wanted informations from the echoes. This transformation is made by a super heterodyne receiver. The main components of the typical superheterodyne receiver are shown on the following picture: Figure 1: Block diagram of a Superheterodyne The superheterodyne receiver changes the rf frequency into an easier to process lower IF- frequency. This IF- frequency will be amplified and demodulated to get a videosignal. The Figure shows a block diagram of a typical superheterodyne receiver. The RF-carrier comes in from the antenna and is applied to a filter. The output of the filter are only the frequencies of the desired frequency-band. These frequencies are applied to the mixer stage. The mixer also receives an input from the local oscillator. These two signals are beat together to obtain the IF through the process of heterodyning. There is a fixed difference in frequency between the local oscillator and the rf-signal at all times by tuning the local oscillator. This difference in frequency is the IF. this fixed difference an ganged tuning ensures a constant IF over the frequency range of the receiver. The IF-carrier is applied to the IF-amplifier. The amplified IF is then sent to the detector. The output of the detector is the video component of the input signal. Image-frequency Filter A low-noise RF amplifier stage ahead of the converter stage provides enough selectivity to reduce the image-frequency response by rejecting these unwanted signals and adds to the sensitivity of the receiver. -

An Open Rf-Digital Interface for Software-Defined Radios

.................................................................................................................................................................................................................. AN OPEN RF-DIGITAL INTERFACE FOR SOFTWARE-DEFINED RADIOS .................................................................................................................................................................................................................. THIS ARTICLE PRESENTS AN OPEN, COMPLETE RF-DIGITAL INTERFACE APPROPRIATE FOR SOFTWARE-DEFINED RADIOS (SDRS). THE INTERFACE INCLUDES DATA AND METADATA (CONTROL AND CONTEXT) PACKETS.THE CONTROL AND CONTEXT PACKETS DESCRIBE THE ENTIRE RF FRONT END.THE PROPOSED DESCRIPTION HAS A HIERARCHICAL STRUCTURE AND IS A HARDWARE ABSTRACTION.THE INTERFACE SUPPORTS ADVANCED ARCHITECTURES SUCH AS SDR CLOUDS.THE METADATA PACKETS CAN BE REPRESENTED USING FORMAL, COMPUTER-PROCESSABLE SEMANTICS. ......Wireless signals are centered at a RF front-end details certain RF. The signal-processing operations— As Figure 1 shows, the RF front end is not synchronization, modulation, and so on—are entirely analog; it consists of an analog front implemented on baseband signals centered at end and a digital front end (DFE).1 The DFE zero frequency. Therefore, receivers must does interpolation or decimation to increase or down-convert from RF to baseband. Trans- decrease the sampling frequency. Furthermore, mitters perform the opposite process of the down-conversion and up-conversion can up-conversion. -

CX74017 on the Direct Conversion Receiver

CX74017 On the Direct Conversion Receiver architectures, this paper presents the direct conversion Abstract reception technique and highlights some of the system-level issues associated with DCR. Increased pressure for low power, small form factor, low cost, and reduced bill of materials in such radio applications as mobile communications has driven academia and industry to resurrect Traditional Reception Techniques the Direct Conversion Receiver (DCR). Long abandoned in favor of the mature superheterodyne receiver, direct conversion has The Superheterodyne emerged over the last decade or so thanks to improved semiconductor process technologies and astute design The superheterodyne, or more generally heterodyne1, receiver techniques. This paper describes the characteristics of the DCR is the most widely used reception technique. This technique and the issues it raises. finds numerous applications from personal communication devices to radio and TV tuners, and has been tried inside out Introduction and is therefore well understood. It comes in a variety of combinations [7-9], but essentially relies on the same idea: the Very much like its well-established superheterodyne receiver RF signal is first amplified in a frequency selective low-noise counterpart, introduced in 1918 by Armstrong [1], the origins of stage, then translated to a lower intermediate frequency (IF), the DCR date back to the first half of last century when a single with significant amplification and additional filtering, and finally down-conversion receiver was first described by F.M. Colebrook downconverted to baseband either with a phase discriminatory in 1924 [2], and the term homodyne was applied. Additional or straight mixer, depending on the modulation format. -

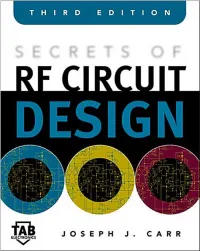

Variable Capacitors in RF Circuits

Source: Secrets of RF Circuit Design 1 CHAPTER Introduction to RF electronics Radio-frequency (RF) electronics differ from other electronics because the higher frequencies make some circuit operation a little hard to understand. Stray capacitance and stray inductance afflict these circuits. Stray capacitance is the capacitance that exists between conductors of the circuit, between conductors or components and ground, or between components. Stray inductance is the normal in- ductance of the conductors that connect components, as well as internal component inductances. These stray parameters are not usually important at dc and low ac frequencies, but as the frequency increases, they become a much larger proportion of the total. In some older very high frequency (VHF) TV tuners and VHF communi- cations receiver front ends, the stray capacitances were sufficiently large to tune the circuits, so no actual discrete tuning capacitors were needed. Also, skin effect exists at RF. The term skin effect refers to the fact that ac flows only on the outside portion of the conductor, while dc flows through the entire con- ductor. As frequency increases, skin effect produces a smaller zone of conduction and a correspondingly higher value of ac resistance compared with dc resistance. Another problem with RF circuits is that the signals find it easier to radiate both from the circuit and within the circuit. Thus, coupling effects between elements of the circuit, between the circuit and its environment, and from the environment to the circuit become a lot more critical at RF. Interference and other strange effects are found at RF that are missing in dc circuits and are negligible in most low- frequency ac circuits.