Architecture, Simulation, and Implementation of Commodity Computer Components in Software Defined Radio Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10

EE447 Lecture 6 Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10 HW7;5-4,5-7,5-13a-d,5-23,5-31 Due next Monday, 29th 1 Figure 4–29 Superheterodyne receiver. m(t) 2 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 1 EE447 Lecture 6 Synchronous Demodulation s(t) LPF m(t) 2Cos(2πfct) •Only method for DSB-SC, USB-SC, LSB-SC •AM with carrier •Envelope Detection – Input SNR >~10 dB required •Synchronous Detection – (no threshold effect) •Note the 2 on the LO normalizes the output amplitude 3 Figure 4–24 PLL used for coherent detection of AM. 4 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 2 EE447 Lecture 6 Envelope Detector C • Ac • (1+ a • m(t)) Where C is a constant C • Ac • a • m(t)) 5 Envelope Detector Distortion Hi Frequency m(t) Slope overload IF Frequency Present in Output signal 6 3 EE447 Lecture 6 Superheterodyne Receiver EE445-09 7 8 4 EE447 Lecture 6 9 Super-Heterodyne AM Receiver 10 5 EE447 Lecture 6 Super-Heterodyne AM Receiver 11 RF Filter • Provides Image Rejection fimage=fLO+fif • Reduces amplitude of interfering signals far from the carrier frequency • Reduces the amount of LO signal that radiates from the Antenna stop 2/22 12 6 EE447 Lecture 6 Figure 4–30 Spectra of signals and transfer function of an RF amplifier in a superheterodyne receiver. 13 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. -

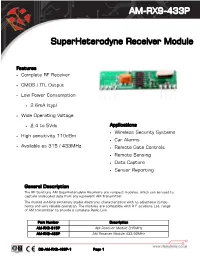

AM-RX9-433P Superheterodyne Receiver Module

AM-RX9-433P SuperHeterodyne Receiver Module Features Complete RF Receiver CMOS / TTL Output Low Power Consumption 2.6mA (typ) Wide Operating Voltage 2.4 to 5Vdc Applications Wireless Security Systems High sensitivity 110dBm Car Alarms Available as 315 / 433MHz Remote Gate Controls Remote Sensing Data Capture Sensor Reporting General Description The RF Solutions AM Superheterodyne Receivers are compact modules, which can be used to capture undecoded data from any equivalent AM Transmitter The module exhibits extremely stable electronic characteristics with no adjustable compo- nents and very reliable operation. The modules are compatible with R F solutions Ltd. range of AM transmitter to provide a complete Radio Link. Part Number Description AM-RX9-315P AM Receiver Module 315MHz AM-RX9-433P AM Receiver Module 433.92MHz DS-AM-RX9-433P-1 Page 1 AM-RX9-433P Mechanical Data Pin Decriptions Pin Description 1 Antenna In 2, 3, 8 Ground 4, 5 Supply voltage 6,7 Data Output Electrical Characteristics Ambient temp = 25°C unless otherwise stated. Characteristic Min Typical Max Dimensions Supply Voltage 2.4 5 5.5 Vdc Supply Current 2.6 mA RF Sensitivity (Vcc=5V, 1Kbps AM 99% -109 dBm @433MHz Square wave modulation) 315 Working Frequency MHz 433.92 High Level Output 0.7Vcc V Low Level Output 0.3Vcc V IF Bandwidth 280 KHz Data Rate 1 10 Kbps DS-AM-RX9-433P-1 Page 2 AM-RX9-433P Typical Application Vcc 1K 15K 13 14 4 Sleep Vcc 17 RX3 Receiver L Vcc OP1 O/P 1 12 Option 1 2 3 7 11 13 15 Status LKIN 18 LED Link OP2 O/P 2 M 1 OP3 O/P 3 2 OP4 O/P 4 10 3 LRN LB Transmitter RF600D Low Battery 1K 11 Serial Data Learn SD1 Output Switch 9 7 IN ECLK GND 5 22K RF Meter RF Multi Meter is a versatile handheld test meter checking Radio signal strength or interference in a given area. -

Superheterodyne Receiver

Superheterodyne Receiver The received RF-signals must transformed in a videosignal to get the wanted informations from the echoes. This transformation is made by a super heterodyne receiver. The main components of the typical superheterodyne receiver are shown on the following picture: Figure 1: Block diagram of a Superheterodyne The superheterodyne receiver changes the rf frequency into an easier to process lower IF- frequency. This IF- frequency will be amplified and demodulated to get a videosignal. The Figure shows a block diagram of a typical superheterodyne receiver. The RF-carrier comes in from the antenna and is applied to a filter. The output of the filter are only the frequencies of the desired frequency-band. These frequencies are applied to the mixer stage. The mixer also receives an input from the local oscillator. These two signals are beat together to obtain the IF through the process of heterodyning. There is a fixed difference in frequency between the local oscillator and the rf-signal at all times by tuning the local oscillator. This difference in frequency is the IF. this fixed difference an ganged tuning ensures a constant IF over the frequency range of the receiver. The IF-carrier is applied to the IF-amplifier. The amplified IF is then sent to the detector. The output of the detector is the video component of the input signal. Image-frequency Filter A low-noise RF amplifier stage ahead of the converter stage provides enough selectivity to reduce the image-frequency response by rejecting these unwanted signals and adds to the sensitivity of the receiver. -

CX74017 on the Direct Conversion Receiver

CX74017 On the Direct Conversion Receiver architectures, this paper presents the direct conversion Abstract reception technique and highlights some of the system-level issues associated with DCR. Increased pressure for low power, small form factor, low cost, and reduced bill of materials in such radio applications as mobile communications has driven academia and industry to resurrect Traditional Reception Techniques the Direct Conversion Receiver (DCR). Long abandoned in favor of the mature superheterodyne receiver, direct conversion has The Superheterodyne emerged over the last decade or so thanks to improved semiconductor process technologies and astute design The superheterodyne, or more generally heterodyne1, receiver techniques. This paper describes the characteristics of the DCR is the most widely used reception technique. This technique and the issues it raises. finds numerous applications from personal communication devices to radio and TV tuners, and has been tried inside out Introduction and is therefore well understood. It comes in a variety of combinations [7-9], but essentially relies on the same idea: the Very much like its well-established superheterodyne receiver RF signal is first amplified in a frequency selective low-noise counterpart, introduced in 1918 by Armstrong [1], the origins of stage, then translated to a lower intermediate frequency (IF), the DCR date back to the first half of last century when a single with significant amplification and additional filtering, and finally down-conversion receiver was first described by F.M. Colebrook downconverted to baseband either with a phase discriminatory in 1924 [2], and the term homodyne was applied. Additional or straight mixer, depending on the modulation format. -

Variable Capacitors in RF Circuits

Source: Secrets of RF Circuit Design 1 CHAPTER Introduction to RF electronics Radio-frequency (RF) electronics differ from other electronics because the higher frequencies make some circuit operation a little hard to understand. Stray capacitance and stray inductance afflict these circuits. Stray capacitance is the capacitance that exists between conductors of the circuit, between conductors or components and ground, or between components. Stray inductance is the normal in- ductance of the conductors that connect components, as well as internal component inductances. These stray parameters are not usually important at dc and low ac frequencies, but as the frequency increases, they become a much larger proportion of the total. In some older very high frequency (VHF) TV tuners and VHF communi- cations receiver front ends, the stray capacitances were sufficiently large to tune the circuits, so no actual discrete tuning capacitors were needed. Also, skin effect exists at RF. The term skin effect refers to the fact that ac flows only on the outside portion of the conductor, while dc flows through the entire con- ductor. As frequency increases, skin effect produces a smaller zone of conduction and a correspondingly higher value of ac resistance compared with dc resistance. Another problem with RF circuits is that the signals find it easier to radiate both from the circuit and within the circuit. Thus, coupling effects between elements of the circuit, between the circuit and its environment, and from the environment to the circuit become a lot more critical at RF. Interference and other strange effects are found at RF that are missing in dc circuits and are negligible in most low- frequency ac circuits. -

Redalyc.Software Defined Radio: Basic Principles and Applications

Facultad de Ingeniería ISSN: 0121-1129 [email protected] Universidad Pedagógica y Tecnológica de Colombia Colombia Machado-Fernández, José Raúl Software Defined Radio: Basic Principles and Applications Facultad de Ingeniería, vol. 24, núm. 38, enero-junio, 2015, pp. 79-96 Universidad Pedagógica y Tecnológica de Colombia Tunja, Colombia Available in: http://www.redalyc.org/articulo.oa?id=413940775007 How to cite Complete issue Scientific Information System More information about this article Network of Scientific Journals from Latin America, the Caribbean, Spain and Portugal Journal's homepage in redalyc.org Non-profit academic project, developed under the open access initiative José Raúl Machado-Fernández ISSN 0121-1129 eISSN 2357-5328 Software Defined Radio: Basic Principles and Applications Software Defined Radio: Principios y aplicaciones básicas Software Defined Radio: Princípios e Aplicações básicas Fecha de Recepción: 29 de Septiembre de 2014 José Raúl Machado-Fernández* Fecha de Aceptación: 15 de Noviembre de 2014 Abstract The author makes a review of the SDR (Software Defined Radio) technology, including hardware schemes and application fields. A low performance device is presented and several tests are executed with it using free software. With the acquired experience, SDR employment opportunities are identified for low-cost solutions that can solve significant problems. In addition, a list of the most important frameworks related to the technology developed in the last years is offered, recommending the use of three of them. Keywords: Software Defined Radio (SDR), radiofrequencies receiver, radiofrequencies transmitter, radio development frameworks, superheterodyne receiver, SDR hardware devices, SDR-Sharp, RTLSDR-Scanner. Resumen El autor realiza una revisión de la tecnología Radio Definido por Software (SDR, Software Defined Radio) incluyendo esquemas de hardware y campos de aplicación. -

5 RCA 26 Receiver

5 RCA 26 receiver- portables was not particularly difficult at the time. By contrast, designing a workable superheterodyne receiver wasn't particularly easy in 1925, as the valves that were then available were not very suitable for the task of frequency conversion. In fact, the design could be quite critical if the set was to operate at all. That situation improved in the early 1930s with the development of the. 2A7 and similar converter type valves. These new valves proved to be quite tolerant of circuit design inadequacies, making the design and manufacture of superhet receivers much easier. ..^. Superhet principles The RCA 26 portable superhet receiver Before the 1930s, most sets em- with its front open, ready for use. ployed TRF (tuned radio frequency) circuits. However, these had their shortcomings and superhet designs Prior to the 1930s, virtually all domestic quickly took over when suitable valves broadcast receivers used TRF circuits. became available. The superhet (or superheterodyne) One exception was the 1925 RCA 26 principle was developed during World portable which was one of the very first War 1 by Major Edwin Armstrong of the US Army. Armstrong was a prolific domestic superhets. It used some truly radio inventor who also developed innovative technology for the era. other radio techniques, including regeneration, super regeneration and frequency modulation (FM). Basically, the sup erhet was devel- NTIL RECENTLY, I'd always Why was this so remarkable? Well, oped because during WW1, the allies Uthought that "portable" radios superheterodyne receivers didn't be- needed direction finding (DF) receiv- (if you could call them that) were an come common in Australia until the ers that could receive the extremely innovation of the mid to late 1930s. -

Demodulation Or Transference Of

H03D DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER (masers, lasers H01S; circuits capable of acting both as modulator and demodulator H03C; details applicable to both modulators and frequency-changers H03C; demodulating pulses H03K9/00; transforming types of pulse modulation H03K11/00; coding, decoding or code conversion, in general H03M; repeater stations H04B7/14; demodulators adapted for ac systems of digital information transmission H04L27/00; synchronous demodulators adapted for colour television H04N9/66 ) Definition statement This subclass/group covers: Demodulation or transference of signals modulated on a sinusoidal carrier or on electromagnetic waves. Relationship between large subject matter areas The modulation and demodulation of pulse trains, for example in Pulse Width Modulation circuits, is covered in subclass H03K. System aspects of modulation by digital signals of the frequency, phase or amplitude of a sinusoidal carrier, or carriers, for example in quadrature (I-Q) modulation systems, and the demodulation thereof, is covered in subclass H04L. Analogue quadrature modulation used in the NTSC and PAL colour television systems (where the I and Q signals representing colour difference values are substantially continuously variable), and the demodulation of these signals, is covered in H04N. The modulation of sinusoidal signals, for example in AM and FM broadcasting, is covered in sub class H03C. References relevant to classification in this subclass This subclass/group does not cover: Masers, lasers H01S Circuits capable of acting both as H03C modulator and demodulator;balanced modulators Details applicable to both modulators H03C and frequency changers 1 Demodulating pulses which have H03K 9/00 been modulated with a continuously variable signal Transforming types of pulse H03K 11/00 modulation Relay systems, e.g. -

Edwin H. Armstrong Papers

Edwin H. Armstrong papers 1981.4 Finding aid prepared by Sarah Leu and Jack McCarthy through the Historical Society of Pennsylvania's Hidden Collections Initiative for Pennsylvania Small Archival Repositories. Last updated on September 12, 2016. The Historical and Interpretive Collections of The Franklin Institute Edwin H. Armstrong papers Table of Contents Summary Information....................................................................................................................................3 Biography/History..........................................................................................................................................4 Scope and Contents..................................................................................................................................... 10 Administrative Information......................................................................................................................... 11 Related Materials......................................................................................................................................... 12 Controlled Access Headings........................................................................................................................12 - Page 2 - Edwin H. Armstrong papers Summary Information Repository The Historical and Interpretive Collections of The Franklin Institute Creator Armstrong, Edwin H. (Edwin Howard), 1890-1954 Title Edwin H. Armstrong papers Call number 1981.4 Date [inclusive] 1909-1956 Extent -

Wide Frequency Range Superheterodyne Receiver Design and Simulation

Wide Frequency Range Superheterodyne Receiver Design and Simulation Chen-Yu Hsieh A Thesis In The Department of Electrical and Computer Engineering Presented in Partial Fulfillment of the Requirements For the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada January 2011 © Chen-Yu Hsieh, 2011 CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES This is to certify that the thesis prepared By: Chen-Yu Hsieh Entitled: “Wide Frequency Range Superheterodyne Receiver Design and Simulation” and submitted in partial fulfillment of the requirements for the degree of Master of Applied Science Complies with the regulations of this University and meets the accepted standards with respect to originality and quality. Signed by the final examining committee: ________________________________________________ Chair Dr. D. Qiu ________________________________________________ Examiner, External Dr. Y. Zeng, CIISE To the Program ________________________________________________ Examiner Dr. A. K. Elhakeem ________________________________________________ Supervisor Dr. Y. R. Shayan Approved by: ___________________________________________ Dr. W. E. Lynch, Chair Department of Electrical and Computer Engineering ____________20_____ ___________________________________ Dr. Robin A. L. Drew Dean, Faculty of Engineering and Computer Science ii Abstract Wide Frequency Range Superheterodyne Receiver Design and Simulation Chen-Yu Hsieh The receiver is the backbone of modern communication devices. The primary purpose of a reliable receiver is to recover the desired signal from a wide spectrum of transmitted sources. A general radio receiver usually consists of two parts, the radio frequency (RF) front-end and the demodulator. RF front-end receiver is roughly defined as the entire segment until the analog-to-digital converter (ADC) placed before digital demodulation. Theoretically, a radio receiver must be able to accommodate several tradeoffs such as spectral efficiency, low noise figure (NF), low power consumption, and high power gain. -

6.101 Final Project Report AM Receiver with Visual AM Spectrum Display Team Members: Kayla Esquivel and Jason Yang

1 6.101 Final Project Report AM Receiver with Visual AM Spectrum Display Team Members: Kayla Esquivel and Jason Yang 2 Table of Contents 1. Introduction 2. System Diagram 3. SubSystem Overview 3.1. Low Noise Amplifier 3.2. AntiImaging Filter 3.3. Mixer 3.4. Ramp Generator 3.5. Voltage Controlled Local Oscillator 3.6. IF Filter 3.7. Detector 3.8. Logarithmic Amplifier 3.9. Visual Spectrum Display 3.10. Audio Amplifier 4. Discussion 5. Conclusion 6. Works Cited 7. Acknowledgements 3 Table of Figures 1. System Block Diagram. Source: Esquivel and Yang 2. Low Noise Amplifier. Source: Esquivel and Yang 3. AntiImaging Filter. Source: Esquivel and Yang 4. Mixer Topologies. Source: Esquivel and Yang 5. Ramp Generator. Source: Esquivel and Yang 6. Voltage Controlled Local Oscillator. Source: Esquivel and Yang 7. IF Filter. Source: Esquivel and Yang 8. Diode Detector. Source: Esquivel and Yang 9. Logarithmic Amplifier. Source: Esquivel and Yang 10. Photograph of Spectrum Display on Oscilloscope Screen. Source: Esquivel and Yang 11. Tuning Comparator Topology. Source: Esquivel and Yang 12. Audio Amplifier. Source: Esquivel and Yang 13. Breadboard Layout of Radio and Spectrum Sweep. Source: Esquivel and Yang 4 1. Introduction Kayla Esquivel and Jason Yang The invention and mass application of radio broadcast was triggered in the first decade of the nineteenth century by Lee De Forest with his Audion triode vacuum tube (Lewis 1993). By the first world war, radio transmission was in common use by many national entities, aided by the development of the superheterodyne receiver by Edwin Armstrong (Lewis 1993). -

One City—Two Giants: Armstrong and Sarnoff: Part 1

dsp HISTORY Harvey F. Silverman [ ] One City—Two Giants: Armstrong and Sarnoff: Part 1 EDITOR’S INTRODUCTION Our guest in this column is Dr. Harvey F. Silverman. Dr. vation. An outgrowth of this passion is that of using his Silverman received his Ph.D. and Sc.M. degrees from Brown knowledge and engineering skills to develop intelligent University. He earned his B.S.E. and B.S. degrees from Trinity means for deterring the many furry and feathered creatures College in Hartford, Connecticut. He worked at IBM T.J. who very much like to share in the eating, although not the Watson Research Center in Yorktown Heights, New York, planting and cultivating. So far, the critters are winning! between 1970 and 1980. During these ten years, he worked As our author mentions at the beginning of this article, in on a number of projects related to image processing methods 1969 he bought the book Man of High Fidelity, which was a applied to earth resources satellite data, analytical methods 1969 paperback version of a 1956 biography of Edwin for computer system performance, speech recognition, and Howard Armstrong. The book was so intriguing that the development of a real-time I/O system as the manager of Dr. Silverman borrowed an autobiography of David Sarnoff. the Speech Terminal Project. In 1980, he joined Brown This was the beginning of a journey where our author University as a professor of engineering. From 1991 to 1998, learned about these two inventors and how such two strong he was the dean of engineering at Brown University.