Operational Amplifiers Is That the User Often Finds That They Oscillate in Connections He Wishes Were Stable

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Op Amp Stability and Input Capacitance

Amplifiers: Op Amps Texas Instruments Incorporated Op amp stability and input capacitance By Ron Mancini (Email: [email protected]) Staff Scientist, Advanced Analog Products Introduction Figure 1. Equation 1 can be written from the op Op amp instability is compensated out with the addition of amp schematic by opening the feedback loop an external RC network to the circuit. There are thousands and calculating gain of different op amps, but all of them fall into two categories: uncompensated and internally compensated. Uncompen- sated op amps always require external compensation ZG ZF components to achieve stability; while internally compen- VIN1 sated op amps are stable, under limited conditions, with no additional external components. – ZG VOUT Internally compensated op amps can be made unstable VIN2 + in several ways: by driving capacitive loads, by adding capacitance to the inverting input lead, and by adding in ZF phase feedback with external components. Adding in phase feedback is a popular method of making an oscillator that is beyond the scope of this article. Input capacitance is hard to avoid because the op amp leads have stray capaci- tance and the printed circuit board contributes some stray Figure 2. Open-loop-gain/phase curves are capacitance, so many internally compensated op amp critical stability-analysis tools circuits require external compensation to restore stability. Output capacitance comes in the form of some kind of load—a cable, converter-input capacitance, or filter 80 240 VDD = 1.8 V & 2.7 V (dB) 70 210 capacitance—and reduces stability in buffer configurations. RL= 2 kΩ VD 60 180 CL = 10 pF 150 Stability theory review 50 TA = 25˚C 40 120 Phase The theory for the op amp circuit shown in Figure 1 is 90 β 30 taken from Reference 1, Chapter 6. -

EE C128 Chapter 10

Lecture abstract EE C128 / ME C134 – Feedback Control Systems Topics covered in this presentation Lecture – Chapter 10 – Frequency Response Techniques I Advantages of FR techniques over RL I Define FR Alexandre Bayen I Define Bode & Nyquist plots I Relation between poles & zeros to Bode plots (slope, etc.) Department of Electrical Engineering & Computer Science st nd University of California Berkeley I Features of 1 -&2 -order system Bode plots I Define Nyquist criterion I Method of dealing with OL poles & zeros on imaginary axis I Simple method of dealing with OL stable & unstable systems I Determining gain & phase margins from Bode & Nyquist plots I Define static error constants September 10, 2013 I Determining static error constants from Bode & Nyquist plots I Determining TF from experimental FR data Bayen (EECS, UCB) Feedback Control Systems September 10, 2013 1 / 64 Bayen (EECS, UCB) Feedback Control Systems September 10, 2013 2 / 64 10 FR techniques 10.1 Intro Chapter outline 1 10 Frequency response techniques 1 10 Frequency response techniques 10.1 Introduction 10.1 Introduction 10.2 Asymptotic approximations: Bode plots 10.2 Asymptotic approximations: Bode plots 10.3 Introduction to Nyquist criterion 10.3 Introduction to Nyquist criterion 10.4 Sketching the Nyquist diagram 10.4 Sketching the Nyquist diagram 10.5 Stability via the Nyquist diagram 10.5 Stability via the Nyquist diagram 10.6 Gain margin and phase margin via the Nyquist diagram 10.6 Gain margin and phase margin via the Nyquist diagram 10.7 Stability, gain margin, and -

TRANSIENT STABILITY of the WIEN BRIDGE OSCILLATOR I

TRANSIENT STABILITY OF THE WIEN BRIDGE OSCILLATOR i TRANSIENT STABILITY OF THE WIEN BRIDGE OSCILLATOR by RICHARD PRESCOTT SKILLEN, B. Eng. A Thesis Submitted ··to the Faculty of Graduate Studies in Partial Fulfilment of the Requirements for the Degree Master of Engineering McMaster University May 1964 ii MASTER OF ENGINEERING McMASTER UNIVERSITY (Electrical Engineering) Hamilton, Ontario TITLE: Transient Stability of the Wien Bridge Oscillator AUTHOR: Richard Prescott Skillen, B. Eng., (McMaster University) NUMBER OF PAGES: 105 SCOPE AND CONTENTS: In many Resistance-Capacitance Oscillators the oscillation amplitude is controlled by the use of a temperature-dependent resistor incorporated in the negative feedback loop. The use of thermistors and tungsten lamps is discussed and an approximate analysis is presented for the behaviour of the tungsten lamp. The result is applied in an analysis of the familiar Wien Bridge Oscillator both for the presence of a linear circuit and a cubic nonlinearity. The linear analysis leads to a highly unstable transient response which is uncommon to most oscillators. The inclusion of the slight cubic nonlinearity, however, leads to a result which is in close agreement to the observed response. ACKNOWLEDGEMENTS: The author wishes to express his appreciation to his supervisor, Dr. A.S. Gladwin, Chairman of the Department of Electrical Engineering for his time and assistance during the research work and preparation of the thesis. The author would also like to thank Dr. Gladwin and all his other undergraduate professors for encouragement and instruction in the field of circuit theor.y. Acknowledgement is also made for the generous financial support of the thesis project by the Defence Research Board·under grant No. -

OA-25 Stability Analysis of Current Feedback Amplifiers

OBSOLETE Application Report SNOA371C–May 1995–Revised April 2013 OA-25 Stability Analysis of Current Feedback Amplifiers ..................................................................................................................................................... ABSTRACT High frequency current-feedback amplifiers (CFA) are finding a wide acceptance in more complicated applications from dc to high bandwidths. Often the applications involve amplifying signals in simple resistive networks for which the device-specific data sheets provide adequate information to complete the task. Too often the CFA application involves amplifying signals that have a complex load or parasitic components at the external nodes that creates stability problems. Contents 1 Introduction .................................................................................................................. 2 2 Stability Review ............................................................................................................. 2 3 Review of Bode Analysis ................................................................................................... 2 4 A Better Model .............................................................................................................. 3 5 Mathematical Justification .................................................................................................. 3 6 Open Loop Transimpedance Plot ......................................................................................... 4 7 Including Z(s) ............................................................................................................... -

Oscillator Circuits

Oscillator Circuits 1 II. Oscillator Operation For self-sustaining oscillations: • the feedback signal must positive • the overall gain must be equal to one (unity gain) 2 If the feedback signal is not positive or the gain is less than one, then the oscillations will dampen out. If the overall gain is greater than one, then the oscillator will eventually saturate. 3 Types of Oscillator Circuits A. Phase-Shift Oscillator B. Wien Bridge Oscillator C. Tuned Oscillator Circuits D. Crystal Oscillators E. Unijunction Oscillator 4 A. Phase-Shift Oscillator 1 Frequency of the oscillator: f0 = (the frequency where the phase shift is 180º) 2πRC 6 Feedback gain β = 1/[1 – 5α2 –j (6α – α3) ] where α = 1/(2πfRC) Feedback gain at the frequency of the oscillator β = 1 / 29 The amplifier must supply enough gain to compensate for losses. The overall gain must be unity. Thus the gain of the amplifier stage must be greater than 1/β, i.e. A > 29 The RC networks provide the necessary phase shift for a positive feedback. They also determine the frequency of oscillation. 5 Example of a Phase-Shift Oscillator FET Phase-Shift Oscillator 6 Example 1 7 BJT Phase-Shift Oscillator R′ = R − hie RC R h fe > 23 + 29 + 4 R RC 8 Phase-shift oscillator using op-amp 9 B. Wien Bridge Oscillator Vi Vd −Vb Z2 R4 1 1 β = = = − = − R3 R1 C2 V V Z + Z R + R Z R β = 0 ⇒ = + o a 1 2 3 4 1 + 1 3 + 1 R4 R2 C1 Z2 R4 Z2 Z1 , i.e., should have zero phase at the oscillation frequency When R1 = R2 = R and C1 = C2 = C then Z + Z Z 1 2 2 1 R 1 f = , and 3 ≥ 2 So frequency of oscillation is f = 0 0 2πRC R4 2π ()R1C1R2C2 10 Example 2 Calculate the resonant frequency of the Wien bridge oscillator shown above 1 1 f0 = = = 3120.7 Hz 2πRC 2 π(51×103 )(1×10−9 ) 11 C. -

Chapter 6 Amplifiers with Feedback

ELECTRONICS-1. ZOLTAI CHAPTER 6 AMPLIFIERS WITH FEEDBACK Purpose of feedback: changing the parameters of the amplifier according to needs. Principle of feedback: (S is the symbol for Signal: in the reality either voltage or current.) So = AS1 S1 = Si - Sf = Si - ßSo Si S1 So = A(Si - S ) So ß o + A from where: - Sf=ßSo * So A A ß A = Si 1 A 1 H where: H = Aß Denominations: loop-gain H = Aß open-loop gain A = So/S1 * closed-loop gain A = So/Si Qualitatively different cases of feedback: oscillation with const. amplitude oscillation with narrower growing amplitude pos. f.b. H -1 0 positive feedback negative feedback Why do we use almost always negative feedback? * The total change of the A as a function of A and ß: 1(1 A) A A 2 A* = A (1 A) 2 (1 A) 2 Introducing the relative errors: A * 1 A A A * 1 A A 1 A According to this, the relative error of the open loop gain will be decreased by (1+Aß), and the error of the feedback circuit goes 1:1 into the relative error of the closed loop gain. This is the Elec1-fb.doc 52 ELECTRONICS-1. ZOLTAI reason for using almost always the negative feedback. (We can not take advantage of the negative sign, because the sign of the relative errors is random.) Speaking of negative or positive feedback is only justified if A and ß are real quantities. Generally they are complex quantities, and the type of the feedback is a function of the frequency: E.g. -

MT-033: Voltage Feedback Op Amp Gain and Bandwidth

MT-033 TUTORIAL Voltage Feedback Op Amp Gain and Bandwidth INTRODUCTION This tutorial examines the common ways to specify op amp gain and bandwidth. It should be noted that this discussion applies to voltage feedback (VFB) op amps—current feedback (CFB) op amps are discussed in a later tutorial (MT-034). OPEN-LOOP GAIN Unlike the ideal op amp, a practical op amp has a finite gain. The open-loop dc gain (usually referred to as AVOL) is the gain of the amplifier without the feedback loop being closed, hence the name “open-loop.” For a precision op amp this gain can be vary high, on the order of 160 dB (100 million) or more. This gain is flat from dc to what is referred to as the dominant pole corner frequency. From there the gain falls off at 6 dB/octave (20 dB/decade). An octave is a doubling in frequency and a decade is ×10 in frequency). If the op amp has a single pole, the open-loop gain will continue to fall at this rate as shown in Figure 1A. A practical op amp will have more than one pole as shown in Figure 1B. The second pole will double the rate at which the open- loop gain falls to 12 dB/octave (40 dB/decade). If the open-loop gain has dropped below 0 dB (unity gain) before it reaches the frequency of the second pole, the op amp will be unconditionally stable at any gain. This will be typically referred to as unity gain stable on the data sheet. -

Operational Amplifiers: Part 3 Non-Ideal Behavior of Feedback

Operational Amplifiers: Part 3 Non-ideal Behavior of Feedback Amplifiers AC Errors and Stability by Tim J. Sobering Analog Design Engineer & Op Amp Addict Copyright 2014 Tim J. Sobering Finite Open-Loop Gain and Small-signal analysis Define VA as the voltage between the Op Amp input terminals Use KCL 0 V_OUT = Av x Va + + Va OUT V_OUT - Note the - Av “Loop Gain” – Avβ β V_IN Rg Rf Copyright 2014 Tim J. Sobering Liberally apply algebra… 0 0 1 1 1 1 1 1 1 1 Copyright 2014 Tim J. Sobering Get lost in the algebra… 1 1 1 1 1 1 1 Copyright 2014 Tim J. Sobering More algebra… Recall β is the Feedback Factor and define α 1 1 1 1 1 Copyright 2014 Tim J. Sobering You can apply the exact same analysis to the Non-inverting amplifier Lots of steps and algebra and hand waving yields… 1 This is very similar to the Inverting amplifier configuration 1 Note that if Av → ∞, converges to 1/β and –α /β –Rf /Rg If we can apply a little more algebra we can make this converge on a single, more informative, solution Copyright 2014 Tim J. Sobering You can apply the exact same analysis to the Non-inverting amplifier Non-inverting configuration Inverting Configuration 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Copyright 2014 Tim J. Sobering Inverting and Non-Inverting Amplifiers “seem” to act the same way Magically, we again obtain the ideal gain times an error term If Av → ∞ we obtain the ideal gain 1 1 1 Avβ is called the Loop Gain and determines stability If Avβ –1 1180° the error term goes to infinity and you have an oscillator – this is the “Nyquist Criterion” for oscillation Gain error is obtained from the loop gain 1 For < 1% gain error, 40 dB 1 (2 decades in bandwidth!) 1 Copyright 2014 Tim J. -

How to Measure the Loop Transfer Function of Power Supplies (Rev. A)

Application Report SNVA364A–October 2008–Revised April 2013 AN-1889 How to Measure the Loop Transfer Function of Power Supplies ..................................................................................................................................................... ABSTRACT This application report shows how to measure the critical points of a bode plot with only an audio generator (or simple signal generator) and an oscilloscope. The method is explained in an easy to follow step-by-step manner so that a power supply designer can start performing these measurements in a short amount of time. Contents 1 Introduction .................................................................................................................. 2 2 Step 1: Setting up the Circuit .............................................................................................. 2 3 Step 2: The Injection Transformer ........................................................................................ 4 4 Step 3: Preparing the Signal Generator .................................................................................. 4 5 Step 4: Hooking up the Oscilloscope ..................................................................................... 4 6 Step 5: Preparing the Power Supply ..................................................................................... 4 7 Step 6: Taking the Measurement ......................................................................................... 5 8 Step 7: Analyzing a Bode Plot ........................................................................................... -

The TL431 in the Control of Switching Power Supplies Agenda

The TL431 in the Control of Switching Power Supplies Agenda Feedback generalities The TL431 in a compensator Small-signal analysis of the return chain A type 1 implementation with the TL431 A type 2 implementation with the TL431 A type 3 implementation with the TL431 Design examples Conclusion Agenda Feedback generalities The TL431 in a compensator Small-signal analysis of the return chain A type 1 implementation with the TL431 A type 2 implementation with the TL431 A type 3 implementation with the TL431 Design examples Conclusion What is a Regulated Power Supply? Vout is permanently compared to a reference voltage Vref. The reference voltage Vref is precise and stable over temperature. The error,ε =−VVrefα out, is amplified and sent to the control input. The power stage reacts to reduce ε as much as it can. Power stage - H Vout Control d variable Error amplifier - G Rupper + - Vin - - α + + Vp Modulator - G V PWM ref Rlower How is Regulation Performed? Text books only describe op amps in compensators… Vout Verr The market reality is different: the TL431 rules! V I’m the out law! Verr TL431 optocoupler How do we Stabilize a Converter? We need a high gain at dc for a low static error We want a sufficiently high crossover frequency for response speed ¾ Shape the compensator G(s) to build phase and gain margins! Ts( ) fc = 6.5 kHz 0° -0 dB ∠Ts( ) -88° GM = 67 dB ϕm = 92° -180° Ts( ) =−67 dB 10 100 1k 10k 100k 1Meg How Much Phase Margin to Chose? a Q factor of 0.5 (critical response) implies a ϕm of 76° a 45° ϕm corresponds -

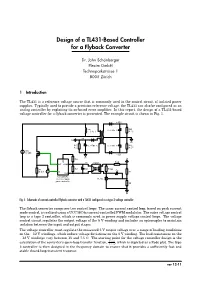

Design of a TL431-Based Controller for a Flyback Converter

Design of a TL431-Based Controller for a Flyback Converter Dr. John Schönberger Plexim GmbH Technoparkstrasse 1 8005 Zürich 1 Introduction The TL431 is a reference voltage source that is commonly used in the control circuit of isolated power supplies. Typically used to provide a precision reference voltage, the TL431 can also be configured as an analog controller by exploiting its on-board error amplifier. In this report, the design of a TL431-based voltage controller for a flyback converter is presented. The example circuit is shown in Fig. 1. 0 ) ( %& -./ ' *+, !""# $#"" Fig. 1: Schematic of current-controlled flyback converter with a TL431 configured as a type 2 voltage controller. The flyback converter comprises two control loops. The inner current control loop, based on peak current mode control, is realized using a UCC38C4x current-controlled PWM modulator. The outer voltage control loop is a type 2 controller, which is commonly used in power supply voltage control loops. The voltage control circuit regulates the output voltage of the 5 V winding and includes an optocoupler to maintain isolation between the input and output stages. The voltage controller must regulate the measured 5 V output voltage over a range of loading conditions on the 12 V windings, which induce voltage deviations on the 5 V winding. The load resistances on the ± 12 V windings vary between 15 and 7.5 Ω. The starting point for the voltage controller design is the ± calculation of the converter’s open-loop transfer function, Vo(s) , which is depicted as a Bode plot. The type Vc(s) 2 controller is then designed in the frequency domain to ensure that it provides a sufficiently fast and stable closed-loop transient response. -

Van Der Pol Approximation Applied to Wien Oscillators João Casaleiroa,B,∗, Luís B

Available online at www.sciencedirect.com ScienceDirect Procedia Technology 17 ( 2014 ) 335 – 342 Conference on Electronics, Telecommunications and Computers – CETC 2013 Van der Pol Approximation Applied to Wien Oscillators João Casaleiroa,b,∗, Luís B. Oliveirab, António C. Pintoa aDep. of Electronics, Telecommunications and Computers Engineering, Instituto Superior de Engenharia de Lisboa - ISEL, Lisboa, Portugal bDepartment of Electrical Engineering, FCT, CTS-Uninova, Caparica, Portugal Abstract This paper presents a nonlinear analysis of the Wien type oscillators based on the Van der Pol approximation. The steady-state equations for the key parameters, frequency and amplitude, are derived and their sensitivities to ambient temperature are discussed. The added value of this work is to present an analytical method to obtain the fundamental characteristics of the Wien type oscillators and to relate these characteristics with the circuit parameters in a simpler manner. The simulation results confirm the amplitude and frequency equations, and confirm that the amplitude is controlled by the limiter circuit. ©c 20142014 TheThe Authors. Authors. Published Published byby Elsevier Elsevier Ltd. Ltd. This is an open access article under the CC BY-NC-ND license (Selectionhttp://creativecommons.org/licenses/by-nc-nd/3.0/ and peer-review under responsibility of ISEL). – Instituto Superior de Engenharia de Lisboa. Peer-review under responsibility of ISEL – Instituto Superior de Engenharia de Lisboa, Lisbon, PORTUGAL. Keywords: Oscillator, Wien oscillator, quasi-sinusoidal, Van der Pol, amplitude stabilization. 1. Introduction The oscillators of the Wien type are well known, second order, quasi-sinusoidal oscillators, suited for low frequencies and low distortion applications [1]. The low-distortion feature of this type of oscillator justifies its use for the characterization of analog-to-digital converters (ADC)[2], instrumentation circuits and a wide variety of measurement circuits.