Implementing a Multirate Uncompressed Video Interface for Broadcast Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ABBREVIATIONS EBU Technical Review

ABBREVIATIONS EBU Technical Review AbbreviationsLast updated: January 2012 720i 720 lines, interlaced scan ACATS Advisory Committee on Advanced Television 720p/50 High-definition progressively-scanned TV format Systems (USA) of 1280 x 720 pixels at 50 frames per second ACELP (MPEG-4) A Code-Excited Linear Prediction 1080i/25 High-definition interlaced TV format of ACK ACKnowledgement 1920 x 1080 pixels at 25 frames per second, i.e. ACLR Adjacent Channel Leakage Ratio 50 fields (half frames) every second ACM Adaptive Coding and Modulation 1080p/25 High-definition progressively-scanned TV format ACS Adjacent Channel Selectivity of 1920 x 1080 pixels at 25 frames per second ACT Association of Commercial Television in 1080p/50 High-definition progressively-scanned TV format Europe of 1920 x 1080 pixels at 50 frames per second http://www.acte.be 1080p/60 High-definition progressively-scanned TV format ACTS Advanced Communications Technologies and of 1920 x 1080 pixels at 60 frames per second Services AD Analogue-to-Digital AD Anno Domini (after the birth of Jesus of Nazareth) 21CN BT’s 21st Century Network AD Approved Document 2k COFDM transmission mode with around 2000 AD Audio Description carriers ADC Analogue-to-Digital Converter 3DTV 3-Dimension Television ADIP ADress In Pre-groove 3G 3rd Generation mobile communications ADM (ATM) Add/Drop Multiplexer 4G 4th Generation mobile communications ADPCM Adaptive Differential Pulse Code Modulation 3GPP 3rd Generation Partnership Project ADR Automatic Dialogue Replacement 3GPP2 3rd Generation Partnership -

Creating 4K/UHD Content Poster

Creating 4K/UHD Content Colorimetry Image Format / SMPTE Standards Figure A2. Using a Table B1: SMPTE Standards The television color specification is based on standards defined by the CIE (Commission 100% color bar signal Square Division separates the image into quad links for distribution. to show conversion Internationale de L’Éclairage) in 1931. The CIE specified an idealized set of primary XYZ SMPTE Standards of RGB levels from UHDTV 1: 3840x2160 (4x1920x1080) tristimulus values. This set is a group of all-positive values converted from R’G’B’ where 700 mv (100%) to ST 125 SDTV Component Video Signal Coding for 4:4:4 and 4:2:2 for 13.5 MHz and 18 MHz Systems 0mv (0%) for each ST 240 Television – 1125-Line High-Definition Production Systems – Signal Parameters Y is proportional to the luminance of the additive mix. This specification is used as the color component with a color bar split ST 259 Television – SDTV Digital Signal/Data – Serial Digital Interface basis for color within 4K/UHDTV1 that supports both ITU-R BT.709 and BT2020. 2020 field BT.2020 and ST 272 Television – Formatting AES/EBU Audio and Auxiliary Data into Digital Video Ancillary Data Space BT.709 test signal. ST 274 Television – 1920 x 1080 Image Sample Structure, Digital Representation and Digital Timing Reference Sequences for The WFM8300 was Table A1: Illuminant (Ill.) Value Multiple Picture Rates 709 configured for Source X / Y BT.709 colorimetry ST 296 1280 x 720 Progressive Image 4:2:2 and 4:4:4 Sample Structure – Analog & Digital Representation & Analog Interface as shown in the video ST 299-0/1/2 24-Bit Digital Audio Format for SMPTE Bit-Serial Interfaces at 1.5 Gb/s and 3 Gb/s – Document Suite Illuminant A: Tungsten Filament Lamp, 2854°K x = 0.4476 y = 0.4075 session display. -

HD-SDI, HDMI, and Tempus Fugit

TECHNICALL Y SPEAKING... By Steve Somers, Vice President of Engineering HD-SDI, HDMI, and Tempus Fugit D-SDI (high definition serial digital interface) and HDMI (high definition multimedia interface) Hversion 1.3 are receiving considerable attention these days. “These days” really moved ahead rapidly now that I recall writing in this column on HD-SDI just one year ago. And, exactly two years ago the topic was DVI and HDMI. To be predictably trite, it seems like just yesterday. As with all things digital, there is much change and much to talk about. HD-SDI Redux difference channels suffice with one-half 372M spreads out the image information The HD-SDI is the 1.5 Gbps backbone the sample rate at 37.125 MHz, the ‘2s’ between the two channels to distribute of uncompressed high definition video in 4:2:2. This format is sufficient for high the data payload. Odd-numbered lines conveyance within the professional HD definition television. But, its robustness map to link A and even-numbered lines production environment. It’s been around and simplicity is pressing it into the higher map to link B. Table 1 indicates the since about 1996 and is quite literally the bandwidth demands of digital cinema and organization of 4:2:2, 4:4:4, and 4:4:4:4 savior of high definition interfacing and other uses like 12-bit, 4096 level signal data with respect to the available frame delivery at modest cost over medium-haul formats, refresh rates above 30 frames per rates. distances using RG-6 style video coax. -

Glossary of Digital Video Terms

Glossary of Digital Video Terms 24P: 24 frame per second, progressive scan. This has been the frame rate of motion picture film since talkies arrived. It is also one of the rates allowed for transmission in the DVB and ATSC television standards – so they can handle film without needing any frame-rate change (3:2 pull-down for 60 fields-per-second systems or running film at 25fps for 50 Hz systems). It is now accepted as a part of television production formats – usually associated with high definition 1080 lines, progressive scan. A major attraction is a relatively easy path from this to all major television formats as well as offering direct electronic support for motion picture film and D-cinema. 24Psf: 24 frame per second, progressive segmented frame. A 24P system in which each frame is segmented – recorded as odd lines followed by even lines. Unlike normal television, the odd and even lines are from the same snapshot in time – exactly as film is shown today on 625/50 TV systems. This way the signal is more compatible (than normal progressive) for use with video systems, e.g. VTRs, SDTI or HD-SDI connections, mixers/switchers etc., which may also handle interlaced scans. It can also easily be viewed without the need to process the pictures to reduce 24-frame flicker. 3:2 pull-down: Method used to map the 24 fps of film onto the 30 fps (60 fields) of 525-line TV, so that one film frame occupies three TV fields, the next two, etc. It means the two fields of every other TV frame come from different film frames making operations such as rotoscoping impossible, and requiring care in editing. -

Multi-Rate Serial Digital Interface (SDI) Physical Layer IP Core Is an Ipexpress User-Configurable Core and Can Be Used to Generate Any Allowable Configuration

ispLever TM CORECORE Multi-Rate Serial Digital Interface Physical Layer IP Core User’s Guide January 2012 ipug70_01.2 Multi-Rate Serial Data Interface Physical Layer Lattice Semiconductor IP Core User’s Guide Introduction Serial Digital Interface (SDI) is the most popular raw video link standard used in television broadcast studios and video production facilities. Field Programmable Gate Arrays (FPGAs) with SDI interface capability can be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more standard definition (SD) or high definition (HD) sources, perform sim- ple processing and retransmit the video data in SDI format. Such applications require an SDI physical layer (PHY) interface and some basic processing blocks such as a color space converter and frame buffer. In more complex applications, the acquired video receives additional processing, such as video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or Ethernet, with or without any additional video processing. In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components such as high speed I/Os (inputs/outputs), serializer/deserializer (SERDES), clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by in-house teams. The Lattice Multi-Rate SDI PHY Intellectual Property (IP) Core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side and the formatted parallel data on the other side. -

List of ITU-R Recommendations on DVD 2012 Edition 2

List of ITU-R Recommendations on DVD 2012 Edition 2 Series BO : Satellite delivery Number Approval Date Recommendation Title Status BO.566-3 1990-06 Terminology relating to the use of space communication techniques for Withdrawn broadcasting BO.600-1 1986-07 Standardized set of test conditions and measurement procedures for the In force subjective and objective determination of protection ratios for television in the terrestrial broadcasting and the broadcasting-satellite services BO.650-2 1992-03 Standards for conventional television systems for satellite broadcasting in In force the channels defined by Appendix 30 of the Radio Regulations BO.651 1986-07 Digital PCM coding for the emission of high-quality sound signals in In force satellite broadcasting (15 kHz nominal bandwidth) BO.652-1 1992-03 Reference patterns for Earth-station and satellite antennas for the In force broadcasting satellite service in the 12 GHz band and for the associated feeder links in the 14 GHz and 17 GHz bands BO.712-1 1992-03 High-quality sound/data standards for the broadcasting-satellite service in In force the 12 GHz band BO.786 1992-03 MUSE system for HDTV broadcasting-satellite services Withdrawn BO.787 1992-03 MAC/packet based system for HDTV broadcasting-satellite services Withdrawn BO.788-1 1994-08 Coding rate for virtually transparent studio quality HDTV emissions in the Withdrawn broadcasting-satellite service BO.789-2 1995-10 Service for digital sound broadcasting to vehicular, portable and fixed In force receivers for broadcasting-satellite service -

LOUDNESS PILOT.Pdf

English Manual Loudness Pilot Product Loudness Pilot Product firmware version Frame software 1.1.00 Document English Manual Document version / date 2014-10-07 Important safety instructions 1 Loudness Pilot – Basic concepts and Obtaining Loudness Pilot status Warning 2 operation 19 information 45 Caution: 3 Operating Loudness Pilot 20 Clock section 46 Service 3 Hardware versions 20 Status section 46 EMC/EMI 4 Expanding your Loudness Pilot 21 For the customers in Canada: 4 Loudness Pilot SDI: The Serial Digital Setting up audio and syncing 49 Interface 21 I/O Setup – SDI 50 About this manual 5 Loudness Pilot AES 21 I/O Setup – Loudness Pilot AES 53 Getting support 6 SDI vs. AES 22 Setting up audio dithering 55 Loudness Pilot presets 22 Before you get started 7 Loudness Pilot remote control 56 Register your product 8 Loudness Pilot Remote – Master 57 Stay up-to-date on loudness 8 status indicators and ports 23 Remote – GPI 59 Front panel indicators 24 GP Input Calibration 63 Unpacking and setup 9 Front panel reset button 26 Setting up GPO 64 Package contents 10 Back panel connectors 27 Remote – SDI 64 Setup 10 Setting up Loudness Pilot 31 Recalling, storing and deleting settings 67 Software: TC Icon and Loudness Pilot Networking basics and troubleshooting 32 Scenes, Routings, Engines 68 firmware 11 Quick Setup 35 The Library concept 69 Finding and installing TC Icon software – Updating Loudness Pilot software 36 Library – Recall page 70 Microsoft Windows 13 Library – Store page 71 Finding and installing TC Icon software – Basic operation -

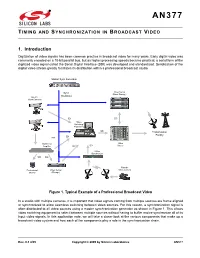

1. Introduction

AN377 TIMING AND SYNCHRONIZATION IN BROADCAST VIDEO 1. Introduction Digitization of video signals has been common practice in broadcast video for many years. Early digital video was commonly encoded on a 10-bit parallel bus, but as higher processing speeds became practical, a serial form of the digitized video signal called the Serial Digital Interface (SDI) was developed and standardized. Serialization of the digital video stream greatly facilitates its distribution within a professional broadcast studio. Master Sync Generator Sync Video Server (Mass Storage) (Genlock) On-site Video Cameras SDI SDI Video Switching/ Processing SDI Transmission Facility SDI SDI Distribution Video Amplifier SDI SDI Router Frame Synchronizer SDI SDI Remote Professional Video Server Video Camera Monitor (Storage) Figure 1. Typical Example of a Professional Broadcast Video In a studio with multiple cameras, it is important that video signals coming from multiple sources are frame aligned or synchronized to allow seamless switching between video sources. For this reason, a synchronization signal is often distributed to all video sources using a master synchronization generator as shown in Figure 1. This allows video switching equipment to select between multiple sources without having to buffer and re-synchronize all of its input video signals. In this application note, we will take a closer look at the various components that make up a broadcast video system and how each of the components play a role in the synchronization chain. Rev. 0.1 8/09 Copyright © 2009 by Silicon Laboratories AN377 AN377 2. Digitizing the Video Signal A video camera uses sensors to capture and convert light to electrical signals that represent the three primary colors– red, green, and blue (RGB). -

Source Image Format and Ancillary Data Mapping for the 3 Gb/S Serial

SMPTE ST 425-1:2017 Revision of SMPTE ST 425-1:2014 SMPTE STANDARD Source Image Format and Ancillary Data Mapping for the 3 Gb/s Serial Interface Page 1 of 32 pages Table of Contents Page 1 Scope ................................................................................................................................................... 3 2 Conformance Notation ....................................................................................................................... 3 3 Normative References ................................ ................................ ................................ ........................ 4 4 Level A — Direct Mapping of Source Image Formats ..................................................................... 5 4.1 20-Bit Virtual Interface ................................ ................................ ....................................................... 6 4.2 Virtual Interface — Data Stream Mappings .................................................................................... 13 5 Level B ― Mapping of SMPTE ST 372 Dual-Link .......................................................................... 23 5.1 SMPTE ST 372 Dual Link Mapping ................................ ................................ .................................. 24 6 Level B ― 2 x SMPTE ST 292-1 (HD-SDI) Dual-Stream Mapping ................................................. 26 6.1 2 x SMPTE ST 292 -1 (HD-SDI) Dual Stream Mapping ................................ .................................... 26 7 Levels -

22.2 Multichannel Audio Format Standardization Activity

22.2 Multichannel Audio Format Standardization Activity The audio format for Super Hi-Vision, which is 2. The 22.2 Multichannel Audio Format under research and development for high-presence 2.1 Requirements for a High-Presence Audio Format broadcasting in the future, is 22.2 multichannel audio. The requirements for a high-presence audio format for The 22.2 multichannel format is a 3D sound play-back use with Super Hi-Vision are as follows: format that is able to reproduce sound impressions that are much closer to natural sound than the 5.1 (1) Must be able to localize an audio image anywhere multichannel audio format used in current digital on the screen. broadcasts. Here, we present an overview of the 22.2 In viewing environments with a wide field of view multichannel audio format and describe current and large screen, it is important to be able to match the activities toward international standardization. positions of the video and audio images*2. Thus, a format that is able to localize the sound image anywhere on the screen is required. 1. Introduction At NHK STRL, we are developing Super Hi-Vision1) (2) Must be able to reproduce sound coming from all and conducting research toward the realization of high- directions surrounding the viewing position. presence broadcasting. Super Hi-Vision is an ultra-high- Sound arrives from all directions in the actual acoustic resolution video system with 4000 scaning lines and a field. Accordingly, to reproduce a high sense of presence, viewing angle*1 of 100°. The standard viewing distance the audio format must be able to reproduce sound for a video system is set such that the pixels are just coming from all directions. -

Dystrybucja I Sprzedaż: Meditronik Sp. Z O.O. 02-952 Warszawa, Ul

1:4 HD-SDI Distribution Amplifier One SDI Input Becomes 4 SDI Outputs for Real-Time Multi-Viewing The 1:4 HD-SDI Distribution Amplifier is a reliable video splitting device that allows a single SDI or HD-SDI video source to send data to four SDI or HD-SDI displays at the same time. Crisp, highly defined visuals are generated for each distributed output, and multiple formats (NTSC, PAL) plus high definition video resolutions (720 to 1080p) are fully supported. SDI SDI (serial digital interface), used primarily in broadcasting, converts and transmits digital video through SDI connectors. It processes high quality standard or high definition video. How It Works You simply connect your source to the 1:4 HD SDI Splitter's HD-SDI input, then connect your four displays to the Splitter's HD-SDI outputs. Once the source, the displays and the Splitter are powered and connected, your source's video appears on all four displays simultaneously. Features: z Easily distribute one HD-SDI source to four HD-SDI displays z Streamlines equipment; unnecessary hardware is eliminated z Distributes video instantaneously Specifications: z Input/Output: SDI - SMPTE 259M-C (270Mbps); HD-SDI -SMPTE 292M (1.485, 1.485/1.001 Gbps) z Supports NTSC, PAL & and all HD formats z 2048x1024 maximum input/output resolution z Power Consumption: 10 watts (max) z Dimensions: 7.5"W x 1.1"H x 3.5"D z Power Supply: 5V DC z Shipping Weight: 4 lbs. Package Includes: z 1:4 HD-SDI Distribution Amplifier z One 5v Power Supply z Owner's Manual EXT-HDSDI-144N Dystrybucja i sprzedaż: Meditronik Sp. -

SMPTE-259M SDI.Pdf

© SMPTE 2005 – All rights reserved SMPTE Standard for Television Date: 2005-12 08 SMPTE 259M Revision of 259M - 1997 SMPTE Technology Committee N26 on File Management & Networking Technology TP Rev 1 SDTV1DigitalSignal/Data - Serial Digital Interface Note 1 SDTV - Standard Definition Television Warning This document is not a SMPTE Standard. It is distributed for review and comment. It is subject to change without notice and may not be referred to as a SMPTE Standard. Recipients of this document are invited to submit, with their comments, notification of any relevant patent rights of which they are aware and to provide supporting documentation. Distribution does not constitute publication. Page 1 of 16 Contents Page Foreword 2 Introduction 2 1 Scope 3 2 Normative References 3 3 Signal Levels and Specifications 3 4 Connector and cable Types 5 5 Channel coding 5 6 Transmission order 5 7 Component 4:2:2 signals 5 8 Levels of operation 7 Annex A (Normative) Composite NTSC 4fsc signals 8 Annex B (Informative) Composite PAL 4fsc signals 10 Annex C (informative) Generator polynomial implementations 13 Annex D (informative) Timing jitter specification 14 Annex E (informative) Waveform measurement method 14 Annex F (Informative) Optional Ancillary Data 4fsc PAL 14 Annex G (informative) 259M Road Map 15 Bibliography 16 Page 2 of 16 Foreword SMPTE (the Society of Motion Picture and Television Engineers) is an internationally recognized standard developing organization. Headquartered and incorporated in the United States of America, SMPTE has members in over 80 countries on six continents. SMPTE’s Engineering Documents, including Standards, Recommended Practices and Engineering Guidelines, are prepared by SMPTE’s Technology Committees.