Satyadev Ahlawat – Assistant Professor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

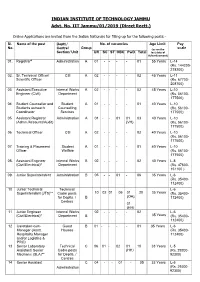

Detailed Advertisement No. Iitjammu/01/2019 (Direct Rectt.)

INDIAN INSTITUTE OF TECHNOLOGY JAMMU Advt. No. IIT Jammu/01/2019 (Direct Rectt.) Online Applications are invited from the Indian Nationals for filling up for the following posts:- Sl. Name of the post Deptt./ No. of vacancies Age Limit Pay No. Centre/ Group (as on the scale Section/ Unit UR SC ST OBC PwD Total last date of Advertisement) 01. Registrar# Administration A 01 - - - - 01 55 Years L-14 (Rs. 144200- 218200) 02. Sr. Technical Officer/ C3I A 02 - - - - 02 45 Years L-11 Scientific Officer (Rs. 67700- 208700) 03. Assistant Executive Internal Works A 02 - - - - 02 45 Years L-10 Engineer (Civil) Department (Rs. 56100- 177500) 04. Student Counsellor and Student A 01 - - - - 01 40 Years L-10 Students outreach Counselling (Rs. 56100- Coordinator Services 177500) 05. Assistant Registrar Administration A 01 - - 01 01 03 40 Years L-10 (Admn./Accounts/Audit) (VH) (Rs. 56100- 177500) 06. Technical Officer C3I A 02 - - - - 02 40 Years L-10 (Rs. 56100- 177500) 07. Training & Placement Student A 01 - - - - 01 40 Years L-10 Officer Welfare (Rs. 56100- 177500) 08. Assistant Engineer Internal Works B 02 - - - - 02 40 Years L-8 (Civil/Electrical)* Department (Rs. 47600- 151100 ) 09. Junior Superintendent Administration B 05 - - 01 - 06 35 Years L-6 (Rs. 35400- 112400) 10 Junior Technical Technical L-6 Superintendant (JTS)** Cadre posts 10 02 01 05 01 20 35 Years (Rs. 35400- for Deptts. / B (OH), 112400) Centres 01 (HH) 11 Junior Engineer Internal Works 02 - - - - 02 L-6 (Civil/Electrical)* Department B 35 Years (Rs. 35400- 112400) 12 Caretaker-cum- Guest B 01 - - - - 01 35 Years L-6 Manager (Asstt. -

Transportation Systems Engineering and Management (Ctsem 2021)

th 8 INTERNATIONAL CONFERENCE ON TRANSPORTATION SYSTEMS ENGINEERING AND MANAGEMENT (CTSEM 2021) August 26 - 27, 2021 (Online mode) Centre for Transportation Research Department of Civil Engineering National Institute of Technology Calicut Kozhikode - 673601, Kerala, India 8th INTERNATIONAL CONFERENCE ON TRANSPORTATION SYSTEMS ENGINEERING AND MANAGEMENT CTSEM 2021 Introduction Transportation systems play a vital role in the growth and development of economies. Reliable, cost effective and sustainable modes help in rapid movement of people and goods, not only within a country but also between countries. Considering the ubiquitous nature of the transportation system and the crucial role played by it in the lives of people, it is imperative that the problems associated with the transport systems are addressed in a time bound manner by the scientific community. It goes without saying that the problems associated with the transportation system get accentuated in urban areas. It is estimated that by the mid twenty-first century, 68% of the population will live in urban areas. Increase in purchasing power of the people have seen a rise in private vehicle ownership. The burgeoning population, rise in vehicle ownership, along with the demand for reliable and accessible transportation facilities for people and goods are posing a severe strain in the transportation systems. Moreover, unforeseen challenges in the form of the pandemic have posed serious challenges to the patronage of the public transport systems. Furthermore, safety, accessibility, mobility and parking challenge transportation engineers to suggest feasible and sustainable solutions for the problems. The need for the hour is therefore to provide sustainable solutions to transport related problems. -

Vol. 7, Issue XII December 2019

SHRI MATA VAISHNO DEVI UNIVERSITY DECEMBER 2019 Times@SMVDU VOLUME 7 ISSUE XII Monthly E-newsletter Patron: Prof. R.K. Sinha (Vice-Chancellor) Chairperson: Dr. Amitabh V Dwivedi Farewell to Finance Officer Shri Romesh Singh (KAS) SMVDU Students Bag 170 Campus End Semester Placement Offers from 12 Companies Examinations Conducted Shri Mata Vaishno Devi University started off its Campus July-December Placement Programme-2020 in September 2019 for the 2019 students of batch passing out in May 2020 Infosys was the first company to visit SMVDU on 17th September 2019, and selected (37) students, followed by Wipro (20), ICICI Bank (15), TCS (24), ICICI Prudential (20), Ceasefire Industries (04), Ezmata Technologies (09), Orange (13), Ericsson (15), Indian Navy etc. The students of SMVDU bagged 170 placements offers with highest CTC of 7 Lac/Annum and average CTC of 3.75 Lac/Annum. Among 12 recruiting companies 09 are the regular recruiters and three companies, namely Ezmata Technologies, Pune, Berger Paints Kolkata SMVDU Students Participated in MOOD INDIGO 1 2 FEST@ IIT Bombay TEQIP-III SPONSORED 6TH NATIONAL CONFERENCE Asia’s Largest Cultural Festival INTERNATIONAL CONFERENCE 20-21 JAN 2020 Recent Trends & Advancements in Contemporary Trends in Humanities 26-29 December Engineering and Technology & Social Sciences 2019 17-18 JAN 2020 1 VOLUME 7 ISSUE XII DECEMBER 2019 and Ericsson Global Guru Gram are the new ones to visit SMVDU first time for campus hiring. The SMVDU also conducted 03 pool drives considering the students of other institutions of the region for campus placement. Despite the economic slowdown, the Campus Placement in the university has actually ascended in the current session. -

News Letter 2019.Cdr

JAGTI Winter 2018-19 1 IIT Jammu’s Newsletter JAGTI Winter ‘18-19 जगती SPIC MACAY IIT JAMMU successfully organized its rst-ever event as part of the Society for the Promotion of Indian Classical Music And Culture Amongst Youth (SPIC MACAY) on 12th of October 2018. India's leading classical vocalist Vidushi Kalapini Komkali along with Shambhunath Bhattacharya and Chetan Nigam on instruments presented various forms of ragas which provided an edge in reviving the classical forms of music among the IIT Jammu students. REPUBLIC DAY CELEBRATION ORGAN DONATION AWARENESS 70th Republic Day of India was celebrated with a vibrant cultural IIT Jammu organised its rst organ donation awareness program in event organised by the cultural, literary and art clubs at IIT Jammu. collaboration with MOHAN FOUNDATION on 16 January 2019. MOU’S INTERNSHIP IN FRANCE IIT Jammu has signed MoU's with the following institutions to Aakar Sharma and Akshit Kansra got an opportunity to work with collaborate in Education, Internships and Research, jointly organize Dr Akka Zemmari, Associate Professor at the University of seminars conferences & workshops: Bordeaux, France as research interns. They primarily worked on Vehicular Ad-hoc network and on implementing an algorithm in · Dhirubhai Ambani Institute of Information and Communication Tenserow which aims to increase the Training stability of Deep Technology. Convolutional Neural Networks.This proved to be a successful · Council of Scientic and Industrial Research (CSIR), New Delhi. programme which brought with it many learning opportunities. · Foundation for Innovation and Technology Transfer, New Delhi. JAGTI Winter 2018-19 2 OUTREACH BY IIT JAMMU Machine assembling and Disassembling workshop” by Dr. -

TRG NEWSLETTER a Ternary Newsletter of Transportation Research Group of India Vol

Transportation Research Group of India ...towards sustainable transport (Regd. Under the Karnataka Societies Registration Act, 1960) Reg. No. DRB/C/SOR/29/2011-12 Decennial Year Celebration: 28th May, 2021 TRG NEWSLETTER A Ternary Newsletter of Transportation Research Group of India Vol. 3(1) May, 2021 Editors Dr. Ankit Kathuria Dr. Anuj Budhkar Dr. Anil Kumar Bachu Harpreet Singh Editor, Editor, Editor, Associate Editor, IIT Jammu IIEST Shibpur IIT Patna IIT Jammu www.trgindia.org Transportation Research Group of India In this Issue Message from Former President, TRG Message from President, We are pleased to release the latest version of TRG TRG Newsletter on this very important occasion of successful completion of 10 years of the society. With the new and young editorial team taking charge of the newsletter, I am confident that the TRG Newsletter will Welcoming New Executive not only be regularly brought out but will also become Board of TRG richer and more innovative in its contents. This day also mark the occasion of passing the baton of TRG to the new Executive Board (EB) and I am confident that the Dr. Ashish Verma, Technical Committees of IISc Bengaluru collective effort of the new EB along with all the TRG Former President, TRG members of TRG will take the society to newer heights in future. My best wish to the new Editorial Team and the new EB. Evolution of CTRG Message from New President, TRG Other Activities of TRG Dear Transportation Professionals, Transportation Research Group of India (TRG) has completed a successful journey of more than one decade since its inception. -

Ugad 1819.Pdf

An initiative of Branding & Communications team of IIT Kharagpur and the students body Branding & Relations Cell led by Dean, International Relations. For more information contact: [email protected] I congratulate the Branding and Communications Cell of the Institute for this novel initiative. Students enjoy the learning experience best when they are challenged. I have often interacted with students, asking them what they thought was the best or worst in a class that they had just attended. And I have often been stumped by their replying that they thought they had “learnt nothing”. Why? I asked them. They said that they did not find the teaching challenging enough. This should leave no one in doubt that we should take another look at the teaching and learning process. Students themselves can be a part of this relook. I have often advocated for student-teachers, often letting them take my own class. The result has been phenomenal, making students involved learners. Only greater involvement on the part of students can ensure their learning. This does not have to happen inside the class always. Sports, extra-curricular activities provide their own challenges. I encourage students to take up these challenges. As these entries show, many of them have indeed taken them up, and realized their enormous potential and talent. Tap your hidden talents and energies. Take up challenges, get involved and enjoy the learning experience Every student is an achiever in his or her own right. Each of them has tremendous potential inside them, and if they pursue their passion with focus and hard work, they will reach their goal. -

ANNUAL REPORT 2019-20 IIT Bombay Annual Report 2019-20 Content

IIT BOMBAY ANNUAL REPORT 2019-20 IIT BOMBAY ANNUAL REPORT 2019-20 Content 1) Director’s Report 05 2) Academic Programmes 07 3) Research and Development Activities 09 4) Outreach Programmes 26 5) Faculty Achievements and Recognitions 27 6) Student Activities 31 7) Placement 55 8) Society For Innovation And Entrepreneurship 69 9) IIT Bombay Research Park Foundation 71 10) International Relations 73 11) Alumni And Corporate Relations 84 12) Institute Events 90 13) Facilities 99 a) Infrastructure Development b) Central Library c) Computer Centre d) Centre For Distance Engineering Education Programme 14) Departments/ Centres/ Schools and Interdisciplinary Groups 107 15) Publications 140 16) Organization 141 17) Summary of Accounts 152 Director's Report By Prof. Subhasis Chaudhuri, Director, IIT Bombay Indian Institute of Technology Bombay acknowledged for their research contributions. (IIT Bombay) has a rich tradition of pursuing We have also been able to further our links with excellence and has continually re-invented international and national peer universities, itself in terms of academic programmes and enabling us to enhance research and educational research infrastructure. Students are exposed programmes at the Institute. to challenging, research-based academics and IIT Bombay continues to make forays into a host of sport, cultural and organizational newer territories pertinent to undergraduate activities on its vibrant campus. The presence and postgraduate education. At postgraduate of world-class research facilities, vigorous level, a specially designed MA+PhD dual institute-industry collaborations, international degree programme in Philosophy under the exchange programmes, interdisciplinary HSS department has been introduced. IDC, the research collaborations and industrial training Industrial Design Centre, celebrated 50 years opportunities help the students of IIT Bombay to of its golden existence earlier this year. -

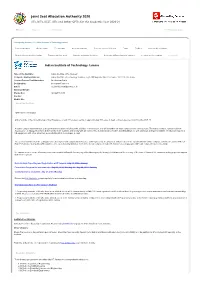

Joint Seat Allocation Authority 2020 Iits, Nits, IIEST, Iiits and Other-Gftis for the Academic Year 2020-21

Joint Seat Allocation Authority 2020 IITs, NITs, IIEST, IIITs and Other-GFTIs for the Academic Year 2020-21 Home Services User Manuals Prof Goutam Dutta Participating Instiute ( PI ): Indian Institute of Technology Jammu Basic Informations About Institute Fee Structure Academic Structure Rules for Change of Branch Faculty Facilities Students life at Institute Financial Assistance/Scholarship Training and Placement Industry and Alumni Relations Recreational/Extra Curricular activities Location and Accessibility View Profile Indian Institute of Technology Jammu Type of the institute: Indian Institute of Technology Complete Mailing Address: Indian Institute of Technology Jammu, Jagti, PO Nagrota, NH-44 Jammu - 181 221 J&K, India Contact Person For Admission: Dr. Goutam Dutta Designation: Associate Professor Email: [email protected] Alternate Email: Phone Nos: 0191-257-0633 Fax No: Mobile No.: About the Institute: Welcome to IIT Jammu! At the foothills of the Shivalik range of the Himalayas, a new IIT has been set up in approximately 400 acres in Jagti, a forest area near Jammu City at NH 44. A transit campus has been built at the permanent location to facilitate the activities of the Institute, this will extend to the main campus in the coming years. The transit campus, operational from August 2017, is equipped to meet all the needs of the students and faculty with 18 classrooms, 15 laboratories, modern hostel buildings for girls and boys and sports facilities. All advanced types of lab equipment with other amenities are available within the campus at Jagti. The Central Instrumentation Facility (CIF) to cater higher-end equipments in Science and Engineering are proposed and procured to be operated from Paloura campus, Jammu. -

Indian Institute of Technology, Jammu

Indian Institute of Technology, Jammu Jammu An exclusive Guide by Indian Institute of Technology, Jammu Reviews on Placements, Faculty & Facilities Check latest reviews and ratings on placements, faculty, facilities submitted by students & alumni. Reviews (Showing 9 of 9 reviews) Overall Rating (Out of 5) 4.4 Based o n 7 Verif ied Reviews Distribution of Rating >4-5 star 71% >3-4 star 29% >2-3 star 0% 1-2 star 0% Component Ratings (Out of 5) Placements 4.1 Infrastructure 4.3 Faculty & Course 4.4 Curriculum Crowd & Campus Life 4.4 Value for Money 4.7 The Verif ied badge indicates that the reviewer's details have been verified by Shiksha, and reviewers are bona f ide students of this college. These reviews and ratings have been given by students. Shiksha does not endorsed the same. Out of 9 published reviews, 7 reviews are verif ied. N Neelu Choudhary | B.Tech. in Computer Science and Engineering - Batch of Verified 2024 Reviewed on 7 Aug 2021 4.4 Placements 4 Infrastructure 5 Faculty & Course Curriculum 4 Crowd & Campus Life 4 I would recommend joining this college as it has good placements. Placements: About 70-80% of the students get placed every year. The highest salary package offered is 42 LPA, and the average salary package offered is 17 LPA. The lowest Disclaimer: This PDF is auto-generated based on the information available on Shiksha as on 23-Sep-2021. salary package offered is 12.2 LPA. The top-most companies which offer recruitment are amazon, Arista Networks, Forbes Marshell, Cognizant, Oyo Optum, JBM, and many more. -

Indian Institute of Technology Jammu, Jagti, Nh 44, Po Nagrota, Jammu (J&K) 181221

INDIAN INSTITUTE OF TECHNOLOGY JAMMU, JAGTI, NH 44, PO NAGROTA, JAMMU (J&K) 181221 Advertisement No. IITJMU/Faculty/04/2018 IIT Jammu invites applications from Indian Nationals, Persons of Indian Origins (PIOs), Overseas Citizens of India (OCIs), and Foreign Nationals with proven academic credentials and who have a passion for teaching and research, for faculty positions at the level of Professor, Associate Professor, Assistant Professor (Grade I & II) and Visiting Professor in the following disciplines: Chemical Engineering, Chemistry, Civil Engineering, Computer Science & Engineering, Electrical Engineering, Humanities & Social Science, Material Science & Engineering, Mathematics, Mechanical Engineering, and Physics. Applicants should hold a Ph.D. degree in one of the above disciplines. Industry experience and/or post-doctoral experience is highly desirable. Candidates must have a passion for excellence in both research and teaching. IIT Jammu offers one of the best possible compensation, facilities, and support systems on the lines of other centrally funded institutes of higher education. Additionally, IIT Jammu provides a healthy start-up research grant and relocation expenses at the time of joining. For more information, please visit the website http://iitjammu.ac.in/faculty-search-cum-selection Interested candidates may apply via online application portal https://apply.iitjammu.ac.in Senior Level Positions. At senior levels, IIT Jammu hopes to attract a select few who have a well-established global reputation in research and development, and who can take leadership for new centers, programs, etc. Applications are particularly invited from senior researchers who are looking for a suitable opportunity to establish a center in India in some specialized area, particularly promoting interdisciplinary research. -

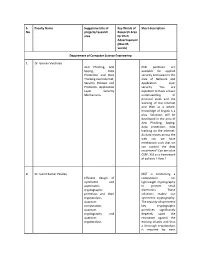

S. No. Faculty Name Suggestive Title of Projects/Research

S. Faculty Name Suggestive title of Key Words of Short description No. projects/research Research Area area for Ph.D Advertisement (Max 05 words) Department of Computer Science Engineering 1. Dr. Gaurav Varshney Anti Phishing, Anti PhD positions are Spying, Data available for applied Protection and Data security enthusiast in the Tracking over Internet, area of Network and Security Policies and Application layer Protocols, Application security. You are Layer Security expected to have a basic Mechanisms understanding of protocol stack and the working of the Internet and Web as a whole. Knowledge of Crypto is a plus. Solutions will be developed in the area of Anti Phishing, Spying, data protection, data tracking on the Internet. As data moves across the web can we have mechanism such that we can control the data movement? Can we solve CSRF, XSS as a framework of policies ? How ? 2. Dr. Sumit Kumar Pandey NIST is conducting a Efficient design of competition for symmetric and lightweight cryptography asymmetric to protect small cryptographic electronics. These primitives and their solutions mainly use cryptanalysis, symmetric cryptography. quantum The security of symmetric computation, key cryptographic quantum primitives significantly cryptography and depends upon the quantum resistance against the cryptanalysis. existing attacks and thus a thorough cryptanalysis is required for each cipher before its final acceptance. In recent years, there is a considerable advancement in the field of the development of quantum computers. Once the quantum computer becomes reality, factorisation and discrete log problem based public key cryptosystems will become insecure. Therefore, NIST is conducting another competition for the selection of postquantum public key encryption, key-establishment algorithms and digital signature schemes. -

Innovation in Materials & Manufacturing (IMM

About the Institute IIT Jammu is an Institute of National Importance undergraduate curriculum but also foster funded by the Government of India. It was research in various specialized and inaugurated on 6th August, 2016. Currently, IIT interdisciplinary areas. There is an array of Jammu has two operational campuses; one at specialized mechanical engineering subjects such Paloura and another one at Jagti, Nagrota. The as Advanced manufacturing, energy conversion, Institute provides cutting-edge academic and research infrastructure for the growth of its materials processing, MEMS, microfluidic AICTE Training and Learning (ATAL) students and faculty. At present, IIT Jammu is devices, nano-mechanics, tribology and Academy Faculty Development Program (FDP) offering B.Tech. degree in six major disciplines vibrations which this department intends to Theme: Sustainability Engineering viz. Mechanical Engineering, Electrical develop as Centre of Excellence. This creates 26th-30th October 2020 Engineering, Computer Science, Chemical potential career opportunities in diverse areas Innovation in Materials & Engineering, Material Engineering and Ph.D. in within an industry, government and R&D, such major relevant areas (including Physics, as automotive industries, railways, power Manufacturing (IMM-2020) chemistry, mathematics). IIT Jammu is on the generation, environment, medical and verge of establishing highly dedicated central research facilities along with advanced teaching manufacturing industries. The department is laboratories. IIT Jammu’s goal is to become being nourished by dedicated teaching and internationally recognized for the quality of its research professionals and the highly skilled lab research and creative endeavors and their staff. In addition, we are focusing on applicability to improving quality of life. collaborations with various industries to design relevant curricula and to provide students with an exposure to the real world.