2021 Proxy Statement

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

Lecture Note 7. IA: History and Features

System Programming Lecture Note 7. IA: History and Features October 30, 2020 Jongmoo Choi Dept. of Software Dankook University http://embedded.dankook.ac.kr/~choijm (Copyright © 2020 by Jongmoo Choi, All Rights Reserved. Distribution requires permission) Objectives Discuss Issues on ISA (Instruction Set Architecture) ü Opcode and operand addressing modes Apprehend how ISA affects system program ü Context switch, memory alignment, stack overflow protection Describe the history of IA (Intel Architecture) Grasp the key technologies in recent IA ü Pipeline and Moore’s law Refer to Chapter 3, 4 in the CSAPP and Intel SW Developer Manual 2 Issues on ISA (1/2) Consideration on ISA (Instruction Set Architecture) asm_sum: addl $1, %ecx movl -4(%ebx, %ebp, 4), %eax call func1 leave ü opcode issues § how many? (add vs. inc è RISC vs. CISC) § multi functions? (SISD vs. SIMD vs. MIMD …) ü operand issues § fixed vs. variable operands f bits n bits n bits n bits § fixed: how many? opcode operand 1 operand 2 operand 3 § operand addressing modes f bits n bits n bits ü performance issues opcode operand 1 operand 2 § pipeline f bits n bits § superscalar opcode operand 1 § multicore 3 Issues on ISA (2/2) Features of IA (Intel Architecture) ü Basically CISC (Complex Instruction Set Computing) § Variable length instruction § Variable number of operands (0~3) § Diverse operand addressing modes § Stack based function call § Supporting SIMD (Single Instruction Multiple Data) ü Try to take advantage of RISC (Reduced Instruction Set Computing) § Micro-operations -

Advancement in Processor's Architecture

© June 2021| IJIRT | Volume 8 Issue 1 | ISSN: 2349-6002 Advancement In Processor’s Architecture Avinash Maurya1, Prachi Mishra2, Prateek Choudhary3, Prashant Upadhyay4 1,2,3,4 Student of Information Technology, RKGIT, Ghaziabad, India Abstract - AMD has launched its next-gen Zen 3 lineup physical layout perspective. The Zen2 AMD Ryzen CPU which makes it the best and most powerful processor series had a big improvement in architecture commercial CPU series. as they moved from 12/14nm processors to 7nm The "Zen 3" core architecture delivers a 19% increase architecture manufactured by TSMC (Taiwan in the instructions per clock for the Ryzen 5600x, 5800x, Semiconductor Manufacturing Company). 5900x, and 5950x. This is a significant modification in the last decade that The 2nd Gen AMD Ryzen processor's which is there happened due to the improvement in core architecture, in the AMD Ryzen 7 3700x has one compute die with which results in full access of the L3 cache without 8 cores and one input/output die that handles PCI having to deal with the extra latency involved. express lanes, SATA, USB, etc. Here, the layout of die matters. In the Zen2 layouts, the L3 cache that is of I.INTRODUCTION 32MB lies in the middle, which is separated into 2 parts of 16MB each with 4 cores on either side so, in In the world of computer performance, there is total, we get 32 MB of L3 cache with 8 total CPU competition between Intel and AMD processors and cores. both are having a large consumer base, which makes it If we look at the gen 3 architecture it's a little bit tricky to get unbiased advice about the best choice for different, we've got 32 MB of L3 cache just like the a processor. -

Intel's Tiger Lake 11Th Gen Core I7-1185G7 Review and Deep Dive

Intel’s Tiger Lake 11th Gen Core i7-1185G7 Review and Deep Dive: Baskin’ for the Exotic by Dr. Ian Cutress & Andrei Frumusanu on September 17, 2020 Contents 1. Tiger Lake: Playing with Toe Beans 2. 10nm Superfin, Willow Cove, Xe, and new SoC 3. New Instructions and Updated Security 4. Cache Architecture: The effect of increasing L2 and L3 5. Power Consumption: Intel’s TDP Shenanigans Hurts Everyone 6. Power Consumption: Comparing 15 W TGL to 28 W TGL 7. Power Consumption: Comparing 15 W TGL to 15 W ICL to15 W Renoir 8. CPU ST Performance: SPEC 2006, SPEC 2017 9. CPU MT Performance: SPEC 2006, SPEC 2017 10. CPU Performance: Office and Web 11. CPU Performance: Simulation and Science 12. CPU Performance: Encoding and Rendering 13. Xe-LP GPU Performance: Civilization 6 14. Xe-LP GPU Performance: Deus Ex Mankind Divided 15. Xe-LP GPU Performance: Final Fantasy XIV 16. Xe-LP GPU Performance: Final Fantasy XV 17. Xe-LP GPU Performance: World of Tanks 18. Xe-LP GPU Performance: F1 2019 19. Conclusion: Is Intel Smothering AMD in Sardine Oil? The big notebook launch for Intel this year is Tiger Lake, its upcoming 10nm platform designed to pair a new graphics architecture with a nice high frequency for the performance that customers in this space require. Over the past few weeks, we’ve covered the microarchitecture as presented by Intel at its latest Intel Architecture Day 2020, as well as the formal launch of the new platform in early September. The missing piece of the puzzle was actually testing it, to see if it can match the very progressive platform currently offered by AMD’s Ryzen Mobile. -

Cpus, Gpus, Accelerators and Memory.Pdf

CPUs, GPUs, accelerators and memory Andrea Sciabà On behalf of the Technology Watch WG HOW Workshop 18-22 March 2019 Jefferson Lab, Newport News Introduction • The goal of the presentation is to give a broad overview of the status and prospects of compute technologies – Intentionally, with a HEP computing bias • Focus on processors and accelerators – Not anymore just R&D, but soon to be used in production by LHC experiments • The wider purpose of the working group is to provide information that can be used to optimize investments – Market trends, price evolution • More detailed information is already available in a document – Soon to be added to the WG website 2 Outline • General market trends • CPUs – Intel, AMD – ARM – Specialized CPUs – Other architectures • GPUs • FPGAs • Interconnect, packaging and manufacturing technologies • Memory technologies 3 Semiconductor device market and trends • Global demand for semiconductors topped 1 trillion units shipped for the first time • Global semiconductor sales got off to a slow start in 2019, as year-to-year sales decreased • Long-term outlook remains promising, due to the ever-increasing semiconductor content in a range of consumer products • Strongest unit growth rates foreseen for components of – smartphones – automotive electronics systems – devices for deep learning applications 4 Semiconductor fabrication • Taiwan leading all regions/countries in wafer capacity • TSMC held 67% of Taiwan’s capacity and is leading • Samsung and SK Hynix represent 94% of the installed IC wafer capacity in -

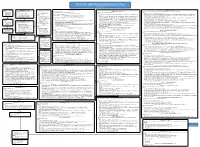

The Intel X86 Microarchitectures Map Version 3.2

The Intel x86 Microarchitectures Map Version 3.2 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P6 (1995, 0.50 to 0.35 μm) Skylake (2015, 14 nm) NetBurst (2000 , 180 to 130 nm) Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: i686 Alternative Names: SKL (Desktop and Mobile), SKX (Server) (Note : all U and Y processors are MCPs) P5 (1993, 0.80 to 0.35 μm) Alternative Names: Pentium 4, Pentium IV, P4 • 16-bit data bus: Series: Series: Pentium Pro (used in desktops and servers) Series: Alternative Names: Pentium, Series: 8086 (iAPX 86) • Desktop/Server: i386DX Variant: Klamath (1997, 0.35 μm) • Desktop: Desktop 6th Generation Core i5 (i5-6xxx, S-H) 80586, 586, i586 • Desktop: Pentium 4 1.x (except those with a suffix, Willamette, 180 nm), Pentium 4 2.0 (Willamette, 180 • 8-bit data bus: • Desktop lower-performance: i386SX Alternative Names: Pentium II, PII • Desktop higher-performance: Desktop 6th Generation Core i7 (i7-6xxx, S-H), Desktop 7th Generation Core i7 X (i7-7xxxX, X), Desktop 7th Series: nm) 8088 (iAPX 88) • Mobile: i386SL, 80376, i386EX, Series: Pentium II 233/266/300 steppings C0 and C1 (Klamath, used in desktops) Generation Core i9 X (i7-7xxxXE, i7-7xxxX, X), Desktop 9th Generation Core i7 X (i7-9xxxX, X, 14 nm++?), Desktop 9th Generation Core i9 X • Desktop/Server: P5, P54C • Desktop higher-performance: Pentium 4 1.xA (Northwood, 130 nm), Pentium 4 2.x (except 2.0, 2.40A, i386CXSA, i386SXSA, i386CXSB New instructions: Deschutes (1998, 0.25 to 0.18 μm) (i7-9xxxXE, i7-9xxxX, X, 14 nm++?), Xeon W-3175X (W, 14 nm++?) -

FORM 10-K (Mark One) ☑ ANNUAL REPORT PURSUANT to SECTION 13 OR 15(D) of the SECURITIES EXCHANGE ACT of 1934 for the Fiscal Year Ended December 26, 2020

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ☑ ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended December 26, 2020. or ☐ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to . Commission File Number 000-06217 INTEL CORPORATION (Exact name of registrant as specified in its charter) Delaware 94-1672743 (State or other jurisdiction of incorporation or organization) (I.R.S. Employer Identification No.) 2200 Mission College Boulevard, Santa Clara, California 95054-1549 (Address of principal executive offices) (Zip Code) Registrant’s telephone number, including area code (408) 765-8080 Securities registered pursuant to Section 12(b) of the Act: Title of each class Trading symbol Name of each exchange on which registered Common stock, $0.001 par value INTC Nasdaq Global Select Market Securities registered pursuant to Section 12(g) of the Act: None Indicate by check mark if the registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. Yes ☑ No ☐ Indicate by check mark if the registrant is not required to file reports pursuant to Section 13 or Section 15(d) of the Act. Yes ☐ No ☑ Indicate by check mark whether the registrant (1) has filed all reports required to be filed by Section 13 or 15(d) of the Securities Exchange Act of 1934 during the preceding 12 months (or for such shorter period that the registrant was required to file such reports), and (2) has been subject to such filing requirements for the past 90 days. -

CSE 141: Introduction to Computer Architecture

CSE 141: Introduction to Computer Architecture Advanced Pipelines CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 1 Part I: Exceptions • This is the last piece of what’s needed to make a “real” CPU useful CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 2 Exceptions • There are two sources of non-sequential control flow in a processor – explicit branch and jump instructions – exceptions • Branches are synchronous and deterministic • Exceptions are typically asynchronous and non-deterministic • Guess which is more difficult to handle? (recall: control flow refers to the movement of the program counter through memory) CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 3 Exceptions and Interrupts The terminology is not consistent, but we’ll refer to • exceptions as any unexpected change in control flow • interrupts as any externally-caused exception So then, what is: – arithmetic overflow – divide by zero – I/O device signals completion to CPU – user program invokes the OS – memory parity error – illegal instruction – timer signal CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 4 For now... • The machine we’ve been designing in class can generate two types of exceptions. – – CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 5 For now... • The machine we’ve been designing in class can generate two types of exceptions. – arithmetic overflow – illegal instruction • On an exception, we need to – save the PC (invisible to user code) -

Cpus, Gpus and Accelerators X86 Intel Server Micro-Architectures (1/2)

CPUs, GPUs and accelerators x86 Intel server micro-architectures (1/2) Microarchitecture Technology Launch year Highlights Skylake-SP 14nm 2017 Improved frontend and execution units More load/store bandwidth Improved hyperthreading AVX-512 Cascade Lake 14nm++ 2019 Vector Neural Network Instructions (VNNI) to improve inference performance Support 3D XPoint-based memory modules and Optane DC Security mitigations Cooper Lake 14nm++ 2020 bfloat16 (brain floating point format) S o Intel server micro-architectures (2/2) ur c e: Microarchitecture Technology Launch Highlights A CPU codename year n Sunny Cove 10nm+ 2019 Single threaded performance a Ice Lake Scalable New instructions n Tiger Lake? Improved scalability dt Larger L1, L2, μop caches and 2nd levele TLB More execution ports AVX-512 c h Willow Cove 10nm 2020? Cache redesign ? New transistor optimization Security Features Golden Cove 7/10nm? 2021? Single threaded performance ? AI Performance Networking/5G Performance Security Features Other Intel CPU architectures ● Intel Nervana AI Processor NNP-L-1000 (H2 2019-) ○ Accelerates AI inference for companies with high workload demands ○ Optimized across memory, bandwidth, utilization and power ○ Spring Crest 3-4x faster training than Lake Crest, introduced in 2017 ○ Supports bfloat16 ● Hybrid CPUs ○ Will be enabled by Foveros, the 3D chip stacking technology recently demonstrated ● Itanium ○ It will be finally discontinued in 2021 (the only remaining customer is HP) Other Intel-related news ● Record Q3 2018 results ○ Data-centric revenue -

Fast) Machines

Part II: The Fancy Stuff in Real (Fast) Machines CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 1 Pipelining in Today’s Most Advanced Processors • Not fundamentally different than the techniques we discussed • Deeper pipelines • Pipelining is combined with – superscalar execution – out-of-order execution – VLIW (very-long-instruction-word) CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 2 Deeper Pipelines • Power 4 • Pentium 3 Pentium 4 “Prescott” • Pentium 4 - Deeper still: 31 stages! - Planned for up to 5 GHz operation! (scrapped) CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 3 Superscalar Execution ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg ALU IM Reg DM Reg CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 4 What can this do in parallel? Selection A Any two instructions B Any two independent instructions C An arithmetic instruction and a memory instruction D Any instruction and a memory instruction CSE 141 E None of the aboveCC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 5 A modest superscalar MIPS • what can this machine do in parallel? • what other logic is required? • Represents earliest superscalar technology (eg, circa early 1990s) CSE 141 CC BY-NC-ND Pat Pannuto – Many slides adapted from Dean Tullsen 6 Superscalar Execution • To execute four instructions in the same cycle, we must -

Apple Silicon

Apple Silicon Fan 01/06/2021 Agenda ● An overview of Apple M1 SoC ○ Micro-architecture ○ Compatibility (from x86 to ARM) ● Why is Apple M1 so fast? ○ The cores ○ Unified Memory Architecture (UMA) ○ Rosetta 2 with Dual memory models ○ Apple Neural Engine (ANE) ● Security ○ Secure Enclave (T2 style) The Apple M1 SoC: An A14X for Macs ● First System on a Chip (SoC) for the Mac ● Unified memory architecture ● 8-core CPU ● 8-core GPU ● 16-core Apple Neural Engine ● Secure Enclave Micro-architecture ● Frees up die space by keeping the LPDDR4X DRAM close at hand ● 4 Firestorm performance cores ● 4 Icestorm efficiency cores ● Big GPU die size Compatibility (from x86 to ARM) Universal apps Universal apps support both Intel‑based and Apple silicon–based Mac systems. Rosetta 2 iPhone and iPad apps can directly run on Mac A binary translation software allows most x86 programs to be able to execute after an initial translation step. Why is Apple M1 so fast? Firestorm Cores (starting A14) Beat most Intel cores and almost beats the fastest AMD Ryzen cores ● Perform more instructions in a sequence faster. ● Perform lots of instructions in parallel. Refill the instruction buffer quickly relies on decoding code instruction into micro-ops. ● 4 decoders (Intel and AMD) vs. ● 8 decoders (Apple) Firestorm Cores (starting A14) A win for RISC vs. CISC ● Various length x86 instruction (1-15 bytes) ● Fixed length ARM instruction (4 bytes) Intel and AMD attempt to decode instructions at every possible starting point ● Convoluted and complicated decoder stage ● Hard to add more Twice as many instructions as AMD and Intel CPUs at the same clock frequency Firestorm Cores (starting A14) Huge out-of-order window ● Apple - 630 ROB ● Intel Sunny Cove and Willow Cove - 352 ROB ● AMD Zen3 - 256 ROB ● Arm Cortex-X1 - 224 ROB High ILP (Instruction level-parallelism) with many, many Execution Units. -

Notebooks (Preise Vom 19.3.21)

HP 14-ck0211ng Jet Black, Celeron N4000, 4GB RAM, 64GB SSD, DE (7GX57EA#ABD) Display 14", 1366x768, 112ppi, 60Hz, non-glare, IPS, 220cd/m² CPU Intel Celeron N4000, 2C/2T, 1.10-2.60GHz, 4MB Cache, 6W TDP, Codename "Gemini Lake" (Goldmont Plus, 14nm) RAM 4GB DDR4-2400 (1x 4GB Modul) SSD 64GB Flash (eMMC) HDD N/A Grafik Intel UHD Graphics 600 (iGPU), 12EU/96SP, 0.20-0.65GHz, Codename "Gemini Lake GT1" (Gen9.5) Betriebssystem Windows 10 Home 64bit Eingabe Tastatur mit DE-Layout (Rubber-Dome), Touchpad (2 abgesetzte Maustasten unten) Anschlüsse 1x HDMI 1.4b, 2x USB-A 3.0, 1x USB-A 2.0, 1x Gb LAN Wireless Wi-Fi 5 (WLAN 802.11a/b/g/n/ac, 1x1), Bluetooth 4.2, Miracast Authentifizierung N/A Webcam 0.9 Megapixel Cardreader SD-Card Optisches Laufwerk N/A Akku 1x Akku fest verbaut (Li-Ionen, 3 Zellen, 41Wh), 12.5h Laufzeit Gewicht 1.47kg Abmessungen (BxTxH) 335x234x20mm Farbe schwarz (Jet Black) 199,- € HP Chromebook 14 G5, Celeron N3350, 8GB RAM, 32GB Flash (3GJ74EA#ABD) Display 14", 1920x1080, 157dpi, 60Hz, non-glare, IPS, 220cd/m² CPU Intel Celeron N3350, 2x 1.10GHz RAM 8GB DDR4-2400 (8GB verlötet, nicht erweiterbar) HDD N/A SSD 32GB Flash (eMMC) Grafik Intel HD Graphics 500 (IGP) Anschlüsse 2x USB-C 3.0, 2x USB-A 3.0 Wireless WLAN 802.11a/b/g/n/ac (2x2, Intel 7265), Bluetooth 4.2 Akku 1x Akku fest verbaut (Li-Ionen, 2 Zellen, 47Wh), 10h Laufzeit Gewicht 1.54kg Betriebssystem Chrome OS Besonderheiten USB-C Ladeanschluss, Chrome Auto Update bis 06/2024 Eingabe Tastatur mit DE-Layout (beleuchtet, Rubber-Dome, spritzwassergeschützt), Touchpad Webcam 0.9 Megapixel Optisches Laufwerk N/A Cardreader microSD Abmessungen (BxTxH) 337x226x18mm Farbe grau Herstellergarantie ein Jahr 299,- € ASUS VivoBook Flip 14 TP412FA-EC363T Star Grey, Pentium Gold 5405U, 4GB RAM, 128GB SSD, DE Display 14", 1920x1080, 157ppi, 60Hz, Multi-Touch, glare, 250cd/m² CPU Intel Pentium Gold 5405U, 2C/4T, 2.30GHz, 2MB+0.5MB Cache, 15W TDP, Codename "Whiskey Lake-U" (Coffee Lake, 14nm++) RAM 4GB DDR4-2400 (4GB verlötet, 1 Slot, max.