Apple Silicon

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

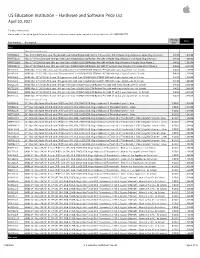

Apple US Education Price List

US Education Institution – Hardware and Software Price List April 30, 2021 For More Information: Please refer to the online Apple Store for Education Institutions: www.apple.com/education/pricelists or call 1-800-800-2775. Pricing Price Part Number Description Date iMac iMac with Intel processor MHK03LL/A iMac 21.5"/2.3GHz dual-core 7th-gen Intel Core i5/8GB/256GB SSD/Intel Iris Plus Graphics 640 w/Apple Magic Keyboard, Apple Magic Mouse 2 8/4/20 1,049.00 MXWT2LL/A iMac 27" 5K/3.1GHz 6-core 10th-gen Intel Core i5/8GB/256GB SSD/Radeon Pro 5300 w/Apple Magic Keyboard and Apple Magic Mouse 2 8/4/20 1,699.00 MXWU2LL/A iMac 27" 5K/3.3GHz 6-core 10th-gen Intel Core i5/8GB/512GB SSD/Radeon Pro 5300 w/Apple Magic Keyboard & Apple Magic Mouse 2 8/4/20 1,899.00 MXWV2LL/A iMac 27" 5K/3.8GHz 8-core 10th-gen Intel Core i7/8GB/512GB SSD/Radeon Pro 5500 XT w/Apple Magic Keyboard & Apple Magic Mouse 2 8/4/20 2,099.00 BR332LL/A BNDL iMac 21.5"/2.3GHz dual-core 7th-generation Core i5/8GB/256GB SSD/Intel IPG 640 with 3-year AppleCare+ for Schools 8/4/20 1,168.00 BR342LL/A BNDL iMac 21.5"/2.3GHz dual-core 7th-generation Core i5/8GB/256GB SSD/Intel IPG 640 with 4-year AppleCare+ for Schools 8/4/20 1,218.00 BR2P2LL/A BNDL iMac 27" 5K/3.1GHz 6-core 10th-generation Intel Core i5/8GB/256GB SSD/RP 5300 with 3-year AppleCare+ for Schools 8/4/20 1,818.00 BR2S2LL/A BNDL iMac 27" 5K/3.1GHz 6-core 10th-generation Intel Core i5/8GB/256GB SSD/RP 5300 with 4-year AppleCare+ for Schools 8/4/20 1,868.00 BR2Q2LL/A BNDL iMac 27" 5K/3.3GHz 6-core 10th-gen Intel Core i5/8GB/512GB -

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

Holiday Catalog

Brilliant for what’s next. With the power to achieve anything. AirPods Pro AppleCare+ Protection Plan†* $29 Key Features • Active Noise Cancellation for immersive sound • Transparency mode for hearing and connecting with the world around you • Three sizes of soft, tapered silicone tips for a customizable fit • Sweat and water resistant1 • Adaptive EQ automatically tunes music to the shape of your ear • Easy setup for all your Apple devices2 • Quick access to Siri by saying “Hey Siri”3 • The Wireless Charging Case delivers more than 24 hours of battery life4 AirPods Pro. Magic amplified. Noise nullified. Active Noise Cancellation for immersive sound. Transparency mode for hearing what’s happening around you. Sweat and water resistant.1 And a more customizable fit for all-day comfort. AirPods® AirPods AirPods Pro with Charging Case with Wireless Charging Case with Wireless Charging Case $159 $199 $249 1 AirPods Pro are sweat and water resistant for non-water sports and exercise and are IPX4 rated. Sweat and water resistance are not permanent conditions. The charging case is not sweat or water resistant. 2 Requires an iCloud account and macOS 10.14.4, iOS 12.2, iPadOS, watchOS 5.2, or tvOS 13.2 or later. 3Siri may not be available in all languages or in all areas, and features may vary by area. 4 Battery life varies by use and configuration. See apple.com/batteries for details. Our business is part of a select group of independent Apple® Resellers and Service Providers who have a strong commitment to Apple’s Mac® and iOS platforms and have met or exceeded Apple’s highest training and sales certifications. -

Apple Accessories & Prices Input Devices Apple Magic Mouse 2 (APPX333) £65.50 Imac, Mac Mini and Accessories Magic Mouse 2 - Space Grey (APPX015) £82.50

Apple Accessories & Prices Input Devices Apple Magic Mouse 2 (APPX333) £65.50 iMac, Mac Mini and Accessories Magic Mouse 2 - Space Grey (APPX015) £82.50 Magic Trackpad 2 (APPX335) £107.50 Magic Trackpad 2 - Space Grey (APPX016) £124.00 Magic Keyboard (APPK005) £79.95 Magic Keyboard - Numeric (APPK006) £105.00 Magic Keyboard - Numeric - Space Grey (APPK007) £124.00 Adapters and Network Mini DisplayPort to DVI Adapter (APPX117) £23.95 Mini DisplayPort to VGA Adapter (APPX142) £23.95 USB-C to USB-A (APPX281) £14.95 USB-C to Digital AV (APPX099) £62.50 Misc. Accessories USB Retina Superdrive (APPX228) £65.50 HomePod Mini Smart Speakers - Available in Space Grey and Silver (APPX137/138) £82.50 HomePod Smart Speakers - Available in Space Grey and Silver (APPX013/014) £232.50 Many other adapters and accessories also available! Guernsey33 Commercial Arcade, Computers St. Peter Port Tel 01481-728738 Ltd E. & O. E. 18th August 2021 Mac Products & Specifications Mac Products & Specifications Mac Mini - i5 2.6GHz (APPC022) £915.00 iMac 27” i5 3.1GHz - 5K Retina Display (APPC028) £1499.00 3.0GHz 6-Core i5 Processor w/ 9MB shared L3 cache - Turbo Boost 3.1GHz 6-Core i5 Processor (Turbo Boost up to 4.5GHz), 8GB up to 4.1GHz, 8GB DDR4 RAM, 256GB Solid State Drive, Intel UHD DDR4 RAM, 256GB Solid State Drive, Radeon Pro 5300 Graphics Graphics 630, 802.11ac Wi-Fi (802.11 a/b/g/n compatible) & Bluetooth 5.0 (4GB), 802.11ac Wi-Fi (802.11 a/b/g/n compatible) & Bluetooth 5.0 Mac Mini - M1 8-Core Processor (APPC031) £582.00 iMac 27” i5 3.3GHz - 5K Retina Display -

Tinkertool System 7 Reference Manual Ii

Documentation 0642-1075/2 TinkerTool System 7 Reference Manual ii Version 7.5, August 24, 2021. US-English edition. MBS Documentation 0642-1075/2 © Copyright 2003 – 2021 by Marcel Bresink Software-Systeme Marcel Bresink Software-Systeme Ringstr. 21 56630 Kretz Germany All rights reserved. No part of this publication may be redistributed, translated in other languages, or transmitted, in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of the publisher. This publication may contain examples of data used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental. This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. The publisher may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice. Make sure that you are using the correct edition of the publication for the level of the product. The version number can be found at the top of this page. Apple, macOS, iCloud, and FireWire are registered trademarks of Apple Inc. Intel is a registered trademark of Intel Corporation. UNIX is a registered trademark of The Open Group. Broadcom is a registered trademark of Broadcom, Inc. Amazon Web Services is a registered trademark of Amazon.com, Inc. -

2021 Proxy Statement

2021 Proxy Statement Notice of Annual Stockholders’ Meeting Investor Engagement To see how we responded to your Who We Met With feedback, see page 41. Total Contacted Total Engaged Director Engaged 50.4% 39.5% 29.7% O/S O/S O/S Intel’s outstanding shares (o/s) caculated as of September 30,2020 We are proud of our long-standing and robust investor engagement program. Our integrated outreach team, led by our Investor Relations group, Corporate Responsibility office, Human Resources office, and Corporate Secretary office, engages proactively with our stockholders, maintaining a two-way, year-round governance calendar as shown in this graphic. During 2020, our engagement program addressed our executive compensation program, corporate governance best practices, our Board’s operation and experience, and our commitment to addressing environmental and social responsibility issues that are critical to our business. Through direct participation in our engagement efforts and through briefings from our engagement teams, our directors are able to monitor developments in corporate governance and social responsibility and benefit from our stockholders’ perspectives on these topics. In consultation with our Board, we seek to thoughtfully adopt and apply developing practices in a manner that best supports our business and our culture. Summer Winter Review annual meeting Incorporate input results to determine from investor meetings Annual appropriate next into annual meeting planning steps, and prioritize and enhance governance Stockholders’ post annual meeting and compensation investor engagement practices and disclosures Meeting focus areas when warranted Fall Spring Hold post- Conduct pre-annual annual meeting meeting investor meetings investor meetings to solicit feedback and report to the to answer questions and Board, Compensation understand investor Committee, and Corporate views on proxy Governance and Nominating matters Committee Additional detail on specific topics and initiatives we have adopted is discussed under “Investor Engagement” on page 40. -

In-Datacenter Performance Analysis of a Tensor Processing Unit

In-Datacenter Performance Analysis of a Tensor Processing Unit Presented by Josh Fried Background: Machine Learning Neural Networks: ● Multi Layer Perceptrons ● Recurrent Neural Networks (mostly LSTMs) ● Convolutional Neural Networks Synapse - each edge, has a weight Neuron - each node, sums weights and uses non-linear activation function over sum Propagating inputs through a layer of the NN is a matrix multiplication followed by an activation Background: Machine Learning Two phases: ● Training (offline) ○ relaxed deadlines ○ large batches to amortize costs of loading weights from DRAM ○ well suited to GPUs ○ Usually uses floating points ● Inference (online) ○ strict deadlines: 7-10ms at Google for some workloads ■ limited possibility for batching because of deadlines ○ Facebook uses CPUs for inference (last class) ○ Can use lower precision integers (faster/smaller/more efficient) ML Workloads @ Google 90% of ML workload time at Google spent on MLPs and LSTMs, despite broader focus on CNNs RankBrain (search) Inception (image classification), Google Translate AlphaGo (and others) Background: Hardware Trends End of Moore’s Law & Dennard Scaling ● Moore - transistor density is doubling every two years ● Dennard - power stays proportional to chip area as transistors shrink Machine Learning causing a huge growth in demand for compute ● 2006: Excess CPU capacity in datacenters is enough ● 2013: Projected 3 minutes per-day per-user of speech recognition ○ will require doubling datacenter compute capacity! Google’s Answer: Custom ASIC Goal: Build a chip that improves cost-performance for NN inference What are the main costs? Capital Costs Operational Costs (power bill!) TPU (V1) Design Goals Short design-deployment cycle: ~15 months! Plugs in to PCIe slot on existing servers Accelerates matrix multiplication operations Uses 8-bit integer operations instead of floating point How does the TPU work? CISC instructions, issued by host. -

Lecture Note 7. IA: History and Features

System Programming Lecture Note 7. IA: History and Features October 30, 2020 Jongmoo Choi Dept. of Software Dankook University http://embedded.dankook.ac.kr/~choijm (Copyright © 2020 by Jongmoo Choi, All Rights Reserved. Distribution requires permission) Objectives Discuss Issues on ISA (Instruction Set Architecture) ü Opcode and operand addressing modes Apprehend how ISA affects system program ü Context switch, memory alignment, stack overflow protection Describe the history of IA (Intel Architecture) Grasp the key technologies in recent IA ü Pipeline and Moore’s law Refer to Chapter 3, 4 in the CSAPP and Intel SW Developer Manual 2 Issues on ISA (1/2) Consideration on ISA (Instruction Set Architecture) asm_sum: addl $1, %ecx movl -4(%ebx, %ebp, 4), %eax call func1 leave ü opcode issues § how many? (add vs. inc è RISC vs. CISC) § multi functions? (SISD vs. SIMD vs. MIMD …) ü operand issues § fixed vs. variable operands f bits n bits n bits n bits § fixed: how many? opcode operand 1 operand 2 operand 3 § operand addressing modes f bits n bits n bits ü performance issues opcode operand 1 operand 2 § pipeline f bits n bits § superscalar opcode operand 1 § multicore 3 Issues on ISA (2/2) Features of IA (Intel Architecture) ü Basically CISC (Complex Instruction Set Computing) § Variable length instruction § Variable number of operands (0~3) § Diverse operand addressing modes § Stack based function call § Supporting SIMD (Single Instruction Multiple Data) ü Try to take advantage of RISC (Reduced Instruction Set Computing) § Micro-operations -

Apple Branded 20210331

Apple Inc. Please visit the Apple NASPO online store for current product pricing, availability and product information. Consumer MNWNC- Band Part Number Description (MSRP) 102 iMac iMac 21.5"/2.3GHz dual-core 7th-gen Intel Core i5/8GB/256GB SSD/Intel Iris Plus Graphics 640 w/Apple Magic Keyboard, Apple Magic Mouse 1 MHK03LL/A 2 1,099.00 1,049.00 1 MHK23LL/A iMac 21.5" 4K/3.6GHz quad-core 8th-gen Intel Core i3/8GB/256GB SSD/Radeon Pro 555X w/Apple Magic Keyboard and Apple Magic Mouse 2 1,299.00 1,249.00 1 MHK33LL/A iMac 21.5" 4K/3.0GHz 6-core 8th-gen Intel Core i5/8GB/256GB SSD/Radeon Pro 560X w/Apple Magic Keyboard and Apple Magic Mouse 2 1,499.00 1,399.00 1 MXWT2LL/A iMac 27" 5K/3.1GHz 6-core 10th-gen Intel Core i5/8GB/256GB SSD/Radeon Pro 5300 w/Apple Magic Keyboard and Apple Magic Mouse 2 1,799.00 1,699.00 1 MXWU2LL/A iMac 27" 5K/3.3GHz 6-core 10th-gen Intel Core i5/8GB/512GB SSD/Radeon Pro 5300 w/Apple Magic Keyboard & Apple Magic Mouse 2 1,999.00 1,899.00 1 MXWV2LL/A iMac 27" 5K/3.8GHz 8-core 10th-gen Intel Core i7/8GB/512GB SSD/Radeon Pro 5500 XT w/Apple Magic Keyboard & Apple Magic Mouse 2 2,299.00 2,099.00 1 BR332LL/A BNDL iMac 21.5"/2.3GHz dual-core 7th-generation Core i5/8GB/256GB SSD/Intel IPG 640 with 3-year AppleCare+ for Schools - 1,168.00 1 BR342LL/A BNDL iMac 21.5"/2.3GHz dual-core 7th-generation Core i5/8GB/256GB SSD/Intel IPG 640 with 4-year AppleCare+ for Schools - 1,218.00 1 BR3G2LL/A BNDL iMac 21.5" 4K/3.6GHz quad-core 8th-gen Intel Core i3/8GB/256GB SSD/Radeon Pro 555X with 3-year AppleCare+ for Schools - 1,368.00 -

Confirm the Logitech Slim Combo Case Connection to Confirm That Your Slim Combo Keyboard Is Properly Connected Using the Smart Connector, Do the Following

FAQs Confirm the Logitech Slim Combo case connection To confirm that your Slim Combo keyboard is properly connected using the Smart Connector, do the following: 1. Go to Settings on your iPad. 2. Tap on About Device. 3. In the legal information section, you should see the Slim Combo. If you don’t see the Slim Combo, then it's not properly connected. Logitech Slim Combo case does not connect to iPad If your Slim Combo case won’t connect to your iPad Pro, check the following: 1. Make sure the iOS on your iPad Pro is updated to the latest version. 2. Disconnect the keyboard and then attempt to reconnect it to your iPad Pro. 3. Make sure there’s no dust around the Smart Connector. 4. Restart your iPad Pro. Shortcut keys on the Logitech Slim Combo keyboard The following shortcut and media keys are available on the Slim Combo keyboard: Key Description Home iPad screen brightness down iPad screen brightness up iPad search field On-screen keyboard Key backlighting level down Key backlighting level up Media control : Previous Media control : Play Media control : Next Volume control : Mute Volume control : Down Key Description Volume control : Up iPad Lock Frequently asked questions regarding Logitech products comparable to Slim Combo Logitech makes other iPad cases in addition to the Slim Combo. If your iPad isn’t compatible with the Slim Combo, check below for other Logitech products that may suit your needs. In addition to the Slim Combo, are there similar devices that are compatible with the iPad Pro 12.9 and 10.5-inch tablets? Slim Combo exists only for the latest models of iPad Pro. -

The American Express® Card Membership Rewards® 2021 Catalogue WHAT's INSIDE Select Any Icon to Go to Desired Section

INCENTIVO The American Express® Card Membership Rewards® 2021 Catalogue WHAT'S INSIDE Select any icon to go to desired section THE MEMBERSHIP REWARDS® PROGRAM FREQUENT TRAVELER OPTION FREQUENT GUEST FREQUENT FLYER PROGRAM PROGRAM NON-FREQUENT TRAVELER OPTION GADGETS & HOME & TRAVEL HEALTH & ENTERTAINMENT KITCHEN ESSENTIALS WELLNESS DINING HEALTH & WELLNESS LUXURY HOTEL SHOPPING VOUCHERS VOUCHERS VOUCHERS VOUCHERS FINANCIAL REWARDS TERMS & CONDITIONS THE MEMBERSHIP REWARDS PROGRAM THE MEMBERSHIP REWARDS PROGRAM TAKES YOU FURTHER NON-EXPIRING MEMBERSHIP REWARDS® POINTS Your Membership Rewards® Points do not expire, allowing you to save your Membership Rewards® Points for higher 1 value rewards. ACCELERATED REWARDS REDEMPTION Membership Rewards® Points earned from your Basic and Supplementary Cards are automatically pooled to enable 2 accelerated redemption. COMPREHENSIVE REWARDS PROGRAM The Membership Rewards® Points can be redeemed for a wide selection of shopping gift certificates, dining vouchers, 3 gadgets, travel essential items and more. The Membership Rewards® Points can also be transferred to other loyalty programs such as Airline Frequent Flyer and Hotel Frequent Guest Rewards programs which will allow you to enjoy complimentary flights or hotel stays. *Select any item below to go to the desired section. THE FREQUENT NON- MEMBERSHIP FREQUENT FINANCIAL TERMS & TRAVELER CONDITIONS REWARDS OPTION TRAVELER REWARDS PROGRAM OPTION THE MEMBERSHIP REWARDS PROGRAM PROGRAM OPTIONS AND STRUCTURE Earn one (1) Membership Rewards® Point for every -

Advancement in Processor's Architecture

© June 2021| IJIRT | Volume 8 Issue 1 | ISSN: 2349-6002 Advancement In Processor’s Architecture Avinash Maurya1, Prachi Mishra2, Prateek Choudhary3, Prashant Upadhyay4 1,2,3,4 Student of Information Technology, RKGIT, Ghaziabad, India Abstract - AMD has launched its next-gen Zen 3 lineup physical layout perspective. The Zen2 AMD Ryzen CPU which makes it the best and most powerful processor series had a big improvement in architecture commercial CPU series. as they moved from 12/14nm processors to 7nm The "Zen 3" core architecture delivers a 19% increase architecture manufactured by TSMC (Taiwan in the instructions per clock for the Ryzen 5600x, 5800x, Semiconductor Manufacturing Company). 5900x, and 5950x. This is a significant modification in the last decade that The 2nd Gen AMD Ryzen processor's which is there happened due to the improvement in core architecture, in the AMD Ryzen 7 3700x has one compute die with which results in full access of the L3 cache without 8 cores and one input/output die that handles PCI having to deal with the extra latency involved. express lanes, SATA, USB, etc. Here, the layout of die matters. In the Zen2 layouts, the L3 cache that is of I.INTRODUCTION 32MB lies in the middle, which is separated into 2 parts of 16MB each with 4 cores on either side so, in In the world of computer performance, there is total, we get 32 MB of L3 cache with 8 total CPU competition between Intel and AMD processors and cores. both are having a large consumer base, which makes it If we look at the gen 3 architecture it's a little bit tricky to get unbiased advice about the best choice for different, we've got 32 MB of L3 cache just like the a processor.