Introduction

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1332 Nippon Suisan Kaisha, Ltd. 50 1333 Maruha Nichiro Corp. 500 1605 Inpex Corp

Nikkei Stock Average - Par Value (Update:August/1, 2017) Code Company Name Par Value(Yen) 1332 Nippon Suisan Kaisha, Ltd. 50 1333 Maruha Nichiro Corp. 500 1605 Inpex Corp. 125 1721 Comsys Holdings Corp. 50 1801 Taisei Corp. 50 1802 Obayashi Corp. 50 1803 Shimizu Corp. 50 1808 Haseko Corp. 250 1812 Kajima Corp. 50 1925 Daiwa House Industry Co., Ltd. 50 1928 Sekisui House, Ltd. 50 1963 JGC Corp. 50 2002 Nisshin Seifun Group Inc. 50 2269 Meiji Holdings Co., Ltd. 250 2282 Nh Foods Ltd. 50 2432 DeNA Co., Ltd. 500/3 2501 Sapporo Holdings Ltd. 250 2502 Asahi Group Holdings, Ltd. 50 2503 Kirin Holdings Co., Ltd. 50 2531 Takara Holdings Inc. 50 2768 Sojitz Corp. 500 2801 Kikkoman Corp. 50 2802 Ajinomoto Co., Inc. 50 2871 Nichirei Corp. 100 2914 Japan Tobacco Inc. 50 3086 J.Front Retailing Co., Ltd. 100 3099 Isetan Mitsukoshi Holdings Ltd. 50 3101 Toyobo Co., Ltd. 50 3103 Unitika Ltd. 50 3105 Nisshinbo Holdings Inc. 50 3289 Tokyu Fudosan Holdings Corp. 50 3382 Seven & i Holdings Co., Ltd. 50 3401 Teijin Ltd. 250 3402 Toray Industries, Inc. 50 3405 Kuraray Co., Ltd. 50 3407 Asahi Kasei Corp. 50 3436 SUMCO Corp. 500 3861 Oji Holdings Corp. 50 3863 Nippon Paper Industries Co., Ltd. 500 3865 Hokuetsu Kishu Paper Co., Ltd. 50 4004 Showa Denko K.K. 500 4005 Sumitomo Chemical Co., Ltd. 50 4021 Nissan Chemical Industries, Ltd. 50 4042 Tosoh Corp. 50 4043 Tokuyama Corp. 50 WF-101-E-20170803 Copyright © Nikkei Inc. All rights reserved. 1/5 Nikkei Stock Average - Par Value (Update:August/1, 2017) Code Company Name Par Value(Yen) 4061 Denka Co., Ltd. -

Sanyo Trading Co., Ltd. Sun Phoenix Mexico SA De CV

Sanyo Trading Co., Ltd. Sun Phoenix Mexico S.A. de C.V. Company profile 2021/Mar. Corporate Profile Head Office : 2-11, Kanda Nishikicho, Chiyoda-ku, Tokyo Establshed : May 28, 1947(2013/Oct TSE listed: 3176) Capital : US$ 10.0 M Sales(Consolidated) : US$ 832 M(2019/Sep) Employee : 368 (2019/Sep.) Business Groups : Rubber Chemical Machinery & Materials Scientific Instruments Industrial Products Branch : Osaka/Nagoya/Hiroshima office(Japan) Branch : <Americas> New York/Detroit/Irapuato (Mexico) office(Global) <Europe> Dusseldorf <Asia> Shanghai/Tianjin/Guangzhou/Hong Kong/ Bangkok/Ho Chi Minh/Hanoi/Jakarta/Singapore Gurgaon (India) Sun Phoenix Mexico 2. Sun Phoenix Company Profile Comapan : Sun Phoenix México, S.A. de C.V. y N a m e Location : Irapuato, Guanajuato, Mexico President : Yu Kashiki Establish : October, 2013 C a p i t a l : 12 Million Pesos (Sanyo Trading95%, SCOA 5%) Employee : 8 N u m b e r Rubber Business Group -Started import of Synthetic Rubber from Polymer Corporation, Canada in 1952 P r o d u c t : Synthetic Rubber - Rubber: ENR, SBR, RNR, RBR, ECO, ACM, EPDM; etc Rubber Additive - Blowing Agents Oil sealing - Curing agents, Activator, Hose for Automotive Industrial rubber Retardant Agents, Accelerators products materials Engineering plastic - Nylon PA6 / PA66 - PP, ABS, POM, PBT; etc - TPE, TPO Compound - PVC S u p p l i e r : Lanxess (Germany), Rubber Products KaMin (USA), Eiwa Chemical (USA) AF Supercell (Thai) C u s t o m e r : Orotex, Parker Corporation, Molten, Nishikawa Sealing System, Sumitomo Chemical, Mitsui -

Highlights of Major General Chemical Manufacturers' Financial Results for Fiscal Year Ended March 2021

21-D-0223 June 7, 2021 Highlights of Major General Chemical Manufacturers’ Financial Results for Fiscal Year Ended March 2021 The following are Japan Credit Rating Agency, Ltd. (JCR)’s perception of the current status and highlights for rating concerning the financial results for the fiscal year ended March 2021 (FY2020) and earnings forecasts for FY2021 of Japan’s 7 general chemical manufacturers: ASAHI KASEI CORPORATION, Showa Denko K.K. (with January-December accounting period), SUMITOMO CHEMICAL COMPANY, LIMITED, TOSOH CORPORATION, Mitsui Chemicals, Inc., Mitsubishi Chemical Holdings Corporation (“Mitsubishi Chemical HD”) and Ube Industries, Ltd. 1. Industry Trend In recent years, business environment of chemical industry has been somewhat severe. Since 2018, trade friction between the U.S. and China has been a negative factor, and in 2020, the COVID-19 pandemic broke out. The COVID-19 pandemic has had a significant negative impact on social and economic activities around the world. Although uncertainty about the future of economic trend has lessened compared to the time when the pandemic broke out, the containment cannot still be foreseen. With regard to bulk chemicals, average utilization rate of domestic ethylene centers in fiscal 2020 was 93.9% (compared to an average of 94.2% in fiscal 2019), falling below the full utilization level of 95% for the second consecutive year. However, the monthly capacity utilization rate hovered around 90% in the first half of the fiscal year, but began to pick up in the second half, with some months exceeding 95%. In addition to recoveries in consumer activity and demand for downstream products, recent cold wave in the U.S. -

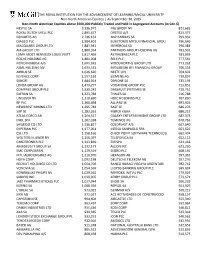

The Royal Institution for the Advancement

THE ROYAL INSTITUTION FOR THE ADVANCEMENT OF LEARNING/McGILL UNIVERSITY Non-North American Equities │ As September 30, 2019 Non-North American Equities above $500,000 Publicly Traded and Held in Segregated Accounts (in Cdn $) NESTLE SA 3,136,972 ING GROEP NV 822,665 ROYAL DUTCH SHELL PLC 2,895,677 ORSTED A/S 813,377 NOVARTIS AG 2,736,152 BNP PARIBAS SA 799,331 DIAGEO PLC 1,984,601 SUMITOMO MITSUI FINANCIAL GROU 796,646 MACQUARIE GROUP LTD 1,881,942 IBERDROLA SA 796,483 AIA GROUP LTD 1,880,954 PARTNERS GROUP HOLDING AG 781,932 LVMH MOET HENNESSY LOUIS VUITT 1,817,469 ASTRAZENECA PLC 781,059 ROCHE HOLDING AG 1,801,008 RELX PLC 777,561 NOVO NORDISK A/S 1,695,931 WOOLWORTHS GROUP LTD 771,262 ASML HOLDING NV 1,633,531 MITSUBISHI UFJ FINANCIAL GROUP 766,553 AIRBUS SE 1,626,620 NESTE OYJ 764,602 KEYENCE CORP 1,557,193 SIEMENS AG 739,857 SANOFI 1,484,014 DANONE SA 733,193 LONZA GROUP AG 1,479,277 VODAFONE GROUP PLC 723,852 COMPASS GROUP PLC 1,339,242 DASSAULT SYSTEMES SE 720,751 SAFRAN SA 1,323,784 THALES SA 716,788 UNILEVER NV 1,319,690 HSBC HOLDINGS PLC 707,830 BP PLC 1,300,498 ALLIANZ SE 693,905 NEWCREST MINING LTD 1,295,783 BASF SE 686,276 SAP SE 1,283,261 MERCK KGAA 686,219 ATLAS COPCO AB 1,264,517 GALAXY ENTERTAINMENT GROUP LTD 683,373 ENEL SPA 1,262,338 TEMENOS AG 670,763 SHISEIDO CO LTD 1,236,827 COLOPLAST A/S 667,640 EXPERIAN PLC 1,177,061 INTESA SANPAOLO SPA 663,622 CSL LTD 1,158,166 CHECK POINT SOFTWARE TECHNOLOG 662,404 WOLTERS KLUWER NV 1,156,397 TELEFONICA SA 652,113 CARDTRONICS PLC 1,143,839 ENI SPA 641,418 AMADEUS IT GROUP SA -

1332:Xtks Nippon Suisan Kaisha Ltd 3 4 1 1334:Xtks Maruha Nichiro Holdings Inc. 3 4 1 1377:Xtks Sakata Seed Corp. 3 5 2 1414:Xtks SHO-BOND Holdings Co

Symbol Code Description Current Rating New rating Diff 1332:xtks Nippon Suisan Kaisha Ltd 3 4 1 1334:xtks Maruha Nichiro Holdings Inc. 3 4 1 1377:xtks Sakata Seed Corp. 3 5 2 1414:xtks SHO-BOND Holdings Co. Ltd 3 6 3 1766:xtks TOKEN Corp. 3 6 3 1801:xtks Taisei Corp. 3 5 2 1803:xtks Shimizu Corp. 3 4 1 1808:xtks Haseko Corp. 3 4 1 1812:xtks Kajima Corp. 3 5 2 1820:xtks Nishimatsu Construction Co. Ltd 3 6 3 1824:xtks Maeda Corp. 3 6 3 1833:xtks Okumura Corp. 3 6 3 1860:xtks Toda Corp. 3 5 2 1861:xtks Kumagai Gumi Co. Ltd 3 8 5 1865:xtks Asunaro Aoki Construction Co. Ltd 3 6 3 1870:xtks Yahagi Construction Co. Ltd 3 4 1 1881:xtks NIPPO Corp. 3 6 3 1883:xtks Maeda Road Construction Co. Ltd 3 6 3 1911:xtks Sumitomo Forestry Co Ltd 3 4 1 1924:xtks PanaHome Corp. 3 4 1 1925:xtks Daiwa House Industry Co. Ltd 3 4 1 1928:xtks Sekisui House Ltd 3 4 1 1934:xtks YURTEC Corp. 3 6 3 1945:xtks Tokyo Energy & Systems Inc. 3 4 1 1961:xtks Sanki Engineering Co. Ltd 3 4 1 1963:xtks JGC Corporation 3 4 1 1968:xtks Taihei Dengyo Kaisha Ltd 3 4 1 1969:xtks Takasago Thermal Engineering Co. Ltd 3 4 1 1973:xtks NEC Networks & System Integration Corp. 3 5 2 1979:xtks Taikisha Ltd 3 4 1 1983:xtks TOSHIBA PLANT SYSTEMS & SERVICES Corp. -

Tskgel® SW-Type Column Guide for Size Exclusion HPLC

TSKgel® SW-type Column Guide For Size Exclusion HPLC Setting the standard in SEC since 1977, with new columns optimized for your applications. Please contact your Fisher Scientific Representative for more information. About Tosoh Bioscience Tosoh Bioscience LLC is a major supplier of chromatography products. Located in King of Prussia, PA, Tosoh Bioscience provides sales and service to pharmaceutical and biotechnology customers in North and South America. European operations are in Griesheim, Germany, while Asia is served by Tosoh Corporation in Tokyo, Japan, Shanghai, China and Singapore. Tosoh’s portfolio of over 500 specialty products encompasses all common modes of liquid chromatography, and coupled with our expertise, we can help you purify any protein, peptide, enzyme, nucleic acid, antibiotic, or small molecule. In addition to our extensive line of analytical HPLC columns, Tosoh provides bulk chromatographic resins for the purification of biopharmaceutical drugs in commercial manufacturing processes. Our TOYOPEARL® and TSKgel® chromatographic resins and TSKgel columns are renowned for their quality and reliability. The EcoSEC® GPC system, introduced in the U.S. in 2008 and a market leader in Japan for more than thirty years, is a top-of-the-line dedicated gel permeation chromatography instrument for the analysis of polymers in organic and aqueous/organic solvents. TSKgel SW-type columns are the industry standard for size exclusion chromatography of proteins. Our expertise in size exclusion chromatography is based on a fundamental understanding of the role played by pore diameter and molecular size in chromatographic separations. This knowledge, coupled with a thorough understanding of transport phenomena and wide-ranging experience in polymer chemistry and surface modifications, allows us to design higher performance polymeric resins for other modes of chromatography, including ion exchange, hydrophobic interaction, affinity, and reversed phase. -

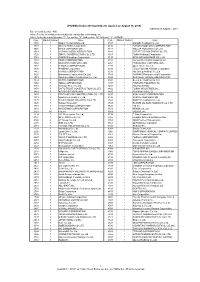

JPX-Nikkei Index 400 Constituents (Applied on August 31, 2021) Published on August 6, 2021 No

JPX-Nikkei Index 400 Constituents (applied on August 31, 2021) Published on August 6, 2021 No. of constituents : 400 (Note) The No. of constituents is subject to change due to de-listing. etc. (Note) As for the market division, "1"=1st section, "2"=2nd section, "M"=Mothers, "J"=JASDAQ. Code Market Divison Issue Code Market Divison Issue 1332 1 Nippon Suisan Kaisha,Ltd. 3048 1 BIC CAMERA INC. 1417 1 MIRAIT Holdings Corporation 3064 1 MonotaRO Co.,Ltd. 1605 1 INPEX CORPORATION 3088 1 Matsumotokiyoshi Holdings Co.,Ltd. 1719 1 HAZAMA ANDO CORPORATION 3092 1 ZOZO,Inc. 1720 1 TOKYU CONSTRUCTION CO., LTD. 3107 1 Daiwabo Holdings Co.,Ltd. 1721 1 COMSYS Holdings Corporation 3116 1 TOYOTA BOSHOKU CORPORATION 1766 1 TOKEN CORPORATION 3141 1 WELCIA HOLDINGS CO.,LTD. 1801 1 TAISEI CORPORATION 3148 1 CREATE SD HOLDINGS CO.,LTD. 1802 1 OBAYASHI CORPORATION 3167 1 TOKAI Holdings Corporation 1803 1 SHIMIZU CORPORATION 3231 1 Nomura Real Estate Holdings,Inc. 1808 1 HASEKO Corporation 3244 1 Samty Co.,Ltd. 1812 1 KAJIMA CORPORATION 3254 1 PRESSANCE CORPORATION 1820 1 Nishimatsu Construction Co.,Ltd. 3288 1 Open House Co.,Ltd. 1821 1 Sumitomo Mitsui Construction Co., Ltd. 3289 1 Tokyu Fudosan Holdings Corporation 1824 1 MAEDA CORPORATION 3291 1 Iida Group Holdings Co.,Ltd. 1860 1 TODA CORPORATION 3349 1 COSMOS Pharmaceutical Corporation 1861 1 Kumagai Gumi Co.,Ltd. 3360 1 SHIP HEALTHCARE HOLDINGS,INC. 1878 1 DAITO TRUST CONSTRUCTION CO.,LTD. 3382 1 Seven & I Holdings Co.,Ltd. 1881 1 NIPPO CORPORATION 3391 1 TSURUHA HOLDINGS INC. 1893 1 PENTA-OCEAN CONSTRUCTION CO.,LTD. -

Portfolio of Investments

PORTFOLIO OF INVESTMENTS Variable Portfolio – Partners International Value Fund, September 30, 2020 (Unaudited) (Percentages represent value of investments compared to net assets) Investments in securities Common Stocks 97.9% Common Stocks (continued) Issuer Shares Value ($) Issuer Shares Value ($) Australia 4.2% UCB SA 3,232 367,070 AMP Ltd. 247,119 232,705 Total 13,350,657 Aurizon Holdings Ltd. 64,744 199,177 China 0.6% Australia & New Zealand Banking Group Ltd. 340,950 4,253,691 Baidu, Inc., ADR(a) 15,000 1,898,850 Bendigo & Adelaide Bank Ltd. 30,812 134,198 China Mobile Ltd. 658,000 4,223,890 BlueScope Steel Ltd. 132,090 1,217,053 Total 6,122,740 Boral Ltd. 177,752 587,387 Denmark 1.9% Challenger Ltd. 802,400 2,232,907 AP Moller - Maersk A/S, Class A 160 234,206 Cleanaway Waste Management Ltd. 273,032 412,273 AP Moller - Maersk A/S, Class B 3,945 6,236,577 Crown Resorts Ltd. 31,489 200,032 Carlsberg A/S, Class B 12,199 1,643,476 Fortescue Metals Group Ltd. 194,057 2,279,787 Danske Bank A/S(a) 35,892 485,479 Harvey Norman Holdings Ltd. 144,797 471,278 Demant A/S(a) 8,210 257,475 Incitec Pivot Ltd. 377,247 552,746 Drilling Co. of 1972 A/S (The)(a) 40,700 879,052 LendLease Group 485,961 3,882,083 DSV PANALPINA A/S 15,851 2,571,083 Macquarie Group Ltd. 65,800 5,703,825 Genmab A/S(a) 1,071 388,672 National Australia Bank Ltd. -

Facilitation of Information Transfer on Chemicals in Products

Facilitation of Information Transfer on Chemicals in Products The Ministry of Economy, Trade and Industry (METI) developed ‘chemSHERPA’ [kémʃéərpə] as a new information transfer scheme for chemicals in products throughout their supply chains. METI hopes that the dissemination of chemSHERPA may contribute to reduce the workload of both providers and recipients of the information. From the beginning of the development of chemSHERPA, METI has been in communication with international bodies such as the IEC and the IPC, etc., with the aim of developing chemSHERPA into not only a Japanese standard but also an International standard. To make it a de-facto standard, METI has introduced this scheme to international organizations and governments of other countries for their active use. The Joint Article Management Promotion Consortium (JAMP) is a governing body for chemSHERPA from April 2016 and see a shift to chemSHERPA. We believe many companies are preparing towards implementing chemSHERPA. Based on the efforts mentioned above, the following companies and company groups have agreed with the dissemination of chemSHERPA, and METI will continue to work with JAMP and companies to spread the use of chemSHERPA to internal as well as external supply chains as needed.(Please contact us if any company or company group has interest in putting its name below.) It should be noted, the use of the provision of data entry support tools is free of charge in principle with the aim of promoting wider use of chemSHERPA. [Contact information] Chemical Management Policy Division Manufacturing Industries Bureau Ministry of Economy, Trade and Industry [email protected] 03-3501-0080 (direct) 03-3501-1511 (ex. -

三井化学ar 2000.7.28

Mitsui Chemicals, Inc. http://www.mitsui-chem.co.jp Forging Ahead... Forging Mitsui Chemicals Ahead... Annual Report 2000 Year Ended March 31, 2000 Another Year of Progress Responsible Care Printed in Japan Common Stock Price Range (“Mitsui Chemicals”) aspires to be Stock Price Range Mitsui Chemicals, Inc. Nikkei 225 (right scale) (¥) (¥) “a diversified chemical company with a strong 1,200 40,000 competitive position in the global market” and is working toward this goal in line with its Medium-Term Corporate Plans. 900 30,000 Mitsui Chemicals’ business centers on petrochemicals & basic chemicals and performance materials. In trying to build a more powerful company, we are creating a new corporate 600 20,000 culture of selective focus that embodies three concepts: Speed, Efficiency and Effect. 300 10,000 This March 31, 2000 term annual report looks back on the achievements of the past two years and outlines our future plans. 0 0 10111298/12345678910111299/12345678910111200/1 2 3 Note: Mitsui Petrochemical Industries, Ltd. and Mitsui Toatsu Chemicals, Inc. merged on October 1, 1997 to form Mitsui Chemicals, Inc. Contents >1 Message From the Management >14 Review of Operations >5 Forging Ahead... Another Year of Progress >14 Basic Chemicals >6 Focus >16 Polymers >7 Development of New Products >18 Functional & Fine Chemicals >8 Globalization >20 Engineered Materials >9 Streamlined Group >22 Research & Development Strategy >10 Early Effective Merger Results >24 Responsible Care >11 Caring for the Environment and Safety >26 Board of Directors >11 Strengthening of Corporate Vitality >27 Financial Section >12 Mitsui Chemicals at a Glance >50 Major Subsidiaries and Affiliates >52 Corporate Data Forging Ahead.. -

"JPX-Nikkei Index 400"

JPX-Nikkei Index 400 Constituents (applied on August 30, 2019) Published on August 7, 2019 No. of constituents : 400 (Note) The No. of constituents is subject to change due to de-listing. etc. (Note) As for the market division, "1"=1st section, "2"=2nd section, "M"=Mothers, "J"=JASDAQ. Code Market Divison Issue Code Market Divison Issue 1332 1 Nippon Suisan Kaisha,Ltd. 3107 1 Daiwabo Holdings Co.,Ltd. 1333 1 Maruha Nichiro Corporation 3116 1 TOYOTA BOSHOKU CORPORATION 1605 1 INPEX CORPORATION 3141 1 WELCIA HOLDINGS CO.,LTD. 1719 1 HAZAMA ANDO CORPORATION 3148 1 CREATE SD HOLDINGS CO.,LTD. 1720 1 TOKYU CONSTRUCTION CO., LTD. 3167 1 TOKAI Holdings Corporation 1721 1 COMSYS Holdings Corporation 3197 1 SKYLARK HOLDINGS CO.,LTD. 1801 1 TAISEI CORPORATION 3231 1 Nomura Real Estate Holdings,Inc. 1802 1 OBAYASHI CORPORATION 3254 1 PRESSANCE CORPORATION 1803 1 SHIMIZU CORPORATION 3288 1 Open House Co.,Ltd. 1808 1 HASEKO Corporation 3289 1 Tokyu Fudosan Holdings Corporation 1812 1 KAJIMA CORPORATION 3291 1 Iida Group Holdings Co.,Ltd. 1820 1 Nishimatsu Construction Co.,Ltd. 3349 1 COSMOS Pharmaceutical Corporation 1821 1 Sumitomo Mitsui Construction Co., Ltd. 3360 1 SHIP HEALTHCARE HOLDINGS,INC. 1824 1 MAEDA CORPORATION 3382 1 Seven & I Holdings Co.,Ltd. 1860 1 TODA CORPORATION 3391 1 TSURUHA HOLDINGS INC. 1861 1 Kumagai Gumi Co.,Ltd. 3401 1 TEIJIN LIMITED 1878 1 DAITO TRUST CONSTRUCTION CO.,LTD. 3402 1 TORAY INDUSTRIES,INC. 1881 1 NIPPO CORPORATION 3405 1 KURARAY CO.,LTD. 1893 1 PENTA-OCEAN CONSTRUCTION CO.,LTD. 3407 1 ASAHI KASEI CORPORATION 1911 1 Sumitomo Forestry Co.,Ltd. -

Chemicals (29 June)

29 June 2015 Asia Pacific/Japan Equity Research Major Chemicals (Chemicals/Textiles (Japan)) / MARKET WEIGHT Chemicals Research Analysts COMPANY UPDATE Masami Sawato 81 3 4550 9729 [email protected] Corporate Day: Kuraray, Asahi Kasei, Tosoh, Shin-Etsu Chemical, JSR, Zeon, Ube Industries, Hitachi Chemical, Nippon Kayaku ■ Kuraray (3405, NEUTRAL TP ¥1,650): We forecast 1H FY3/16 OP of ¥29.5bn, beating guidance (¥29.0bn) by ¥0.5bn (the Quick consensus is ¥30.4bn). The company indicated that areas such as Poval products, including optical-use Poval film, isoprene, and methyl methacrylate have been outperforming, while glass laminating solutions (vinyl acetate-related) have been falling short of guidance. Based on firm 1Q shipments, the company expects shipment volume of optical-use Poval film to increase by around 7% YoY for the full year. We think Kuraray will likely leave full-year guidance unchanged. The company indicated that the impact of coated polarizing film among optical-use Poval film will be modest in the near term. ■ Asahi Kasei (3407, NEUTRAL, TP ¥1,200): We forecast 1Q OP of ¥32.0bn, equivalent to 45.4% of 1H guidance (¥70.5bn; Nikkei 1Q forecast ¥32.0bn; Quick consensus ¥32.1bn). The company indicated that profits have been tracking above guidance considering factors including that housing profits are concentrated in 2Q. At the chemicals segment, the company expects higher styrene monomer (SM) margins and functional resin outperformance to offset acrylonitrile (AN) margins, which have been tracking below its assumptions. We understand fibers, electronics, and pharmaceuticals & healthcare have also been firm. Housing orders are firm, but it expects a YoY decline in earnings due mainly to increases in materials and construction costs.