Thierry Moreau

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Supplemental Information

ARTICLE Supplemental Information PEDIATRICS Volume 146, Number 3, September 2020 1 SUPPLEMANTAL FIGURE 3 Example individualized antibiotic prescribing feedback report used in the DART study. Amox, amoxicillin; Clav, clavulanate; Rx, prescription. 2 ARTICLE SUPPLEMANTAL FIGURE 4 aRR for antibiotic prescribing from ITT analyses of the DART primary and secondary outcomes by study phase. PEDIATRICS Volume 146, Number 3, September 2020 3 SUPPLEMANTAL TABLE 5 ICD-10 Codes Used To Define ARTI Visits Diagnosis Included Conditions ICD-10 Codesa AOM Acute serous, allergic, and H65.0n, H65.11n, H65.19n, H65.2n, nonsuppurative otitis media; chronic H65.3n, H65.41n, H65.49n, H65.9n, serous, mucoid, allergic, and H66.00n, H66.01n, H66.1n, H66.2n, nonsuppurative otitis media H66.3Xn, H66.4n, H66.9n, and/or H67.n Pharyngitis Acute pharyngitis and tonsillitis J02, J02.n, J03, J03.00, J03.8n, and/or J03.9n Sinusitis Acute maxillary, frontal, ethmoidal, J01.0n, J01.1n, J01.2n, J01.3n, J01.4n, sphenoidal, and pansinusitis J01.8n, and/or J01.9n Viral ARTIsb Common cold, upper respiratory tract J00, J06.n, J10.1, J11.1, J20.3-J20.9, infection, influenza, bronchitis, and J21.n, and/or J40 bronchiolitis Additional Central venous catheter infections, T80.2n, T88.0n, W50.3n, W53.n1Xn, bacterial infection after immunization, bites and W54.0XXn, W55.n1Xn, W56.n1Xn, infectionsc scratches, infections due to specific W58.n1Xn, W59.n1Xn, W61.n1xn, pathogens (eg, Salmonella), sexually Y04.1xxn, A01.0n, A01.n, A02.n, A03.n, transmitted diseases, neutropenia, A04.n, A18.0n, -

This Is a Converted File. Please Check Before Making the Next Change

OEM: When controller is mounted, discard either Table 151 or Table 154 before attaching lower portion of the instruction sheet to your equipment. Table 151 should remain when the controller is mounted in a small enclusure(a volume of 860 cubic inches or less), or in the proximity of heat producing components which have the same effect as a small enclosure. Select Table 154 for use on open panels or in very large enclosures. BULLETIN 520, SIZE 2, 3-PHASE, heater Table 151 element selection table for controllers with Table 154 two Bulletin 592 3-pole overload relays. Heater Full Heater Full Type Load WARNING:To provide continued protec- Type Load No. Amps. tion against fire or shock hazard, the No. Amps. complete overload relay must be replaced W50 8.45 if burnout of any heater element occurs. W50 8.58 W51 9.32 W51 9.48 W52 10.3 W52 10.6 W53 11.3 IMPORTANT: When ordering heater W53 11.7 W54 12.3 elements for this controller, always specify W54 12.8 W55 13.4 the desired “Heater Type No.’ W55 14.1 W56 14.5 W56 15.4 W57 15.8 Motors Rated for Continuous Duty with W57 16.9 W58 16.7 Marked Service Factor Not Less Than 1.15 or W58 18.3 W59 18.1 Marked Temperature Rise Not Over 40°C. W59 19.9 W60 20.0 Select the ”Heater Type No.” with the listed W60 21.9 W61 22.0 “Full Load Amps.” nearest the full load W61 24.2 W62 24.5 current value shown on the motor W62 26.8 W63 27.3 nameplate when the ambient temperature W63 29.6 W64 29.2 at the controller and the motor is the same. -

Library of Congress Classification

R MEDICINE (GENERAL) R Medicine (General) Periodicals. Societies. Serials 5 International periodicals and serials 10 Medical societies Including aims, scope, utility, etc. International societies 10.5.A3 General works 10.5.A5-Z Individual societies America English United States. Canada 11 Periodicals. Serials 15 Societies British West Indies. Belize. Guyana 18 Periodicals. Serials 20 Societies Spanish and Portuguese Latin America 21 Periodicals. Serials 25 Societies 27.A-Z Other, A-Z 27.F7 French Europe English 31 Periodicals. Serials 35 Societies Dutch 37 Periodicals. Serials 39 Societies French 41 Periodicals. Serials 45 Societies German 51 Periodicals. Serials 55 Societies Italian 61 Periodicals. Serials 65 Societies Spanish and Portuguese 71 Periodicals. Serials 75 Societies Scandinavian 81 Periodicals. Serials 85 Societies Slavic 91 Periodicals. Serials 95 Societies 96.A-Z Other European languages, A-Z 96.H8 Hungarian Asia 97 English 97.5.A-Z Other European languages, A-Z 97.7.A-Z Other languages, A-Z Africa 98 English 98.5.A-Z Other European languages, A-Z 98.7.A-Z Other languages, A-Z 1 R MEDICINE (GENERAL) R Periodicals. Societies. Serials -- Continued Australasia and Pacific islands 99 English 99.5.A-Z Other European languages, A-Z 99.7.A-Z Other languages, A-Z Indexes see Z6658+ (101) Yearbooks see R5+ 104 Calendars. Almanacs Cf. AY81.M4 American popular medical almanacs 106 Congresses 108 Medical laboratories, institutes, etc. Class here papers and proceedings For works about these organizations see R860+ Collected works (nonserial) Cf. R126+ Ancient Greek and Latin works 111 Several authors 114 Individual authors Communication in medicine Cf. -

Heater Element Specifications Bulletin Number 592

Technical Data Heater Element Specifications Bulletin Number 592 Topic Page Description 2 Heater Element Selection Procedure 2 Index to Heater Element Selection Tables 5 Heater Element Selection Tables 6 Additional Resources These documents contain additional information concerning related products from Rockwell Automation. Resource Description Industrial Automation Wiring and Grounding Guidelines, publication 1770-4.1 Provides general guidelines for installing a Rockwell Automation industrial system. Product Certifications website, http://www.ab.com Provides declarations of conformity, certificates, and other certification details. You can view or download publications at http://www.rockwellautomation.com/literature/. To order paper copies of technical documentation, contact your local Allen-Bradley distributor or Rockwell Automation sales representative. For Application on Bulletin 100/500/609/1200 Line Starters Heater Element Specifications Eutectic Alloy Overload Relay Heater Elements Type J — CLASS 10 Type P — CLASS 20 (Bul. 600 ONLY) Type W — CLASS 20 Type WL — CLASS 30 Note: Heater Element Type W/WL does not currently meet the material Type W Heater Elements restrictions related to EU ROHS Description The following is for motors rated for Continuous Duty: For motors with marked service factor of not less than 1.15, or Overload Relay Class Designation motors with a marked temperature rise not over +40 °C United States Industry Standards (NEMA ICS 2 Part 4) designate an (+104 °F), apply application rules 1 through 3. Apply application overload relay by a class number indicating the maximum time in rules 2 and 3 when the temperature difference does not exceed seconds at which it will trip when carrying a current equal to 600 +10 °C (+18 °F). -

K-12 Individual No. Name Team Gr Rate Pts Tbrk1 Tbrk2 Tbrk3 Tbrk4

K-12 Individual No. Name Team Gr Rate Pts TBrk1 TBrk2 TBrk3 TBrk4 Rnd1 Rnd2 Rnd3 Rnd4 Rnd5 Rnd6 1 Chakraborty, Dipro 11 2299 5.5 21 24 43 20.5 W27 W12 W5 W32 W8 D3 State Champion, AZ Denker Representative 2 Yim, Tony Sung BASISS 8 2135 5 20.5 23.5 38.5 17.5 W24 W10 D3 D16 W11 W9 3 Aletheia-Zomlefer, Soren CHANPR 11 1961 5 20 23 35.5 18.5 W25 W26 D2 W40 W15 D1 4 Desmarais, Nicholas Eduard NOTRED 10 1917 5 18 20 33 18 W39 W23 W18 L15 W10 W8 5 Wong, Kinsleigh Phillip CFHS 10 1992 4.5 20 20 24.5 15 -X- W17 L1 W26 D7 W15 6 Todd, Bryce BASISC 10 1923 4.5 17 19 26.5 14.5 W38 D18 L9 W23 W21 W16 7 Chaliki, Kalyan DSMTHS 9 1726 4.5 17 18.5 26 15 W46 L16 W28 W22 D5 W17 8 Li, Bohan UHS 9 2048 4 22 25 29 18 W30 W11 W45 W9 L1 L4 9 Mittal, Rohan CFHS 9 1916 4 19.5 20.5 23 17 W47 W22 W6 L8 W20 L2 10 Pennock, Joshua CFHS 10 1682 4 19 22 24 14 W31 L2 W25 W21 L4 W29 11 Aradhyula, Sumhith CFHS 9 1631 4 18 20 22 14 W41 L8 W38 W13 L2 W19 12 Johnston, Nicolas Godfrey CFHS 9 1803 4 18 19.5 21 13 W43 L1 W29 L17 W24 W20 13 Martis, Tyler BRHS 12 1787 4 17 18 21 13 W42 L15 W24 L11 W18 W22 14 Plumb, Justin Rodney GCLACA 10 1700 4 16 17 20 13 W51 L32 W19 L20 W28 W27 15 Martinez, Isaac GLPREP 10 2159 3.5 21.5 24.5 27.5 16 W28 W13 D16 W4 L3 L5 16 Chen, Derek H CFHS 10 1965 3.5 21 23.5 26 15.5 W35 W7 D15 D2 D17 L6 17 Woodson, Tyler GILBHS 1640 3.5 19 19 17.5 14 W50 L5 W30 W12 D16 L7 18 Cancio, Aiya CFHS 9 1469 3.5 18.5 20 17.5 12.5 W36 D6 L4 W46 L13 W25 AZ Girls' Invitational Representative 19 Folden, Kurt CHANPR 10 1207 3 14 18 12 10 L32 W50 L14 W31 W23 L11 20 Thornton, -

Quarterly Report Department of Energy Implementation Plan For

October 29, 1996, DOE forwards Quarterly Report (for the period July 1 ... http://www.hss.doe.gov/deprep/1996-2/qr96o29c.htm Quarterly Report Department of Energy Implementation Plan for Defense Nuclear Facilities Safety Board Recommendation 93-6 Maintaining Access to Nuclear Weapons Expertise Reporting Period July 1 through September 30, 1996 Table of Contents Section Title 1.0 Commitment Status 2.0 Activities 2.1 Pantex 2.2 Y-12 2.3 Nevada 2.4 Archiving 3.0 Meetings 2 Attachments: Summary of 93-6 Archiving Televideo Conference conducted on July 23, 1996 Summary of 93-6 Archiving Televideo Conference conducted on September 16, 1996 1.0 Deliverable Status Deliverable Due Date Status Remarks A.1.A Feb 29, 1996 Complete Deliverable provided to DNFSB on March 26, 1996. A.1.B May 30, 1996 Complete W69 provided to the DNFSB on May 7, 1996. W56 WSS provided to the DNFSB on August 12, 1996. A.2 May 31, 1996 Complete Deliverable provided to DNFSB on August 27, 1996. A.3 Feb 29, 1996 Complete Deliverable provided to DNFSB on January 24, 1996. B.1 Jan 31, 1996 Complete Deliverable provided to DNFSB on February 2, 1996. 1 of 18 7/1/2011 10:38 AM October 29, 1996, DOE forwards Quarterly Report (for the period July 1 ... http://www.hss.doe.gov/deprep/1996-2/qr96o29c.htm B.2 Sep 30, 1996 Complete Deliverable provided to DNFSB on October 28, 1996. C.1 Jan 31, 1996 Complete Deliverable provided to DNFSB on February 2, 1996. D.1 Jan 31, 1996 Complete Deliverable provided to DNFSB on February 2, 1996. -

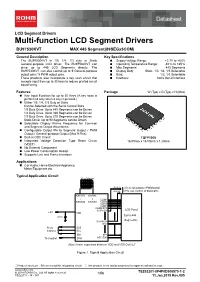

BU97530KVT MAX 445 Segment(89Segx5com)

Datasheet LCD Segment Drivers Multi-function LCD Segment Drivers BU97530KVT MAX 445 Segment(89SEGx5COM) General Description Key Specifications The BU97530KVT is 1/5, 1/4, 1/3 duty or Static ■ Supply Voltage Range: +2.7V to +6.0V General-purpose LCD driver. The BU97530KVT can ■ Operating Temperature Range: -40°C to +85°C drive up to 445 LCD Segments directly. The ■ Max Segments: 445 Segments BU97530KVT can also control up to 9 General-purpose ■ Display Duty Static, 1/3, 1/4, 1/5 Selectable output pins / 9 PWM output pins. ■ Bias: 1/2, 1/3 Selectable These products also incorporate a key scan circuit that ■ Interface: 3wire Serial Interface accepts input from up to 30 keys to reduce printed circuit board wring. Features Package W (Typ) x D (Typ) x H (Max) Key Input Function for up to 30 Keys (A key scan is performed only when a key is pressed.) Either 1/5, 1/4, 1/3 Duty or Static Can be Selected with the Serial Control Data. 1/5 Duty Drive: Up to 445 Segments can be Driven 1/4 Duty Drive: Up to 360 Segments can be Driven 1/3 Duty Drive: Up to 270 Segments can be Driven Static Drive: Up to 90 Segments can be Driven Selectable Display Frame Frequency for Common and Segment Output Waveforms. Configurable Output Pin to Segment Output / PWM Output / General-purpose Output.(Max 9 Pins) Built-in OSC Circuit TQFP100V Integrated Voltage Detection Type Reset Circuit 16.00mm x 16.00mm x 1.20mm (VDET) No External Component Low Power Consumption Design Supports Line and Frame Inversion Applications Car Audio, Home Electrical Appliance, Meter Equipment etc. -

Eagle July Wine Editable

august 2021 WINE BY THE GLASS WHITES REDS Flirty & Sparky Gls/Btl Alluring & Spicy Gls/Btl MIONETTO Prosecco (Italy) 7/28 CARICATURE Zinfandel ‘18 (Lodi, CA) *S-G 8/32 VIETTI Moscato d’Asti ‘20 (IT) Half btl 10/20 AMAVI by Pepper Bridge Syrah ‘18 (WA) 14/56 LARCHARGO Reserva Tempranillo ‘12 (SP) 9/36 Sumptously Fruity ALTOS ‘Las Hormigas’ Malbec ‘19 (ARG) 8/32 Ste. CHAPELLE Soft Huckleberry (ID) 5/20 Pinot Noir & Light-bodied Red Dr. LOOSEN Qba Riesling ‘20 (GER) 6/24 MEIOMI ‘19 (CA) 10/40 Refreshing & Satisfying PATTON VALLEY Estate ‘18 (OR) 10/40 LAVENDETTE Rose ‘20 (FR) 8/32 GULP/HABLO TINTO Red ‘19 (SP) *S-G 7/28 McMANIS Pinot Grigio ‘20 (CA) 6/24 As the name implies, this blend is delish and easy-drinking! ELK COVE Pinot Gris ‘20 (OR) 9/36 Handsome Blends Perky & Crisp PASSIONATE ‘Tinto’ Malbec blend ‘19 (AR) 9/36 MARIETTA ‘Lot 72’ Zin blend (CA) 6/24 TELAYA Viognier ‘20 (Yakima, WA) 9/36 SPLIT RAIL GSM ‘17 Rhone style (ID) By draft! 9 Gls LANZOS Sauvignon Blanc blend ‘19 (SP) *S-G 8/32 NAUTILUS Sauvignon Blanc ‘20 (NZ) *S-G 8/32 Merlot CROW CANYON ‘18 (CA) 5/20 Chardonnay DECOY by Duckhorn ‘19 (Sonoma) 12/48 LOST ANGEL ‘18 (CA) 6/24 Cabernet Sauvignon & Cab Blends LA CREMA ‘18 (Sonoma Coast, CA) 9/36 SALMON CREEK ‘17 (CA) 5/20 ROMBAUER ‘20 (Carneros, CA) 17/68 LOUIS MARTINI ‘18 (Sonoma) 9/36 SLEIGHT OF HAND ‘Spellbinder’ ‘18 (WA) 10/40 BODEGAS LANZOS Blanco 8/Gls J. -

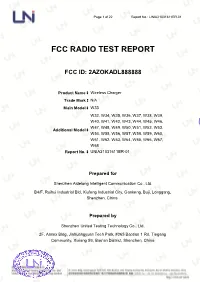

Measurement Report

Page 1 of 22 Report No.: UNIA21031611ER-01 FCC RADIO TEST REPORT FCC ID: 2AZOKADL888888 Product Name: Wireless Charger Trade Mark: N/A Main Model: W33 W32, W34, W35, W36, W37, W38, W39, W40, W41, W42, W43, W44, W45, W46, W47, W48, W49, W50, W51, W52, W53, Additional Model: W54, W55, W56, W57, W58, W59, W60, W61, W62, W63, W64, W65, W66, W67, W68 Report No.: UNIA21031611ER-01 Prepared for Shenzhen Aidelong Intelligent Communication Co., Ltd. B4/F, Ruihui Industrial Bld, Xiufeng Industrial City, Gankeng, Buji, Longgang, Shenzhen, China Prepared by Shenzhen United Testing Technology Co., Ltd. 2F, Annex Bldg, Jiahuangyuan Tech Park, #365 Baotian 1 Rd, Tiegang Community, Xixiang Str, Bao'an District, Shenzhen, China Page 2 of 22 Report No.: UNIA21031611ER-01 TEST RESULT CERTIFICATION Applicant .............................. : Shenzhen Aidelong Intelligent Communication Co., Ltd. B4/F, Ruihui Industrial Bld, Xiufeng Industrial City, Gankeng, Buji, Address ................................. : Longgang, Shenzhen, China Manufacturer ........................ : Shenzhen Aidelong Intelligent Communication Co., Ltd. B4/F, Ruihui Industrial Bld, Xiufeng Industrial City, Gankeng, Buji, Address ................................. : Longgang, Shenzhen, China Product description Product Name .............................. : Wireless Charger Trade Mark ............................ : N/A W33, W32, W34, W35, W36, W37, W38, W39, W40, W41, W42, W43, W44, W45, W46, W47, W48, W49, W50, W51, W52, W53, Model Name .......................... : W54, W55, W56, W57, W58, W59, W60, W61, W62, W63, W64, W65, W66, W67, W68 FCC Rules and Regulations Part 15 Subpart C Section 15.209 Test Methods ........................ : ANSI C63.10: 2013 This device described above has been tested by Shenzhen United Testing Technology Co., Ltd., and the test results show that the equipment under test (EUT) is in compliance with the FCC requirements. -

Improving Health Through Evidence-Based Probiotics

Improving health through evidence-based probiotics Company Profile & Probiotic Portfolio wincloveprobiotics.com vw Company Profile Winclove Probiotics Developing probiotic formulations since 1991 with a strong emphasis on research Winclove Probiotics, established in Amsterdam, The Netherlands, has been specializing in research, development and manufacturing of probiotic formulations for over 25 years. Our probiotic formulations are developed in close collaboration with leading research institutes, universities and academic hospitals. This enables us to develop innovative multispecies probiotic formulations for many different health indications. We continuously invest in research and technologies in order to develop the most effective probiotics that ensure end-users with the best solution. Looking for business opportunities? Winclove’s mission is to create long-lasting, sustainable and strategic partnerships. To achieve this, we offer innovative, high-quality and competitive probiotic solutions, as well as in-house scientific expertise and sales support. Our indication-specific formulations are designed for specific microbiota-related indications. The thorough substantiation of our probiotic formulations with scien- tific and clinical evidence makes them ideal for selling medically endorsed. We are a committed business partner and are looking forward to starting a fruitful collaboration with you! Product package Dossiers Technical lab analysis, in vitro data, etc. Clinical in vivo studies, Development of Probiotic blend post market studies, -

BU91530KVT-M : Display Drivers

Datasheet LCD Segment Drivers Multi-function LCD Segment Drivers BU91530KVT-M MAX 445 Segment(89SEGx5COM) General Description Key Specifications The BU91530KVT-M is 1/5, 1/4, 1/3 or 1/1 duty ■ Supply Voltage Range: +2.7V to +6.0V general-purpose LCD driver that can be used for ■ Operating Temperature Range: -40°C to +85°C frequency display in electronic tuners under the control of ■ Max Segments: 445 Segments a microcontroller. The BU91530KVT-M can drive up to ■ Display Duty 1/1, 1/3, 1/4, 1/5 Selectable 445 LCD Segments directly. The BU91530KVT-M can ■ Bias: 1/2, 1/3 Selectable also control up to 9 general-purpose output ports. ■ Interface: 3wire Serial Interface These products also incorporate a key scan circuit that accepts input from up to 30 keys to reduce printed circuit board wring. Package W (Typ.) x D (Typ.) x H (Max.) Features AEC-Q100 Qualified (Note1) Key input function for up to 30 keys (A key scan is performed only when a key is pressed.) Either 1/5, 1/4, 1/3 or 1/1 duty (static) can be selected with the serial control data. 1/5 duty drive: Up to 445 segments can be driven 1/4 duty drive: Up to 360 segments can be driven 1/3 duty drive: Up to 270 segments can be driven 1/1 duty drive: Up to 90 segments can be driven Serial Data Control of frame frequency for common and segment output waveforms. Serial data control of switching between the segment TQFP100V output port , PWM output port and general-purpose 16.00mm x 16.00mm x 1.20mm output port functions.(Max 9 ports) Built-in OSC circuit Integrated Power-on Reset Circuit No external component Low power consumption design Supports Line and Frame Inversion (Note1) Grade 3 Applications Car Audio, Home Electrical Appliance, Meter Equipment etc. -

NEMA Motor Control

Bulletin Eutectic Alloy Overload Relays Heater Elements Selection For Application on Bulletin 100/500/609/1200 Line Starters Eutectic Alloy Overload Relay Heater Elements Heater Element Selection Type J — CLASS 10 Table of Contents 0 Type P — CLASS 20 (Bul. 600 ONLY) Type W — CLASS 20 Overload Relay Type WL — CLASS 30 Class Designation...... this page Heater Element Selection ....................... this page 1 Type W Heater Elements Ambient Temperature Correction..................... this page Time — Current Characteristics............ 1-169 2 Index to Heater Element Selection Tables ............................. 1-170 3 Description The following is for motors rated for Continuous Duty: For motors with marked service factor of not less than 1.15, or Overload Relay Class Designation motors with a marked temperature rise not over +40 °C United States Industry Standards (NEMA ICS 2 Part 4) designate an (+104 °F), apply application rules 1 through 3. Apply application 4 overload relay by a class number indicating the maximum time in rules 2 and 3 when the temperature difference does not exceed seconds at which it will trip when carrying a current equal to 600 +10 °C (+18 °F). When the temperature difference is greater, see percent of its current rating. below. A Class 10 overload relay will trip in 10 seconds or less at a current 1. The Same Temperature at the Controller and the Motor — equal to 600 percent of its rating. Select the “Heater Type Number” with the listed “Full Load 5 Amperes” nearest the full load value shown on the motor A Class 20 overload relay will trip in 20 seconds or less at a current nameplate.