LP5520 RGB Backlight LED Driver Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

An Analysis of Power Consumption in a Smartphone

An Analysis of Power Consumption in a Smartphone Josh Hildebrand Introduction l Mobile devices derive the energy required to operate from batteries that are limited by the size of the device. l The ability to manage energy usage requires a good understanding of where and how the energy is being used. l The advancing functionality of modern smartphones is increasing the pressure on battery lifetime, and increases the need for effective energy management. l Goal is to break down a modern smartphone and measure the power consumption of the devices major subsystems, under a range of usage scenarios. l Results from the breakdown of energy consumption will be validated against two additional mobile devices. l Finally, an analysis of the energy consumption will be performed, and an energy model will be created to allow us to model usage patterns. Methodology / Device Under Test l The approach is to take physical power measurements at the component level on a piece of real hardware. l Three elements to the experimental setup, the device under test, a hardware data acquisition (DAQ) system, and a host computer. l Device under test is the Openmoko Neo Freerunner 2.5G smartphone. Experimental Setup l To measure power to each component, supply voltage and current must be measured. l Current is measured by placing sense resistors on the power supply rails of each component. Resistors were selected such that the voltage drop did not exceed 10mV, less than 1% of the supply voltage. l Voltages were measured using a National Instruments PCI-6229 DAQ. Software l The device was running the Freerunner port of Android 1.5, using the Linux v2.6.29 kernel. -

Illumination Is One of the Most Critical Components of a Machine Vision

Lighting llumination is one of the most critical components of a machine vision system. The selection of Ithe appropriate lighting component for a specific application is very important to ensure that a machine vision system performs its tasks consistently and reliably. The main reason is that improper illumination results in loss of information which, in most cases, cannot be recovered via software. This is why the selection of quality lighting components is of primary importance: there is no software algorithm capable of revealing features that are not correctly illuminated. To make the most appropriate choice, one must consider many different parameters, including: • Lighting geometry • Light source type • Wavelength • Surface property of the material to be inspected or measured (e.g. color, reflectivity) • Item shape • Item speed (inline or offline application) • Mechanical constraints • Environment considerations • Cost Since many parameters must be considered, the choice can be difficult and sometimes the wisest advice is to perform feasibility studies with different light types to reveal the features of interest. On the other hand, there are a number of simple rules and good practices that can help select the proper lights and improve the image quality. For every application, the main objectives are the following: 1. Maximizing the contrast of the features that must be inspected or measured 2. Minimizing the contrast of the features of no interest 3. Getting rid of unwanted variations caused by: a. Ambient light b. Differences between items that are non-relevant to the inspection task www.opto-engineering.com Light in machine vision n machine vision, light is mostly characterized by its wavelength, Light visible to the human eye has wavelengths in the range of Iwhich is generally expressed in nm (nanometers). -

Dell Latitude 14 Rugged Extreme (7404) Getting Started Guide

Dell Latitude 14 Rugged Extreme (7404) Getting Started Guide Regulatory Model: P45G Regulatory Type: P45G001 Notes, Cautions, and Warnings NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. Copyright © 2014 Dell Inc. All rights reserved. This product is protected by U.S. and international copyright and intellectual property laws. Dell™ and the Dell logo are trademarks of Dell Inc. in the United States and/or other jurisdictions. All other marks and names mentioned herein may be trademarks of their respective companies. 2014 - 06 Rev. A01 Contents 1 Finding Information and Resources.....................................................................4 2 System Overview.......................................................................................................5 3 Quick Setup................................................................................................................ 7 4 Removing and Installing Components............................................................... 9 Opening the Press-Latch Doors...........................................................................................................9 Closing the Press-Latch Doors.............................................................................................................9 Removing the Battery............................................................................................................................9 -

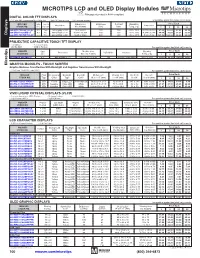

MICROTIPS LCD and OLED Display Modules This Page of Product Is Rohs Compliant

MICROTIPS LCD and OLED Display Modules This page of product is RoHS compliant. DIGITAL COLOR TFT DISPLAYS • 3.5" with TMR-Transmissive Micro Reflective • Up to 16.7 million colors • SPI Interface available For quantities greater than listed, call for quote. MOUSER Size Touch Dimensions Brightness Contrast Operating Price Each Resolution Pixel Pitch STOCK NO. (in.) Screen W x H (mm) (nits) Ratio Temp. (°C) 1 5 10 50 668-MTF-TQ35SP741-AV 3.5 Yes 240 x RGB x 320 76.9 x 63.9 210 200 -20 to 70°C 0.073 x 0.219 67.20 61.09 57.93 54.19 668-UMSH-8253MD-1T 4.3 No 480 x RGB x 272 95.04 x 53.856 500 500 -20 to 70°C 0.198 x 0.198 40.00 38.24 37.37 33.97 Displays 668-MTF-TV57NP721-AV 5.7 Yes 640 x RGB x 480 144.0 x 104.6 400 300 -20 to 70°C 0.36 x 0.36 107.10 103.90 96.69 92.82 PROJECTIVE CAPACITIVE TOUCH TFT DISPLAY • Transmissive • 6 o'clock Viewing • LED Backlight • COG IC Package For quantities greater than listed, call for quote. MOUSER Size Module Size Opening Price Each Resolution LCD Mode Interface STOCK NO. (in.) W x H x T (mm) Temp. (°C) 1 5 10 50 668-UMSH-8253MD-3T 4.3 480 x RGB x 272 105.5 x 67.2 x 5.45 TN Parallel 24-bit RGB -20 to + 70°C 69.23 66.17 64.27 58.31 Microtips GRAPHIC MODULES - TOUCH SCREEN Graphic Modules-Transflective With Backlight and Negative Transmissive With Backlight • 122x32 and 128x64Dot Pixels (WxH) For quantities greater than listed, call for quote. -

Zaggkeys Profolio Plus Instructions

NEED MORE HELP? PLEASE SEE OUR FAQ SECTION AT: www.ZAGG.com/faq WARRANTY REGISTRATION YOUR ZAGGkeys™ ProFolio Plus™ COMES WITH A 1 YEAR MANUFACTURER’S WARRANTY. YOU MUST REGISTER YOUR ProFolio Plus AND KEEP YOUR RECEIPT OF PURCHASE TO ACTIVATE THE WARRANTY. IF YOU PURCHASED ON ZAGG.COM, ZAGG HAS ALREADY REGISTERED YOUR ProFolio Plus AND HAS YOUR PROOF OF PURCHASE. INSERTING/REMOVING YOUR iPAD® TO INSERT THE iPAD®, HAVE KEYBOARD ON THE LEFT WITH iPAD® HOME BUTTON FACING YOU AND SLIDE THE iPAD® IN AND TO THE RIGHT. TO REMOVE THE IPAD®, PULL THE LEFT SIDE. POSITIONING PLACE THE iPAD® INTO THE CENTRAL GROOVE AND LEAN BACK. POWERING ON AND PAIRING YOUR ZAGGkeys ProFolio THE ZAGGkeys ProFolio’s BLUETOOTH KEYBOARD SHOULD ONLY NEED TO PAIR TO YOUR iPAD® ONCE AS FOLLOWS: 1. ON THE ZAGGkeys ProFolio Plus, SLIDE THE POWER BUTTON ON. THE BLUE CAPS LOCK LIGHT WILL ILLUMINATE FOR FOUR SECONDS AND THEN TURN OFF TO SAVE POWER. YOUR ProFolio Plus IS STILL ON. 2. PRESS THE PAIR BUTTON AND THE CAPS LOCK LIGHT WILL FLASH INDICATING THAT YOUR ProFolio Plus IS READY TO PAIR. 3. ON THE iPAD®, SELECT: SETTINGS > GENERAL > BLUETOOTH > ON. 4. THE CAPS LOCK LIGHT WILL FLASH ON THE ProFolio Plus AND THE iPAD® WILL DISPLAY “ZAGGkeys ProFolio Plus” AS AN AVAILABLE DEVICE. 5. SELECT “ZAGGkeys ProFolio Plus” ON THE iPAD®; TO PAIR. 6. YOUR iPAD® AND ProFolio Plus WILL AUTOMATICALLY PAIR. CHARGING YOUR ProFolio Plus COMES WITH A CHARGING CABLE THAT PLUGS INTO THE SIDE OF THE DEVICE. YOU CAN PLUG THE OTHER END OF THE CHARGING CABLE INTO ANY USB OUTLET, INCLUDING THE FOLLOWING: A COMPUTER, YOUR iPAD® CHARGER, A ZAGGsparq™, ETC. -

Liquid Crystal Display Module

LIQUID CRYSTAL DISPLAY MODULE Product Specification PRODUCT NUMBER TSR5413 INTERNAL APPROVALS Product Manager Engineering Document Control Product No. TSR5413 REV. G Page 1 / 34 Copyright ©2008 DENSITRON CORPORATION All rights reserved. – Proprietary Data FORM No. DT-029 V2 TABLE OF CONTENTS 1 PRODUCT SPECIFICATION ........................................................................................... 4 1.1 MAIN FEATURES .................................................................................................... 4 1.2 AVAILABLE FLUID AND POLARIZER TYPES ....................................................... 5 1.3 AVAILABLE BACKLIGHT TYPES AND COLORS .................................................. 5 1.4 CHOICE OF BACKLIGHT COLORS AND LCD SURFACE LUMINOSITIES .......... 5 2 MECHANICAL DRAWING ............................................................................................... 6 2.1 FOR ALL BACKLIGHT TYPES EXCEPT SUNBURST YELLOW AND RGB .......... 6 2.2 FOR SUNBURST YELLOW BACKLIGHT TYPE ..................................................... 7 2.3 FOR RGB TYPE BACKLIGHT ................................................................................. 8 3 PIN CONNECTIONS ........................................................................................................ 9 4 THE STEP-UP VOLTAGE CIRCUITS............................................................................ 10 5 LCD GLASS LAYOUT ................................................................................................... 11 6 RECOMMENDED -

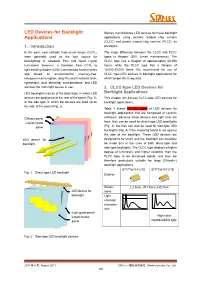

LED Devices for Backlight Applications That Are Composed of Ceramic Diffuser Panel拡散板 Reflectors

LED Devices for Backlight Stanley manufactures LED devices for these backlight Applications applications using ceramic leaded chip carriers (CLCC) and plastic leaded chip carriers (PLCC) as 1. Introduction packages. In the past, cold cathode fluorescent lamps (CCFL) The major difference between the CLCC and PLCC were generally used as the light source for types is lifespan (50% lumen maintenance). The backlighting in notebook PCs and liquid crystal CLCC type has a lifespan of approximately 60,000 televisions. However, a transition from CCFL to hours, while the PLCC type has a lifespan of light-emitting diodes (LED) commenced several years 15,000-20,000 hours. We recommend the use of ago based on environmental (mercury-free, CLCC type LED devices in backlight applications for low-power-consumption, long life) and functional (thin, which longer life is required. lightweight, local dimming) considerations, and LED are now the main light source in use. 2. CLCC-type LED Devices for LED backlights may be of the direct type, in which LED Backlight Applications devices are positioned at the rear of the panel (Fig. 1), This chapter will discuss CLCC-type LED devices for or the side type, in which the devices are lined up on backlight applications. the side of the panel (Fig. 2). Table 1 shows the four types of LED devices for backlight applications that are composed of ceramic Diffuser panel拡散板 reflectors. Because these devices emit light from the Liquid液晶パネル crystal front, they can be used for direct-type LED backlights panel (Fig. 3), but they can also be used for side-type LED backlights (Fig. -

![Application Note [AN-005] Liquid Crystal Display (LCD) Modes](https://docslib.b-cdn.net/cover/9925/application-note-an-005-liquid-crystal-display-lcd-modes-3199925.webp)

Application Note [AN-005] Liquid Crystal Display (LCD) Modes

Application Note [AN-005] Liquid Crystal Display (LCD) Modes Introduction Unlike cathode ray tubes (CRTs), liquid crystal displays (LCDs) are not emissive i.e. they do not generate their own light source. In order to see an image on an LCD of any type (thin-film transistor (TFT), twisted nematic (TN) or super twisted nematic (STN) LCD etc.) a light source is required. This light source can be either ambient e.g. sunlight or some form of artificial lighting e.g. light emitting diodes (LEDs), cold cathode fluorescent lamp (CCFL) or electroluminescence panels (ELP) etc. on the rear or the front of the display. LCD panels can be designed to operate in a variety of viewing modes to allow operation in any lighting condition, from direct sunlight to total darkness. The polarisers used and the LCD panel construction determine the viewing mode of the LCD. There are three basic modes of an LCD, reflective, transmissive and transflective, each mode of the LCD is described in this application note. Contents INTRODUCTION .......................................................................................................................................... 1 CONTENTS.................................................................................................................................................. 1 INDEX OF FIGURES.................................................................................................................................... 2 INDEX OF TABLES .................................................................................................................................... -

Light Emitting Diodes Reliability Review ⇑ Moon-Hwan Chang A, Diganta Das A, P.V

Microelectronics Reliability 52 (2012) 762–782 Contents lists available at ScienceDirect Microelectronics Reliability journal homepage: www.elsevier.com/locate/microrel Light emitting diodes reliability review ⇑ Moon-Hwan Chang a, Diganta Das a, P.V. Varde a,c, Michael Pecht a,b, a CALCE Center for Advanced Life Cycle Engineering, University of Maryland, College Park, MD 20742, United States b Center for Prognostics and System Health Management, City University of Hong Kong, Hong Kong, China c Homi Bhabha National Institute, Reactor Group, Dhruva Complex, Bhabha Atomic Research Centre, Mumbai 400 085, India article info abstract Article history: The increasing demand for light emitting diodes (LEDs) has been driven by a number of application cat- Received 21 February 2011 egories, including display backlighting, communications, medical services, signage, and general illumina- Received in revised form 9 July 2011 tion. The construction of LEDs is somewhat similar to microelectronics, but there are functional Accepted 16 July 2011 requirements, materials, and interfaces in LEDs that make their failure modes and mechanisms unique. Available online 15 August 2011 This paper presents a comprehensive review for industry and academic research on LED failure mecha- nisms and reliability to help LED developers and end-product manufacturers focus resources in an effec- tive manner. The focus is on the reliability of LEDs at the die and package levels. The reliability information provided by the LED manufacturers is not at a mature enough stage to be useful to most con- sumers and end-product manufacturers. This paper provides the groundwork for an understanding of the reliability issues of LEDs across the supply chain. -

Transparent OLED Display

Planar LookThru Transparent OLED Display Transparent OLED Display Creates Truly See-Through Installations The Planar® LookThru® Transparent Display makes it possible to create truly see-through installations with a virtually frameless glass design by utilizing cutting-edge Organic Light Emitting Diode (OLED) technology, eliminating the needed for a backlight or enclosure. With a 55" diagonal, Planar LookThru features bright, vibrant colors greater than 120 percent National Television System Committee (NTSC) performance, as well as wide viewing angles with no off-axis contrast or brightness limitations. The display provides Full HD resolution, delivering beautiful graphics and full-motion video. Planar LookThru can be used in both portrait and landcape modes, table top or ceiling mount and can be tiled to create large, eye-catching video wall arrays. Corning® Gorilla® Glass is optically bonded to the display using Planar® ERO-OLED™ (Extended Ruggedness and Optics™) technology to create a highly durable display and accommodate touch screen usage for interactive applications. Planar LookThru displays are available with a wide range of accessories, expanding the application capabilities. The accessories include four tiling components that cater to multi-display tiling designs featuring flat or corner configurations. In addition, other accessories available include Base Plates for securing Planar LookThru displays to ceilings and a Platform Cover that creates a staging surface for items placed behind the display while protecting Planar LookThru -

Maintenance and Service Guide HP 15 Laptop PC

Maintenance and Service Guide HP 15 Laptop PC © Copyright 2018, 2019 HP Development Product notice Software terms Company, L.P. This user guide describes features that are By installing, copying, downloading, or AMD, Athlon, Ryzen, and Radeon are common to most models. Some features may otherwise using any software product trademarks of Advanced Micro Devices, Inc. not be available on your computer. preinstalled on this computer, you agree to be Bluetooth is a trademark owned by its bound by the terms of the HP End User License proprietor and used by HP Inc. under license. Not all features are available in all editions of Agreement (EULA). If you do not accept these Windows is a trademark of the Microsoft group Windows. This computer may require upgraded license terms, your sole remedy is to return the of companies. and/or separately purchased hardware, drivers entire unused product (hardware and software) and/or software to take full advantage of within 14 days for a full refund subject to the The information contained herein is subject to Windows functionality. Go to refund policy of your seller. change without notice. The only warranties for http://www.microsoft.com for details. HP products and services are set forth in the For any further information or to request a full express warranty statements accompanying refund of the price of the computer, please such products and services. Nothing herein contact your seller. should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. Second Edition: February 2019 First Edition: April 2018 Document Part Number: L19675-002 Important Notice about Customer Self-Repair Parts CAUTION: Your computer includes Customer Self-Repair parts and parts that should only be accessed by an authorized service provider. -

Pro Keys (2020) Online Manual Warranty Registration Your ZAGG Pro Keys Wireless Keyboard and Detachable Case Comes with a One-Year Manufacturer’S Warranty

pro keys (2020) Online Manual Warranty Registration Your ZAGG Pro Keys wireless keyboard and detachable case comes with a one-year manufacturer’s warranty. In order to activate the warranty, you must register your Pro Keys as well as keep your purchase receipt. If you purchased your Pro Keys from ZAGG.com, ZAGG has already registered it and has a copy of your proof of purchase. Need more help? Please see our FAQ section at: www.zagg. com/faq See the important Health and Safety information on page 12 before using this product. 1 INSERTING YOUR DEVICE 1 2 1. Holding your device in landscape mode with the volume control buttons facing up, press the top half of your device into the case and apply light pressure to snap it snuggly into place. 2. Press the bottom half of your device into the case and check each corner to make sure your device is seated properly. 2 fn ctrl 1 2 fn ctrl 3. Once your device has been inserted into the case, attach the case to the keyboard by setting the case in one of the two cradles on the keyboard (above the keys). 4. Place the top of the magnetized, foldable back flap against the top of the back of the case. You’ll feel it magnetically snap into place. This should create a triangular stand at the base of the flap that props up your tablet in the case. 5. To detach the case from the keyboard, simply pull the magnetized back flap away from the case.