Schottky Diode RF Detectors and RF Pulse Effects on CMOS Logic

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Extremely High-Gain Source-Gated Transistors

Extremely high-gain source-gated transistors Jiawei Zhanga,1, Joshua Wilsona,1, Gregory Autonb, Yiming Wangc, Mingsheng Xuc, Qian Xinc, and Aimin Songa,c,1,2 aSchool of Electrical and Electronic Engineering, University of Manchester, Manchester M13 9PL, United Kingdom; bNational Graphene Institute, University of Manchester, Manchester M13 9PL, United Kingdom; and cState Key Laboratory of Crystal Materials, Centre of Nanoelectronics and School of Microelectronics, Shandong University, Jinan 250100, People’s Republic of China Edited by Alexis T. Bell, University of California, Berkeley, CA, and approved January 29, 2019 (received for review December 6, 2018) Despite being a fundamental electronic component for over 70 turn-on voltage (19, 20). This susceptibility to negative bias illu- years, it is still possible to develop different transistor designs, mination temperature stress (NBITS) is one of the main factors including the addition of a diode-like Schottky source electrode delaying the wide-scale adoption of IGZO in the display industry. to thin-film transistors. The discovery of a dependence of the Another major problem is that TFTs require precise lithography source barrier height on the semiconductor thickness and deriva- to enable large-area uniformity, and difficulties with registration tion of an analytical theory allow us to propose a design rule to between different TFT layers are likely to be compounded by the achieve extremely high voltage gain, one of the most important use of flexible substrates. One major advantage of the SGT is that figures of merit for a transistor. Using an oxide semiconductor, an it does not require such precise registration, because the current intrinsic gain of 29,000 was obtained, which is orders of magni- is controlled by the dimensions of the source contact rather than tude higher than a conventional Si transistor. -

Lecture 3: Diodes and Transistors

2.996/6.971 Biomedical Devices Design Laboratory Lecture 3: Diodes and Transistors Instructor: Hong Ma Sept. 17, 2007 Diode Behavior • Forward bias – Exponential behavior • Reverse bias I – Breakdown – Controlled breakdown Æ Zeners VZ = Zener knee voltage Compressed -VZ scale 0V 0.7 V V ⎛⎞V Breakdown V IV()= I et − 1 S ⎜⎟ ⎝⎠ kT V = t Q Types of Diode • Silicon diode (0.7V turn-on) • Schottky diode (0.3V turn-on) • LED (Light-Emitting Diode) (0.7-5V) • Photodiode • Zener • Transient Voltage Suppressor Silicon Diode • 0.7V turn-on • Important specs: – Maximum forward current – Reverse leakage current – Reverse breakdown voltage • Typical parts: Part # IF, max IR VR, max Cost 1N914 200mA 25nA at 20V 100 ~$0.007 1N4001 1A 5µA at 50V 50V ~$0.02 Schottky Diode • Metal-semiconductor junction • ~0.3V turn-on • Often used in power applications • Fast switching – no reverse recovery time • Limitation: reverse leakage current is higher – New SiC Schottky diodes have lower reverse leakage Reverse Recovery Time Test Jig Reverse Recovery Test Results • Device tested: 2N4004 diode Light Emitting Diode (LED) • Turn-on voltage from 0.7V to 5V • ~5 years ago: blue and white LEDs • Recently: high power LEDs for lighting • Need to limit current LEDs in Parallel V R ⎛⎞ Vt IV()= IS ⎜⎟ e − 1 VS = 3.3V ⎜⎟ ⎝⎠ •IS is strongly dependent on temp. • Resistance decreases R R R with increasing V = 3.3V S temperature • “Power Hogging” Photodiode • Photons generate electron-hole pairs • Apply reverse bias voltage to increase sensitivity • Key specifications: – Sensitivity -

Comparing Trench and Planar Schottky Rectifiers

Whitepaper Comparing Trench and Planar Schottky Rectifiers Trench technology delivers lower Qrr, reduced switching losses and wider SOA By Dr.-Ing. Reza Behtash, Applications Marketing Manager, Nexperia The Schottky diode - named after its inventor, the German physicist Walter Hans Schottky - consists essentially of a metal-semiconductor interface. Because of its low forward voltage drop and high switching speed, the Schottky diode is widely used in a variety of applications, such as a boost diode in power conversion circuits. The electrical performance of a Schottky diode is, of course, subject to physical trade-offs, primarily between the forward voltage drop, the leakage current and the reverse blocking voltage. The Trench Schottky diode is a development on the original Schottky diode, providing greater capabilities than its planar counterpart. In this paper the structure and the benefits of Trench Schottky rectifiers are discussed. Schottky operation Trench technology The ideal rectifier would have a low forward voltage drop, Given this explanation, one might ask how the major a high reverse blocking voltage, zero leakage current and advantage of Schottky rectifiers - namely, a low voltage a low parasitic capacitance, facilitating a high switching drop across the metal semiconductor interface - is preserved, speed. When considering the forward voltage drop, despite the demand for a low leakage current and a high there are two main elements: the voltage drop across the reverse blocking voltage? Here, Trench rectifiers prove very junction - PN junction in case of PN rectifiers and metal- useful. The concept behind the Trench Schottky rectifier semiconductor junction in case of Schottky rectifiers; and is termed ‘RESURF’ (reduced surface field). -

Schottky Diode Replacement by Transistors: Simulation and Measured Results

SCHOTTKY DIODE REPLACEMENT BY TRANSISTORS: SIMULATION AND MEASURED RESULTS Martin Pospisilik Department of Computer and Communication Systems Faculty of Applied Informatics Tomas Bata University in Zlin 760 05, Zlin, Czech Republic E-mail: [email protected] KEYWORDS MOTIVATION Model, SPICE, MOSFET, Electronic Diode, Voltage The expansion of metal oxide field effect transistors has Drop, Power Dissipation led to efforts to substitute conventional diodes by electronic circuit that behave in the same way as the ABSTRACT diodes, but show considerably lower power dissipation The software support for simulation of electrical circuits as the voltage drop over the transistor can be eliminated has been developed for more than sixty years. Currently, to very low levels. In Fig. 1 there is a block diagram of a the standard tools for simulation of analogous circuits backup power source for the devices that use Power are the simulators based on the open source package over Ethernet technology. This solution, that has been Simulation Program with Integrated Circuit Emphasis developed at Tomas Bata University in Zlin, enables generally known as SPICE (Biolek 2003). There are immediate switching from the main supply to the backup many different applications that provide graphical one together with gentle charging of the accumulator, interface and extended functionalities on the basis of unlike the conventional on-line uninterruptable power SPICE or, at least, using SPICE models of electronic sources do (Pospisilik and Neumann 2013). devices. The author of this paper performed a simulation of a circuit that acts as an electronic diode in Multisim and provides a comparison of the simulation results with the results obtained from measurements on the real circuit. -

Basics of Transistors and Circuits Dr

BASICS OF TRANSISTORS AND CIRCUITS DR. HEATHER QUINN, LANL TEXTBOOK For these slides I am using many figures from the second edition of the Principles of CMOS VLSI Design by Weste and Esharaghain, and the fourth edition of CMOS VLSI Design: A Circuit and Systems Perspective INTRODUCTION There are two ways to view radiation effects in electronics: Start from the material science and work upward to transistors to circuits Start from computer circuits and work downward to transistors and then to material science There are advantages and disadvantages to both TOP/BOTTOM VS. BOTTOM/TOP Top/Bottom Bottom/Top Pros: Pros: Understanding of how the entire circuit Deep understanding of the mechanism works (sort of) Deep understanding the potential of the Understanding of the effect of electrical, effect, able to determine whether new temporal, and logical masking, which can be effects are possible used to limit the effects to the ones that cause noticeable effect Cons: Cons: Lack of understanding about electrical, temporal, and logical masking Hard to scale down to the material science Hard to scale up Might not understand the mechanism WHICH WAY TO GO? Likely depends on your background I’m a computer architect that learned radiation effects OJT, so I feel more comfortable personally going top down Some of my team is better versed in radiation effects are learning the circuit part OJT Either way, it is almost impossible to do both well, unless you would like to earn two PhDs, so working in teams is always best At the end of -

Design and Fabrication of Schottky Diode with Standard CMOS Process3

第 26 卷 第 2 期 半 导 体 学 报 Vol. 26 No. 2 2005 年 2 月 CHINESEJOURNAL OF SEMICONDUCTORS Feb. ,2005 Design and Fabrication of Schottky Diode with Standard CMOS Process 3 Li Qiang , Wang J unyu, Han Yifeng, and Min Hao ( State Key L aboratory of A S IC &System , Fudan U niversity , S hanghai 200433 , China) Abstract : Design and fabrication of Schottky barrier diodes (SBD) with a commercial standard 0135μm CMOS process are described. In order to reduce the series resistor of Schottky contact ,interdigitating the fingers of schottky diode layout is adopted. The I2V , C2V ,and S parameter are measured. The parameters of realized SBD such as the saturation current , breakdown voltage ,and the Schottky barrier height are given. The SPICE simulation model of the realized SBDs is given. Key words : CMOS; Schottky diode; integration EEACC : 2560H; 2570D CLC number : TN311 + 17 Document code : A Article ID : 025324177 (2005) 0220238205 sured results[5 ,6 ] . In this paper we describe the way to 1 Introduction design and layout a Schottky diode in a low cost com2 mercial standard CMOS process without any process Schottky diodes have advantages such as fast modification. The measured results and SPICE simu2 switching speed and low forward voltage drop. Due to lation model are offered. these excellent high frequency performance ,they have been widely used in power detection and microwave 2 Design and layout of Schottky diode network circuit [1 ] . Schottky diodes are often fabricat2 ed by depositing metals on n2type or p2type semicon2 This design was performed through MPW(multi ductor materials such as GaAs and SiC[2~4 ] . -

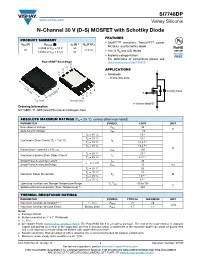

Si7748dp N-Channel 30 V (D-S) MOSFET with Schottky Diode

Si7748DP www.vishay.com Vishay Siliconix N-Channel 30 V (D-S) MOSFET with Schottky Diode FEATURES PRODUCT SUMMARY •SkyFETTM monolithic TrenchFET® power V (V) R (Ω)I (A) a Q (TYP.) DS DS(on) D g MOSFET and Schottky diode 0.0048 at VGS = 10 V 50 30 27.8 nC • 100 % R and UIS tested 0.0066 at VGS = 4.5 V 50 g • Material categorization: For definitions of compliance please see ® PowerPAK SO-8 Single www.vishay.com/doc?99912 D D 8 D APPLICATIONS 7 D D 6 5 • Notebook - Vcore low-side 6.15 mm 1 2 S Schottky Diode 3 S G 1 5.15 mm 4 S G Top View Bottom View N-Channel MOSFET Ordering Information: Si7748DP-T1-GE3 (lead (Pb)-free and halogen-free) S ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, unless otherwise noted) PARAMETER SYMBOL LIMIT UNIT Drain-Source Voltage V 30 DS V Gate-Source Voltage VGS ± 20 a TC = 25 °C 50 a TC = 70 °C 50 Continuous Drain Current (TJ = 150 °C) ID b, c TA = 25 °C 23.5 T = 70 °C 18.6 b, c A A Pulsed Drain Current (t = 100 μs) IDM 150 a TC = 25 °C 50 Continuous Source-Drain Diode Current IS b, c TA = 25 °C 4.3 Single Pulse Avalanche Current I 30 L = 0.1 mH AS Single Pulse Avalanche Energy EAS 45 mJ TC = 25 °C 56 TC = 70 °C 31 Maximum Power Dissipation PD b, c W TA = 25 °C 4.8 b, c TA = 70 °C 3 Operating Junction and Storage Temperature Range T , T -55 to 150 J stg °C Soldering Recommendations (Peak Temperature) d, e 260 THERMAL RESISTANCE RATINGS PARAMETER SYMBOL TYPICAL MAXIMUM UNIT Maximum Junction-to-Ambient b, f t ≤ 10 s R 21 26 thJA °C/W Maximum Junction-to-Case (Drain) Steady State RthJC 1.7 2.2 Notes a. -

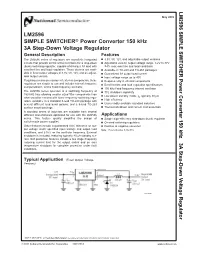

LM2596 SIMPLE SWITCHER Power Converter 150 Khz 3A Step-Down V

LM2596 SIMPLE SWITCHER Power Converter 150 kHz 3A Step-Down Voltage Regulator May 2002 LM2596 SIMPLE SWITCHER® Power Converter 150 kHz 3A Step-Down Voltage Regulator General Description Features The LM2596 series of regulators are monolithic integrated n 3.3V, 5V, 12V, and adjustable output versions circuits that provide all the active functions for a step-down n Adjustable version output voltage range, 1.2V to 37V (buck) switching regulator, capable of driving a 3A load with ±4% max over line and load conditions excellent line and load regulation. These devices are avail- n Available in TO-220 and TO-263 packages able in fixed output voltages of 3.3V, 5V, 12V, and an adjust- n Guaranteed 3A output load current able output version. n Input voltage range up to 40V Requiring a minimum number of external components, these n Requires only 4 external components regulators are simple to use and include internal frequency n Excellent line and load regulation specifications compensation†, and a fixed-frequency oscillator. n 150 kHz fixed frequency internal oscillator The LM2596 series operates at a switching frequency of n TTL shutdown capability 150 kHz thus allowing smaller sized filter components than n Low power standby mode, I typically 80 µA what would be needed with lower frequency switching regu- Q n lators. Available in a standard 5-lead TO-220 package with High efficiency several different lead bend options, and a 5-lead TO-263 n Uses readily available standard inductors surface mount package. n Thermal shutdown and current limit protection A standard series of inductors are available from several different manufacturers optimized for use with the LM2596 Applications series. -

Finalrell-PWR-Power-And-Energy

Rich, unique history of engineering, manufacturing and distributing 4 United Silicon Carbide, inc. is a semiconductor company specializing in the development of high efficiency Silicon Carbide (SiC) devices & foundry services with process expertise in Schottky Barrier Diodes, JFETs, MOSFETs, Solid State Circuit Breakers and Custom SiC integrated circuits. USCi technology and products enable affordable power efficiency in key markets that will drive • Leading technologythe new in High and Powered greener IGBT (Modules economy. 650-3300V & Discrete), MOSFETs, Bipolar & SiC Modules • Research & Development in Nuremburg Germany with manufacturing located in Jiaxing China. 3 operational fabs and New facility opened in Shanghai for focus on the EV market. • Heavy investments in R&D and development of new technologies—including “Sintering” and new die bonding. • Becoming 100% independent supplier. Star Power has control of own IGBT Chip Technology • Reliability, cost and lead time surpasses the competition with new chip technology. • http://www.starpowereurope.com/en Fuji Electric is a global manufacturer of Power Semiconductor products offering Industrial IGBT Power modules, High Power IGBT modules, Intelligent Power Modules, SiC devices (Hybrid & Full SiC), Discrete Rectifier Diodes, Discrete MOSFET & IGBT devices. • IGBT Modules- 10A-3600A 600V-3300V several topologies and packages • Gen 6 and Gen 7 X series now available • GEN 7 Reduces power dissipation, Achieves equipment size reduction, Contributes to improving equipment reliability • -

Sic Lateral Schottky Diode Technology for Integrated Smart Power Converter Jean-François Mogniotte, Christophe Raynaud, Mihai Lazar, Bruno Allard, Dominique Planson

SiC lateral Schottky diode technology for integrated smart power converter Jean-François Mogniotte, Christophe Raynaud, Mihai Lazar, Bruno Allard, Dominique Planson To cite this version: Jean-François Mogniotte, Christophe Raynaud, Mihai Lazar, Bruno Allard, Dominique Planson. SiC lateral Schottky diode technology for integrated smart power converter. 2018 IEEE ICIT, Feb 2018, Lyon, France. 10.1109/ICIT.2018.8352287. hal-01864545 HAL Id: hal-01864545 https://hal.archives-ouvertes.fr/hal-01864545 Submitted on 9 May 2019 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. SiC lateral Schottky diode technology for integrated smart power converter J. F. MOGNIOTTE C. RAYNAUD, M. LAZAR, B. ALLARD, D. Université de Lyon INSA-Lyon, ESTA School of business PLANSON and Technology, CNRS, AMPERE, UMR 5005 Université de Lyon INSA-Lyon, CNRS, AMPERE, F-69621, Villeurbanne, France UMR 5005 [email protected] F-69621, Villeurbanne, France Abstract— Ampere laboratory develops a technology of been characterized with a breakdown voltage of 1200 V and a lateral power integrated circuit in Silicon Carbide (SiC). The Ron of 4 mΩ/cm2. The ref [3] presents a PN diode with a purpose is to establish integrated power converter with its driver, breakdown voltage of 400 V. -

W2018 Digit2 Lecture08.Pdf

2018.04.22. DIGITAL TECHNICS II Dr. Bálint Pődör Óbuda University, Microelectronics and Technology Institute 8. LECTURE: LOGIC CIRCUITS III: ECL, SCHOTTKY TTL, CMOS AND BiCMOS 2nd (Spring) term 2017/2018 1 8. LECTURE 1. Digital IC technology picture gallery 2. Emitter coupled logic (ECL) 3. ”Classical” and high performance („advanced”) logic families, performance comparisons 4. Advanced Schottky TTL logic families 5. Advanced CMOS circuits and logic families 6. BiCMOS logic families 1 2018.04.22. INTEGRATED CIRCUIT ETCHNOLOGY Manufacturing technology of microelectronic (and MEMS) devices and chips. Basic material: semiconductor single crystal (silicon,Si) Processing : Additive steps: thin layer deposition – PVD, CVD, oxidation, patterning Modification steps: fotoexposition, ion implantation doping, thermal processing steps Subtractive steps: Chemical and physical etching steps, laser-assisted and mechanical layer removal Wafer technology: Sequential application of the above steps and their combinations on the surface of the wafer 3 IC TECHNOLOGY FLOW DIAGRAM Schematic flow diagram of IC fabrication 4 2 2018.04.22. SILICON INGOT AND WAFERS 300 mm (12 in.) dia ingot and polished silicon wafers5 TECHNOLOGY BASICS Batch processing 10 to 50 thousands chips in one step. Clean room in an IC fab 6 3 2018.04.22. HIGH CLEANNESS CONDITIONS IC processing, especially lithography: only under very high cleanness conditions, clean room. US Federal Standard: level100: less than 100 particle larger than 0.5 m. Submicron lithography: level10 and level 1 clean rooms. Extremely expensive! 7 IC FAB COSTS Cost of IC manufacturing clean rooms in function of time (calendar year) 8 4 2018.04.22. TECHNOLOGY BASICS Wafer and chip: ca. -

FDFMA2P853 Integrated P-Channel Powertrench® MOSFET And

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body.