Industrial Ethernet PHY Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1) What Is the Name of an Ethernet Cable That Contains Two

1) What is the name of an Ethernet cable that contains two electrical conductors ? A coaxial cable 2) What are the names of the two common conditions that degrade the signals on c opper-based cables? Crosstal and attenuation 3) Which topology requires the use of terminators? Bus 4) Which of the following topologies is implemented only logically, not physical ly? Ring 5) How many wire pairs are actually used on a typical UTP Ethernet network? Two 6) What is the name of the process of building a frame around network layer info rmation? Data encapsulation 7) Which of the connectors on a network interface adapter transmits data in para llel? The System bus connector 8) Which two of the following hardware resources do network interface adapters a lways require? I/O port address and IRQ 9) What is the name of the process by which a network interface adapter determin es when it should transmit its data over the network? Media Access Control 10) Which bus type is preferred for a NIC that will be connected to a Fast Ether net network? PCI 11) A passive hub does not do which of the following? Transmit management information using SNMP 12) To connect two Ethernet hubs together, you must do which of the following? Connect the uplink port in one hub to a standard port on the other 13) Which term describes a port in a Token Ring MAU that is not part of the ring ? Intelligent 14) A hub that functions as a repeater inhibits the effect of____________? Attenuation 15) You can use which of the following to connect two Ethernet computers togethe r using UTP -

DIO Wireless Transceiver

M O C I U T N I DIO Wireless Transceiver MULTIFUNCTIONAL CONTACT CLOSURE SOLUTION R E FUNCTIONALITY AND FLEXIBILITY V KEY FEATURES I The Intuicom DIO provides bi-directional E • “Best-in-Class” RF C communication with 16 individual channels, performance S eight (8) input and eight (8) output, for a • Robust on-off control and N virtually limitless number of I/O routing possi- monitoring of multiple A bilities including positive confirmation of events R command execution. T • Long range, error free, low latency performance S • Eight (8) dry contact/low S “BEST-IN-CLASS” RF PERFORMANCE E voltage input channels L Employing Intuicom’s robust and secure • Eight (8) open collector E The Intuicom DIO is a high performance frequency hopping spread spectrum output channels R technology, the Intuicom DIO is inherently I wireless contact closure radio for • Software mapping of input resistant to interference from other RF and output channels W ON-OFF and Detection applications. Designed for short and long-range error- equipment including other spread spectrum • Confirmation ability O radios. Empowered with an ultra-sensitive, • I free communications, the DIO delivers a Single Unit Operation™, highly-selective RF transceiver, the Intuicom D Any one unit may serve as complete bi-directional wireless I/O DIO provides real-time, robust communication Master, Remote, Repeater capability for point-to-point, point-to- links with 32-bit CRC with error correction. or Remote/Repeater multipoint and multipoint-to-multipoint The Intuicom DIO is capable of delivering the • 900 MHz or 2.4 GHz applications, providing an alternative to maximum output power allowable by the FCC license free operation hardwire, fiber and other RF solutions. -

Gigabit Ethernet - CH 3 - Ethernet, Fast Ethernet, and Gigabit Ethern

Switched, Fast, and Gigabit Ethernet - CH 3 - Ethernet, Fast Ethernet, and Gigabit Ethern.. Page 1 of 36 [Figures are not included in this sample chapter] Switched, Fast, and Gigabit Ethernet - 3 - Ethernet, Fast Ethernet, and Gigabit Ethernet Standards This chapter discusses the theory and standards of the three versions of Ethernet around today: regular 10Mbps Ethernet, 100Mbps Fast Ethernet, and 1000Mbps Gigabit Ethernet. The goal of this chapter is to educate you as a LAN manager or IT professional about essential differences between shared 10Mbps Ethernet and these newer technologies. This chapter focuses on aspects of Fast Ethernet and Gigabit Ethernet that are relevant to you and doesn’t get into too much technical detail. Read this chapter and the following two (Chapter 4, "Layer 2 Ethernet Switching," and Chapter 5, "VLANs and Layer 3 Switching") together. This chapter focuses on the different Ethernet MAC and PHY standards, as well as repeaters, also known as hubs. Chapter 4 examines Ethernet bridging, also known as Layer 2 switching. Chapter 5 discusses VLANs, some basics of routing, and Layer 3 switching. These three chapters serve as a precursor to the second half of this book, namely the hands-on implementation in Chapters 8 through 12. After you understand the key differences between yesterday’s shared Ethernet and today’s Switched, Fast, and Gigabit Ethernet, evaluating products and building a network with these products should be relatively straightforward. The chapter is split into seven sections: l "Ethernet and the OSI Reference Model" discusses the OSI Reference Model and how Ethernet relates to the physical (PHY) and Media Access Control (MAC) layers of the OSI model. -

FCC Element 1 Question Pool

FCC Commercial Element 1 Question Pool (approved 25 June 2009) Subelement A – Rules & Regulations: 6 Key Topics, 6 Exam Questions Key Topic 1: Equipment Requirements 1-1A1 What is a requirement of all marine transmitting apparatus used aboard United States vessels? A. Only equipment that has been certified by the FCC for Part 80 operations is authorized. B. Equipment must be type-accepted by the U.S. Coast Guard for maritime mobile use. C. Certification is required by the International Maritime Organization (IMO). D. Programming of all maritime channels must be performed by a licensed Marine Radio Operator. 1-1A2 What transmitting equipment is authorized for use by a station in the maritime services? A. Transmitters that have been certified by the manufacturer for maritime use. B. Unless specifically excepted, only transmitters certified by the Federal Communications Commission for Part 80 operations. C. Equipment that has been inspected and approved by the U.S. Coast Guard. D. Transceivers and transmitters that meet all ITU specifications for use in maritime mobile service. 1-1A3 Small passenger vessels that sail 20 to 150 nautical miles from the nearest land must have what additional equipment? A. Inmarsat-B terminal. B. Inmarsat-C terminal. C. Aircraft Transceiver with 121.5 MHz. D. MF-HF SSB Transceiver. 1-1A4 What equipment is programmed to initiate transmission of distress alerts and calls to individual stations? A. NAVTEX. B. GPS. C. DSC controller. D. Scanning Watch Receiver. 1-1A5 What is the minimum transmitter power level required by the FCC for a medium-frequency transmitter aboard a compulsorily fitted vessel? A. -

MIMO Transceiver with Afe76xx for LTE and 5G Wireless Radio

www.ti.com Table of Contents Application Report MIMO Transceiver with AFE76xx for LTE and 5G Wireless Radio Ebenezer Dwobeng ABSTRACT In this application report, the implementation and performance of a radio transceiver suitable for multiple-input multiple-output (MIMO) wireless communications will be presented. AFE76xx is the main device used for the transceiver design. This device integrates 4 analog-to-digital converters (ADCs), 4 digital-to-analog converters (DACs) and a phase-locked loop (PLL) for sampling clock generation. The main advantage of this MIMO transceiver implementation is the high level of integration, which makes it easier to expand to larger antenna arrays via synchronization of multiple AFE76xx devices. Also the direct RF-sampling based data converters eliminate common analog impairments in radio transceiver design such as local oscillator (LO) leakage and sideband image. Table of Contents 1 Introduction.............................................................................................................................................................................2 2 System Overview.................................................................................................................................................................... 4 3 Constellation........................................................................................................................................................................... 8 4 Error Vector Magnitude (EVM)...............................................................................................................................................9 -

Radio Transceiver System Design with Emphasis on Parameters Which Affect Range

www.vanteon.com Radio Transceiver System Design With Emphasis on Parameters Which Affect Range Tony Manicone, Principal RF Engineer September 2012 Fig 1 1 www.vanteon.com ABSTRACT This paper will describe the basic impairments which reduce communications range in a radio system. Typically these are factors such as: Transmit Power and losses in the transmit chain, Power Amplifier non-linearity, etc. Receiver and Transmitter antenna choice, grounding, location, and impedance matching. Propagation path impairments such as Free Space Loss, Absorption (building materials, vegetation, moisture, etc), Multipath Destructive Interference, Fading, etc. Receiver Sensitivity and criteria which affect it such as Noise Figure, Bandwidth, Signal to Noise Ratio, Phase Noise, etc. The ramifications of each of these effects would be discussed in terms of degradation to communications range as well as the “cost” of poor design practices. The paper is aimed at people who currently use or need a radio communications system and want to learn many of the basic issues and constraints which affect communications range and radio design. The discussion is presented in several parts: Antennas Propagation Path Transmitter issues Receiver issues Process Gain Enhancements Communications range estimation calculations using a 2.4 GHz radio as an example. Some of the topics will be mentioned only briefly, as a full discussion is beyond the scope of this presentation, yet they are important issues that need to be touched on. 2 www.vanteon.com FUNDAMENTAL RADIO TRANSMISSION SYSTEM ANTENNA ANTENNA RADIO PROPAGATION RADIO TRANSMITTER PATH RECEIVER BASEBAND INPUT BASEBAND OUTPUT (Voice, Data, Video) (Voice, Data, Video) MODULATED MODULATED RADIO WAVE RADIO WAVE Fig 2 Fundamental Radio Transmission System All Radio transmission systems require, at a minimum: A Radio Transmitter, which converts (modulates) lower frequency baseband signals (data, voice, video…) onto higher frequency radio waves. -

10BASE-T1S Learn to Run Supported by Embedded Software

10BASE-T1S Learn To Run Supported by Embedded Software V1.1 | 2021-06-11 Agenda 1. All IP Car 2. Extensions in AUTOSAR 3. Areas of Investigation 4. Evaluation SW Setup Based on the Infineon Evaluation Kit 2 All IP Car 10BASE-T1S as Replacement for Lower Bandwidth Networks IP as well-known common “language” proven in use technology enabler for E/E architecture trends and service-based communication and Ethernet is the naturally associated Network Access Layer 3 All IP Car Introducing an Additional Network Access Layer It’s more than just physical layer compliance The digital eco-system must be “ready” Tools, data models and databases SW AUTOSAR … 4 Extensions in AUTOSAR 10BASE-T1S Within AUTOSAR Classic Platform 10BASE-T1S was introduced as new concept in R20-11 Further refinement is currently ongoing within AUTOSAR It’s Ethernet the upper layer stack remains untouched Utilize the benefits of the strictly layered architecture Encapsulate the changes in the MCAL layer Ethernet Driver Ethernet Switch Driver Ethernet Transceiver Driver Eth EthSwt EthTrcv 5 Areas of Investigation Extension of the Existing MICROSAR Solution Ethernet Transceiver Driver Ethernet Driver 10BASE-T1S specific initializations Depending on actual Transceiver device Timeline is depending on documentation and device availability Diagnostic Interface Error and State Management Transmit Buffer Management 6 Evaluation SW Setup Based on the Infineon Evaluation Kit Specific SIP – Software Integration Package Fixed Compile Environment Infineon TriBoard -

Datasheet - Public

Marvell® Alaska® 88E1510/88E1518/88E1512/88E1514 Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver Datasheet - Public Doc. No. MV-S107146-U0 Rev. E June 3, 2021 Document Classification: Public Cover Alaska 88E1510/88E1518/88E1512/88E1514 Datasheet - Public THIS DOCUMENT AND THE INFORMATION FURNISHED IN THIS DOCUMENT ARE PROVIDED "AS IS" WITHOUT ANY WARRANTY. MARVELL AND ITS AFFILIATES EXPRESSLY DISCLAIM AND MAKE NO WARRANTIES OR GUARANTEES, WHETHER EXPRESS, ORAL, IMPLIED, STATUTORY, ARISING BY OPERATION OF LAW, OR AS A RESULT OF USAGE OF TRADE, COURSE OF DEALING, OR COURSE OF PERFORMANCE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT. This document, including any software or firmware referenced in this document, is owned by Marvell or Marvell's licensors, and is protected by intellectual property laws. No license, express or implied, to any Marvell intellectual property rights is granted by this document. The information furnished in this document is provided for reference purposes only for use with Marvell products. It is the user's own responsibility to design or build products with this information. Marvell products are not authorized for use as critical components in medical devices, military systems, life or critical support devices, or related systems. Marvell is not liable, in whole or in part, and the user will indemnify and hold Marvell harmless for any claim, damage, or other liability related to any such use of Marvell products. Marvell assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. -

TR-200 Using EPON in the Context of TR-101

TECHNICAL REPORT TR-200 Using EPON in the Context of TR-101 Issue: 1 Corrigendum 1 Issue Date: July 2011 © The Broadband Forum. All rights reserved. Using EPON in the Context of TR-101 TR-200 Issue 1 Corrigendum 1 Notice The Broadband Forum is a non-profit corporation organized to create guidelines for broadband network system development and deployment. This Broadband Forum Technical Report has been approved by members of the Forum. This Broadband Forum Technical Report is not binding on the Broadband Forum, any of its members, or any developer or service provider. This Broadband Forum Technical Report is subject to change, but only with approval of members of the Forum. This Technical Report is copyrighted by the Broadband Forum, and all rights are reserved. Portions of this Technical Report may be copyrighted by Broadband Forum members. This Broadband Forum Technical Report is provided AS IS, WITH ALL FAULTS. ANY PERSON HOLDING A COPYRIGHT IN THIS BROADBAND FORUM TECHNICAL REPORT, OR ANY PORTION THEREOF, DISCLAIMS TO THE FULLEST EXTENT PERMITTED BY LAW ANY REPRESENTATION OR WARRANTY, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY WARRANTY: (A) OF ACCURACY, COMPLETENESS, MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT, OR TITLE; (B) THAT THE CONTENTS OF THIS BROADBAND FORUM TECHNICAL REPORT ARE SUITABLE FOR ANY PURPOSE, EVEN IF THAT PURPOSE IS KNOWN TO THE COPYRIGHT HOLDER; (C) THAT THE IMPLEMENTATION OF THE CONTENTS OF THE TECHNICAL REPORT WILL NOT INFRINGE ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADEMARKS OR OTHER RIGHTS. By using this Broadband Forum Technical Report, users acknowledge that implementation may require licenses to patents. -

Physical Layer Compliance Testing for 1000BASE-T Ethernet

Physical Layer Compliance Testing for 1000BASE-T Ethernet –– APPLICATION NOTE Physical Layer Compliance Testing for 1000BASE-T Ethernet APPLICATION NOTE Engineers designing or validating the 1000BASE-T Ethernet 1000BASE-T Physical Layer physical layer on their products need to perform a wide range Compliance Standards of tests, quickly, reliably and efficiently. This application note describes the tests that ensure validation, the challenges To ensure reliable information transmission over a network, faced while testing multi-level signals, and how oscilloscope- industry standards specify requirements for the network’s resident test software enables significant efficiency physical layer. The IEEE 802.3 standard defines an array of improvements with its wide range of tests, including return compliance tests for 1000BASE-T physical layer. These tests loss, fast validation cycles, and high reliability. are performed by placing the device under test in test modes specified in the standard. The Basics of 1000BASE-T Testing While it is recommended to perform as many tests as Popularly known as Gigabit Ethernet, 1000BASE-T has been possible, the following core tests are critical for compliance: experiencing rapid growth. With only minimal changes to IEEE 802.3 Test Mode Test the legacy cable structure, it offers 100 times faster data Reference rates than 10BASE-T Ethernet signals. Gigabit Ethernet, in Peak 40.6.1.2.1 combination with Fast Ethernet and switched Ethernet, offers Test Mode-1 Droof 40.6.1.2.2 Template 40.6.1.2.3 a cost-effective alternative to slow networks. Test Mode-2 Master Jitter 40.6.1.2.5 Test Mode-3 Slave Jitter 1000BASE-T uses four signal pairs for full-duplex Distortion 40.6.1.2.4 transmission and reception over CAT-5 balanced cabling. -

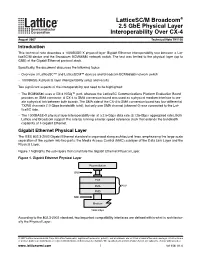

Latticesc/M Broadcom® 2.5 Gbe Physical Layer Interoperability Over CX-4

LatticeSC/M Broadcom® 2.5 GbE Physical Layer Interoperability Over CX-4 August 2007 Technical Note TN1156 Introduction This technical note describes a 1000BASE-X physical layer Gigabit Ethernet interoperability test between a Lat- ticeSC/M device and the Broadcom BCM56580 network switch. The test was limited to the physical layer (up to GMII) of the Gigabit Ethernet protocol stack. Specifically, the document discusses the following topics: • Overview of LatticeSC™ and LatticeSCM™ devices and Broadcom BCM56580 network switch • 1000BASE-X physical layer interoperability setup and results Two significant aspects of the interoperability test need to be highlighted: • The BCM56580 uses a CX-4 HiGig™ port, whereas the LatticeSC Communications Platform Evaluation Board provides an SMA connector. A CX-4 to SMA conversion board was used as a physical medium interface to cre- ate a physical link between both boards. The SMA side of the CX-4 to SMA conversion board has four differential TX/RX channels (10 Gbps bandwidth total), but only one SMA channel (channel 0) was connected to the Lat- ticeSC side. • The 1000BASE-X physical layer interoperability ran at a 2.5-Gbps data rate (3.125-Gbps aggregated rate). Both Lattice and Broadcom support this rate by running a faster speed reference clock that extends the bandwidth capability of 1-Gigabit Ethernet. Gigabit Ethernet Physical Layer The IEEE 802.3-2002 Gigabit Ethernet standard is organized along architectural lines, emphasizing the large-scale separation of the system into two parts: the Media Access Control (MAC) sublayer of the Data Link Layer and the Physical Layer. Figure 1 highlights the sub-layers that constitute the Gigabit Ethernet Physical Layer. -

Wifire: Medium Access Control (MAC) and Physical Layer (PHY) Specifications

WiFiRe Specifications, Aug 2006 draft Broadband Wireless for Rural Areas -- WiFiRe : Medium Access Control (MAC) and Physical Layer (PHY) Specifications Release 2006 (This document is - Aug 2006 draft) Center of Excellence in Wireless Technology (CEWiT) 1 Copyright © 2006 CEWiT, Some rights reserved WiFiRe Specifications, Aug 2006 draft About CEWiT The Centre of Excellence in Wireless Technology (CEWiT), India , has been set up under a public-private initiative with the mission of making India a leader in the research, development and deployment of wireless technology. It is an autonomous institution temporarily headquartered at IIT Madras. Broadband wireless technology has great potential in the coming years. Emerging standards can be leveraged to build a system that specifically meets India’s broadband access needs. CEWiT will play a pro-active role in engaging with academic and industry research groups in India to focus research on areas with strong potential. CEWiT will also foster collaboration with similar efforts worldwide. CEWiT seeks to actively participate in International standards bodies, and to assist government and public institutions in policy-making, spectrum management and regulation. CEWiT Std, WiFiRe, 2006 Edition CEWiT standards are developed within the Technical Committees of CEWiT. Members of the committees serve voluntarily and without any compensation. The standards developed within CEWiT represent a consensus of the broad expertise of the subject. The existence of a CEWiT standard does not imply that there are no other ways to provide services related to the scope of the standard. Furthermore, a standard is subject to change brought about through developments in the state of the art and comments received from the users of the standard.