DAC161S055 Precision 16-Bit, Buffered Voltage-Output DAC Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

T E L L T a L E S a R a T O G a L a K E S a I L I N G C L U B

What's Inside? T e l l t a l e S a r a t o g a L a k e S a i l i n g C l u b Web page: sailsaratoga.org May, 2016 Commodore’s Corner SLSC By Mark Welcome Annual Memorial Day It’s time to go sailing! Champagne Brunch The Club is in great shape and the docks are all in as of the Monday, May 30 April 30th work party. We had 120 memberships 10:00 AM - Noon represented at the first work party and were able to accomplish almost everything that was on our lists. Not to Adults $10 - Kids (12 and under) $5 worry, we have more than enough work to add to our lists th Champagne market price per bottle for Work Party #2 which will be on Saturday May 7 . Planned work details include getting the mooring field ready, Reservations no later than May 22 to more house cleaning, additional work on school boats and any number of projects on the grounds. We look forward to seeing many of you who couldn’t make the first work party at [email protected] the second work party so we can finish opening up the club Email reservations are preferred, and will be and start the sailing season off right. If you are unable to acknowledged! participate in the work parties, please contact John Smith, Melissa Tkal, Greg Tkal, JT Fahy, David Hudson or myself or call to see if they need help with additional projects. Given that Kathleen & Vic Roberts we are a volunteer run organization, there are always 399-4410 projects to do and we appreciate the help of all the members. -

Virginia USGS River Input Monitoring QA Project Plan

QUALITY ASSURANCE PROJECT PLAN for the Virginia River Input Monitoring Program Prepared by Douglas L. Moyer U.S. Geological Survey 1730 E. Parham Road Richmond, VA 23228 for Virginia Department of Environmental Quality Chesapeake Bay Office PO Box 1105 Richmond, VA 23218 Effective August 2016 Approvals: Douglas Moyer, Project Manager, USGS Date Douglas Chambers, Acting Water-Quality Specialist, USGS Date Cindy Johnson, Project Officer, VDEQ Date Cindy Johnson, Quality Assurance Officer, VDEQ Date Peter Tango, Project Officer, US EPA Date Rich Batiuk, Quality Assurance Officer, US EPA Date QUALITY ASSURANCE PROJECT PLAN for the Virginia River Input Monitoring Program Prepared by: Douglas L. Moyer U.S. Geological Survey for Virginia Department of Environmental Quality Chesapeake Bay Office Richmond, VA updated August, 2016 2 TABLE OF CONTENTS I. PROJECT DESCRIPTION 4 II. PROJECT ORGANIZATION AND RESPONSIBILITY 18 III. QA OBJECTIVES AND CRITERIA 21 IV. SAMPLING PROCEDURES 25 V. SAMPLE CUSTODY 26 VI. CALIBRATION PROCEDURES AND FREQUENCY 27 VII. ANALYTICAL PROCEDURES 28 VIII. DATA REDUCTION, VALIDATION, AND REPORTING 29 IX. INTERNAL QC CHECKS 30 X. PERFORMANCE AND SYSTEM AUDITS 31 XI. PREVENTATIVE MAINTENANCE 31 XII. ASSESSMENT OF DATA VARIABILITY, BIAS, ACCURACY, REPRESENTATIVE- NESS, AND COMPLETENESS 32 XIII. CORRECTIVE ACTION FOR OUT-OF-CONTROL SITUATIONS 32 XIV. QA REPORTING PROCEDURES 33 3 I. PROJECT DESCRIPTION A. Background Quantification of the loads of nutrient and suspended solids into the Chesapeake Bay, and evaluation of the trends in constituent loads are necessary in order to determine the effects that these constituents have on the ecosystems of the Chesapeake Bay. The Virginia River Input Monitoring Program (formerly known as the Virginia Fall Line Nutrient Input Program) was developed to quantify and assess the effectiveness of programs aimed at reducing the impact of nutrient and suspended solid inputs. -

2018 Membership Directory

Established 1969 2018 2018 Membership Directory 2018 OFFICERS Commodore: Mark Walker Vice Commodore: Geoff Endris Treasurer: Tom Moore Welcome to Eagle Creek Sailing Club! We were established Secretary: Rich Fox in 1969 to "encourage, sponsor and develop recreational and competitive sailing on Eagle Creek Reservoir." Over the Past Commodore: Larry Conrad years, the club has built a wonderful facility and established many programs and events to achieve this. We have very COMMITTEE CHAIRS competitive club racing on Wednesday nights and friendly Sunday Fun-Day racing on Sunday afternoons. We have a Harbormaster: Dennis Robertson myriad of social events, including holiday pitch-ins, a Lobster Assistant: Jan Wishart Fest, and our year-end Final Bash. We have a well- Membership: Jane Schmidt established and very active youth sailing program that competes in regattas all season. They also hold two weeks of Assistant: Christy Merriman Summer Sailing Camp that has become more popular every Publicity: Rick Graef year (get your reservations in early). The club hosts four Racing: Bob Hickock regattas every year, and we encourage everybody to Assistant: John George participate in the Saturday evening regatta dinner and party whether you raced or not. Information on these events can be Safety / Education: Chuck Lessick found on our website at “ecsail.org.” Assistant: Wayne Myers The club belongs to the ILYA (Inland Lake Yachting Ship Store: Les Miller Association) and the YCA (Yachting Club of America). These Social: Vickie Greenough memberships give us privileges at other clubs that belong to those associations. More information can be found on their websites. Keep this in mind when traveling and use the CURRENT BOARD MEMBERS opportunity to visit other yachting and sailing clubs. -

Data Collection Requirements and Procedures for Mapping Wetland, Deepwater, and Related Habitats of the United States (Version 3)

Data Collection Requirements and Procedures for Mapping Wetland, Deepwater, and Related Habitats of the United States (version 3) U.S. FISH & WILDLIFE SERVICE - ECOLOGICAL SERVICES DIVISION OF BUDGET AND TECHNICAL SUPPORT BRANCH OF GEOSPATIAL MAPPING AND TECHNICAL SUPPORT FALLS CHURCH, VA 2204 REVISED JULY 2020 1 Acknowledgements The authors would like to acknowledge the following individuals for their support and contributions: Bill Kirchner, USFWS, Region 1, Portland, OR; Elaine Blok, USFWS, Region 8, Portland, OR Brian Huberty, USFWS, Region 3, Twin Cities, MN; Ralph Tiner, USFWS, Region 5, Hadley, MA: Kevin Bon, USFWS, Region 6, Denver, CO; Jerry Tande, USFWS, Region 7, Anchorage, AK; Julie Michaelson, USFWS, Region 7, Anchorage, AK; Norm Mangrum, USFWS, St. Petersburg, FL; Dennis Fowler, USFWS, St. Petersburg, FL; Jim Terry, USFWS, St. Petersburg, FL; Martin Kodis, USFWS, Chief - Branch of Resources and Mapping Support, Washington, D.C. and David J. Stout, USFWS, Chief - Division of Habitat and Resource Conservation, Washington, D.C. Peer review was provided by the following subject matter experts: Dr. Shawna Dark and Danielle Bram, California State University - Northridge. Robb Macleod, Ducks Unlimited, Great Lakes and Atlantic Regional Office, Ann Arbor, MI; Michael Kjellson, Dept. Wildlife and Fisheries, South Dakota State University, Brookings, SD; and Deborah (Jane) Awl, Tennessee Valley Authority, Knoxville, TN. This document may be referenced as: Dahl, T.E., J. Dick, J. Swords, and B.O. Wilen. 2020. Data Collection Requirements and Procedures for Mapping Wetland, Deepwater and Related Habitats of the United States. Division of Habitat and Resource Conservation (version 3), National Wetlands Inventory, Madison, WI. 91 p. -

Modern Challenges in Distribution O-F.De High Voltage? RELAX!

ISSN: 1863-5598 ZKZ 64717 01-14 Electronics in Motion and Conversion January 2014 Modern Challenges in Distribution o-f.de High voltage? RELAX! Medium voltage components for power electronics Does this sound familiar? Voltage increases, whenever it is least expected. Good for thrillers. Not so good for power electronic installations. That is why we developed our “ready-to-use switch components” based on IGBT and Thyristor technology, specifically for use in MV applications. They are even available with or without control or current loop feed power supply. So sit back, relax and look forward to an exciting conversation with your House of Competence. It's worth it. MV IGBT DC switches MV Thyristor AC switches engineered by MV IGBT / Thyristor control MV current loop feed power supply Welcome to the House of Competence. GvA Leistungselektronik GmbH | Boehringer Straße 10 - 12 | D-68307 Mannheim Phone +49 (0) 621/7 89 92-0 | www.gva-leistungselektronik.de | [email protected] CONTENT Read online and search for key subjects from all articles in Bodo’s Power Systems by going to Powerguru: Viewpoint . 4 Power Supply . 24 Progress in SiC and GaN - Good Things for the New Year Pin-Compatible Switcher Replacement for TO220-Style Linear Regulators Events . 4 By Matthias Ulmann, Texas Instruments News . 6-9 Automotive Power . 28-30 Blue Product of the Month . 10 5. eCarTec 2013 Munich: Connecting Mobility Markets Compact Converter Series COMPISO By Marisa Robles Consée, Corresponding Editor; Egston Bodo’s Power Systems Green Product of the Month . 12 Lighting . 32-33 Win a dsPICDEM™ MCLV-2 Development Board LED professional Symposium + Expo 2013; The Lighting Hub Microchip By Marisa Robles Consée, Corresponding Editor; Bodo’s Power Systems Guest Editorial . -

Guadamuz2013.Pdf (5.419Mb)

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use: • This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated. • A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. • This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author. • The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author. • When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given. Networks, Complexity and Internet Regulation Scale-Free Law Andres Guadamuz Submitted in accordance with the requirements for the degree of Doctor of Philosophy by Publication(PhD) The University of Edinburgh February 2013 The candidate confirms that the work submitted is his/her own and that appropriate credit has been given where reference has been made to the work of others. © Andrés Guadamuz 2013 Some rights reserved. This work is Licensed under a Creative Commons Attribution-NonCommercial- ShareAlike 3.0 Unported License. Contents Figures and Tables ix Figures ix Tables x Abbreviations xi Cases xv Acknowledgments xvii License xix Attribution-NonCommercial-NoDerivs 3.0 Unported xix 1. Introduction 1 A short history of psychohistory 3 Objectives 10 Some notes on methodology 13 2. The Science of Complex Networks 15 1. -

Tell Tales Issue 1 January 2007

Lake Townsend Yacht Club PO Box 4002 Greensboro NC 27404-4002 www.laketownsendyachtclub.com/ Tell Tales Issue 1 January 2007 Schedule of LTYC Events EVENT DATE TIME LOCATION Board of Directors Thursday, 1 1745 hrs Greensboro College Campus in Room Meeting February 2007 226 of Proctor Hall West Frostbite Series Saturday, 3 Skippers Meeting Lake Townsend Marina February 2007 1100 hrs Race Committee Members needed! SAYRA Annual Meeting 2-4 February Augusta, GA 2007 Trophies awarded for 2005-2006 Race Board Meeting Meets on February 1 Series The Board of Directors meeting is open to all Club Trophies for the Lake Townsend Yacht Club 2005- members. At the January Board meeting, the Board 2006 Frostbite Series were presented to John decided to continue to meet on the Greensboro Hemphill, First Place and Steve Morris, Second College Campus in Room 226 of Proctor Hall West. Place. January Frostbite Series For the Lake Townsend Yacht Club 2006 Saturday Hardly frostbite conditions! One competitor Summer Series Monohull Fleet trophies were described it as possibly the best day of sailing we presented to Ken Warren, First Place; John will have this year. Indeed, what was not to like, Hemphill, Second Place and David Raper, temperature in the high 60s and winds 10 knots Third Place. diminishing to 4.5 knots. Well the wind did shift around throughout the day but, hey, this is Lake For the Lake Townsend Yacht Club 2006 Saturday Townsend, it is always shifting. Summer Series Isotope Fleet, trophies were presented to Eric Rasmussen, First Place; and Alan Change of Watch Banquet Held! Wolfe and Joleen Rasmussen, Thirty-eight members of the yacht club gathered Second Place. -

Tell Tales Issue 11 November 2005

Lake Townsend Yacht Club PO Box 4002 Greensboro NC 27404-4002 www.greensboro.com/ltyc Tell Tales Issue 11 November 2005 Schedule of LTYC Events EVENT DATE TIME LOCATION Board of Directors 1 December 2005 1745 hrs Benjamin Pkwy Public Library Branch Meeting Frostbite Series Begins 3 December Skippers Meeting Lake Townsend Marina 2005 1100 hrs Board of Directors 5 January 2006 1745 hrs Benjamin Pkwy Public Library Branch Meeting Frostbite Series 7 January 2006 Skippers Meeting Lake Townsend Marina 1100 hrs Change of Watch Banquet 14 January 2003 TBA TBA Inter-club Regatta Report On Saturday November 4, members of the Oak The following skippers sailed for LTYC: Hollow Yacht Club joined members of LTYC on Lake Townsend for the annual Inter-club Bill Grossie Buccaneer Regatta. It was a beautiful day for sailing. Keith Smoot Snark The temperature was in the low 70s and winds George Bageant Tanzer 690 moderate but variable. Jere Woltz, PRO was Steve Morris FS 3500 able to set a windward-leeward course for the Esther Khoury Tanzer 1440 first two races in 4-7 mph winds and for the John Russell FS 2300 last race; he set a modified Olympic course. Rudy Cordon Capri 4645 Pete Thorn Tanzer 1427 The Lake Townsend Yacht Club retained the John Hemphill FS 4043 Neil Benson Inter Club Cup winning all three of the races. The following skippers sailed for OHYC: John Wikle Capri 4646 Charles Eldred Hobie 80666 Harry Herman Hobie 16 77747 W. Mitchell Hobie 16 86425 Nancy Valego Hobie 1 501 Art Martz Precision 16 999 The Results Race 3 (LTYC 16 points-OHYC 39 points) Results with finishing order based on corrected elapsed time with the top 5 boats FS 4043 First LTYC from each club reported: FS 2300 2 LTYC Tanzer 1427 3 LTYC Race 1 (LTYC 21 points- OHYC 34 Snark 4 LTYC points) The winner has the lowest points. -

Horseshoe Crab Management Board

Atlantic States Marine Fisheries Commission Horseshoe Crab Management Board October 31, 2013 10:15 a.m. – 12:15 p.m. St. Simons Island, Georgia DRAFT Agenda The times listed are approximate; the order in which these items will be taken is subject to change; other items may be added as necessary. 1. Welcome/Call to order (D. Simpson) 10:15 a.m. 2. Board Consent 10:15 a.m. • Approval of Agenda • Approval of Proceedings from May 2013 3. Public comment 10:20 a.m. 4. 2013 Stock Assessment Update Action 10:25 a.m. • Presentation of Stock Assessment Report (P. Howell) • Consider acceptance of stock assessment update for management use 5. Horseshoe Crab Technical Committee Report (P. Howell) 11:15 a.m. • Review Asian horseshoe crab bans • Proposed listing of red knots • Use of alternative bait in conch and eel fisheries 6. Delaware Bay Ecosystem Technical Committee Reports Action 11:45 a.m. (G. Breese) • ARM Framework Harvest Output for 2014 • Shorebird and Horseshoe Crab Survey Reports Summary • Delaware Bay Egg Survey Review Report 7. Other business/Adjourn 12:15 p.m. The meeting will be held at The King and Prince Beach & Golf Resort, 201 Arnold Street, St. Simons Island, GA; 800.342-0212 Healthy, self-sustaining populations for all Atlantic coast fish species or successful restoration well in progress by the year 2015 MEETING OVERVIEW Horseshoe Crab Management Board Meeting Thursday, October 31, 2013 10:15 a.m. – 12:15 p.m. St. Simon’s Island, GA Horseshoe Crab Law Enforcement Committee Chair: David Simpson (CT) Technical Committee Representative: Assumed Chairmanship: 2/12 Chair: Penny Howell (CT) Rutherford Horseshoe Crab Vice Chair: Previous Board Meeting: Advisory Panel Jim Gilmore (NY) May 22, 2013 Chair: Dr. -

Centerboard Classes NAPY D-PN Wind HC

Centerboard Classes NAPY D-PN Wind HC For Handicap Range Code 0-1 2-3 4 5-9 14 (Int.) 14 85.3 86.9 85.4 84.2 84.1 29er 29 84.5 (85.8) 84.7 83.9 (78.9) 405 (Int.) 405 89.9 (89.2) 420 (Int. or Club) 420 97.6 103.4 100.0 95.0 90.8 470 (Int.) 470 86.3 91.4 88.4 85.0 82.1 49er (Int.) 49 68.2 69.6 505 (Int.) 505 79.8 82.1 80.9 79.6 78.0 A Scow A-SC 61.3 [63.2] 62.0 [56.0] Akroyd AKR 99.3 (97.7) 99.4 [102.8] Albacore (15') ALBA 90.3 94.5 92.5 88.7 85.8 Alpha ALPH 110.4 (105.5) 110.3 110.3 Alpha One ALPHO 89.5 90.3 90.0 [90.5] Alpha Pro ALPRO (97.3) (98.3) American 14.6 AM-146 96.1 96.5 American 16 AM-16 103.6 (110.2) 105.0 American 18 AM-18 [102.0] Apollo C/B (15'9") APOL 92.4 96.6 94.4 (90.0) (89.1) Aqua Finn AQFN 106.3 106.4 Arrow 15 ARO15 (96.7) (96.4) B14 B14 (81.0) (83.9) Bandit (Canadian) BNDT 98.2 (100.2) Bandit 15 BND15 97.9 100.7 98.8 96.7 [96.7] Bandit 17 BND17 (97.0) [101.6] (99.5) Banshee BNSH 93.7 95.9 94.5 92.5 [90.6] Barnegat 17 BG-17 100.3 100.9 Barnegat Bay Sneakbox B16F 110.6 110.5 [107.4] Barracuda BAR (102.0) (100.0) Beetle Cat (12'4", Cat Rig) BEE-C 120.6 (121.7) 119.5 118.8 Blue Jay BJ 108.6 110.1 109.5 107.2 (106.7) Bombardier 4.8 BOM4.8 94.9 [97.1] 96.1 Bonito BNTO 122.3 (128.5) (122.5) Boss w/spi BOS 74.5 75.1 Buccaneer 18' spi (SWN18) BCN 86.9 89.2 87.0 86.3 85.4 Butterfly BUT 108.3 110.1 109.4 106.9 106.7 Buzz BUZ 80.5 81.4 Byte BYTE 97.4 97.7 97.4 96.3 [95.3] Byte CII BYTE2 (91.4) [91.7] [91.6] [90.4] [89.6] C Scow C-SC 79.1 81.4 80.1 78.1 77.6 Canoe (Int.) I-CAN 79.1 [81.6] 79.4 (79.0) Canoe 4 Mtr 4-CAN 121.0 121.6 -

11 04 08 Sect 2 (Pdf)

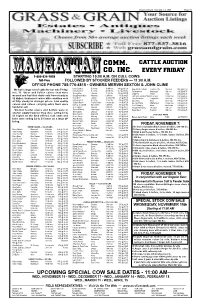

Grass & Grain, November 4, 2008 Page 17 COMM. CATTLE AUCTION MANHATTAN CO. INC. EVERY FRIDAY 1-800-834-1029 STARTING 10:00 A.M. ON CULL COWS Toll-Free FOLLOWED BY STOCKER FEEDERS — 11:00 A.M. B OFFICE PHONE 785-776-4815 • OWNERS MERVIN SEXTON & JOHN CLINE We had a large run of cattle for our sale Friday, Larry Howbert Berryton 10 blk hfrs 348 @ 101.00 Sam Jahnke & Sons Junction City 1 hol cow 1465 @ 41.50 Larry Howbert Berryton 43 blk hfrs 477 @ 100.85 oct. 31. Steer and heifer calves that were Ted Anderson Manhattan 1 blk cow 1190 @ 40.75 Gene Owen Linwood 11 blk hfrs 358 @ 100.50 Craig Fox Holton 1 cow 1295 @ 40.25 weaned and had their shots sold from steady to Doug Brackenbury Wamego 6 blk hfrs 446 @ 98.25 James W. & Mark PattonSt. George 1 cross cow 1320 @ 40.25 $2 higher. Unweaned calves with condition sold Kelly Miller Topeka 12 cross hfrs 476 @ 98.00 Jerry Stockman Tonganoxie 1 bwf cow 1210 @ 39.75 at fully steady to stronger prices. Low quality Larry Howbert Berryton 11 blk hfrs 414 @ 97.50 Larry King Hoyt 1 herf cow 1190 @ 38.75 Tailgate Ranch Prairie Village 6 cross hfrs 448 @ 97.00 calves and calves carrying extra flesh were Goeckel Farms Washington 1 cross cow 1140 @ 38.25 Larry & Jo Cordell Havensville 6 blk hfrs 511 @ 96.50 Geo S. Quigley Blaine 5 bwf cows 1298 @ 37.75 harder to sell. Gene Owen Linwood 9 blk hfrs 413 @ 95.75 Woody Henneberg Wheaton 1 blk cow 1265 @ 36.75 Stocker feeder steers and heifers were in Goeckel Farms Washington 8 char hfrs 441 @ 94.75 Susan Koch Frankfort 1 blk cow 1430 @ 36.25 shorter supply however they were selling $2 to Gene Owen Linwood 11 blk hfrs 467 @ 94.50 Bruce Nutsch Muscotah 25 blk hfrs 541 @ 93.75 $3 higher on the kind offered. -

CHANGE of WATCH Awards & Banquet • January 19 • RSVP Now

Lake TownsendTELL Yacht Club • PO Box 4002 • Greensboro TALES NC 27404-4002 • www.laketownsendyachtclub.com December 2012 CHANGE OF WATCH Awards & Banquet • January 19 • RSVP now Issue 11 • December 2012 www.laketownsendyachtclub.com Call People. Go Sailing **** REACH OUT AND CALL SOMEONE **** In an effort to involve more sailors in the Club’s Sailing Events and Racing Programs, this “Available to Crew” list is published in each newsletter. If you have a boat and would like to participate in the Summer or Frostbite Race Series, call one of these folks for your crew. Alternatively, if you need a cruising partner on your boat or would like to team with someone on one of the city sailboats for a day sail or a race, contact someone on this list. If you are interested in crewing and would like to add your name to the list, please let Joleen know. Joleen has the best intentions of calling each new member if she doesn’t hear from them to encourage them to sign up on the Crew List. (See the Help Lines box located in this newsletter). Available To Crew Name Phone E-mail Jeanne Allamby [email protected] Bill Byrd 336-635-1926 Lacy Joyce 336-413-7929 [email protected] John Kuzmier 336-282-0411/336-580-5766 [email protected] Jonathan Kreider 336-829-6196 [email protected] Chris Maginnis 336-793-5313 [email protected] Dawn-Michelle Oliver [email protected] Jon Mitchell [email protected] Remik Pearson [email protected] George Shen 336-451-2646 [email protected] Martin Sinozich 336-455-9445 [email protected] Keith Smoot 336 996-6734 [email protected] Robert Riley [email protected] Bill Young 336-292-3102/336-707-0295 [email protected] Also, check the participation scratch sheet on the web Have ideas, articles,photos or contributions for inclusion in the newsletter? Send them to [email protected].