XTX Specification Rev

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ET820 IP510 Baseboard

ETX ET820 Intel® Atom™ N270 ETX CPU Module w/ Baseboard Intel® 945GSE Chipset CPU IP510 Winbond W83627EHG Multi I/O DDR2 SO-DIMM Socket Intel® 945GSE Chipset Audio SATA II PCI to ISA ICH7M 10/100 LAN ICH7M SATA 8 42 2 11 USB COM SATAII Gbe10/100 LAN Features Mini ITX Nano ETX Express Baseboard ● Onboard Intel® Atom™ Processor N270, 1.6GHz, 533MHz FSB ● 1x DDR2 SO-DIMM, Max. 2GB Features ● Supports CRT and LVDS (18/24-bit dual channel) ● Winbond W83627EHG ● Integrated ICH7M 10/100BaseT LAN ● Watchdog timer, 4-in / 4-out digital I/O ● Watchdog timer, PCI to ISA ● 2x SATA , 2x IDE, 4x USB 2.0, 2x COM ● 2x Realtek 8111DL GbE LAN ● Edge connectors for PS/2, VGA, COM1, dual RJ45, 4x USB, audio connector (Line-out, Line-in & Mic.) Specifications ● 1x Mini-PCIe (x1), 1x PCI slots CPU Intel® Atom™ Processor N270, 1.6GHz ● Board connectors for 1x SATA, 1x LVDS, 2x USB, 1x LPT, System Memory 1x DDR2 SO-DIMM, Max. 2GB 3x COM and Nano ETX Express connector ® System Chipset Intel 945GSE + ICH7M, 533MHz FSB ● ATX power connector BIOS Award ● 170mm x 170mm Watchdog Timer 256 levels SSD DOM or CF socket on baseboard Ordering Information H/W Monitor Yes 4x ETX connectors for PCI bus, USB, audio, VGA/CRT, LVDS, LAN, IP510: Mini ITX Nano ETX Express baseboard Expansion Slot COM ports, LPT, IDE, PS/2 keyboard/mouse and ISA bus Intel® 945GSE integrated Graphics Media Accelerator 950 (GMA Dimensions Drawing VGA Controller 950), supports CRT/LVDS VGA Memory Shared memory - Max. -

The Worldwide Merchant Embedded Computing Market 2018 Edition

THE WORLDWIDE MERCHANT EMBEDDED COMPUTING MARKET 2018 EDITION A Comprehensive Report on the Latest Embedded Computing Technologies Plus Forecasts of Key Markets Report Highlights Technical Trends PCI C ompactPCI AdvancedTCA PC/104 AdvancedMC MicroTCA COM Express PMC VMEbus OCP Market Trends Total Available Market Competitive Strategies Corporate Relations Industry Analysis and Forecast, 2015-2022 MEC Market Total A vailable MEC Market By Segment (Communications, Industrial, Medical, Aerospace/Military, Other Applications) Company Profiles (89) New Venture Research Corp. A Technology Market Research Company 337 Clay St., Suite 101 [email protected] Nevada City, CA 95959 www.newventureresearch.com Tel: (530) 265-2004 Fax: (530) 265-1998 The Worldwide Merchant Embedded Computing Market - 2018 Edition Synopsis The Worldwide Merchant Embedded The Industrial market segment also holds strong Computing Market - 2018 Edition report potential for the process control industries (oil & gas, analyzes the performance of the standards-based mining, agriculture, paper/pulp and textiles) as the and non-standards-based industry from 2015 - Industrial Internet of Things begins to impact 2022. Although there are several hundred manufacturing and engage Big Data solutions for companies in the standards-based MEC market, increased productivity and output. Related industries most are fairly small in revenue and highly like robotics will require high performance designs specialized, focusing on specific application that utilize advanced artificial intelligence and virtual segments with unique product requirements. reality solutions. Clean energy is also examined for However, the report also examines the world’s optimizing efficiency in solar, wind and tidal technical leading contract manufacturers that participate in solutions. the non-standards-based product assemblies in the same market segments. -

ETX-DC® Document Revision: 1.18

ETX-DC® Document Revision: 1.18 If it’s embedded, it’s Kontron » Table of Contents « 1 User Information ............................................................................ 1 1.1 About This Document ................................................................................................................................. 1 1.2 Copyright Notice ....................................................................................................................................... 1 1.3 Trademarks .............................................................................................................................................. 1 1.4 Standards ................................................................................................................................................ 1 1.5 Warranty .................................................................................................................................................. 2 1.6 Technical Support ...................................................................................................................................... 2 2 Introduction ................................................................................. 3 2.1 ETX®-DC .................................................................................................................................................. 3 2.2 ETX® Documentation ................................................................................................................................. 3 2.3 ETX® -

COM Express® Basic, Compact, Mini • Qseven® • SMARC™

• • • • Computer Highlights Product ETX® SMARC™ Qseven COM Express® - ® Qseven® on (70 x 70 mm) - Module Basic SMARC™ (84 x 55 mm) , Compact COM Express® mini (84 x 55 mm) , Mini your specialist for embedded solutions COM Express® Compact (95 x 95 mm) 13.10.2017 COM Express® Basic (125 x 95 mm) Embedded Boards Industrial Mainboards Embedded Systems Accessories & IoT 2,5“ Pico-ITX™ Mini-ITX™ Embedded Box PCs Gateways 3,5“ Single Board Computer Micro-ATX Embedded Panel PCs Switches PC/104 Flex-ATX Embedded Server Router Slot SBC ATX Embedded Desktop PCs Memory, CPUs Computer-on-Module Digital Signage Player Cables Industrial Monitors Power Supplies Available Features & Options: Designed for Industrial Applications Long-term Availability Extended Temperature -40°C…+85°C Custom Design Design-in Support Fixed Bill of Material Kits (Board with OS, Display & Cables) EOL / PCN Handling your specialist for embedded solutions Systems - Custom - Standard Kit Solutions - Embedded Board - Operating System - Accessories e.g. Cable/Memory Distribution - Embedded Boards - Displays - Power Supplies your specialist for embedded solutions COM Express® Basic Type 6 & Type 7 COM Express® Basic (125 x 95 mm) your specialist for embedded solutions COM Express® Basic (95 x 125 mm) Intel® Core™ i CPU (Kaby Lake & Skylake) Product SOM-5898 COMe-bKL6 ET970 SOM-5897 COMe-bSL6 Vendor ADVANTECH Kontron iBASE ADVANTECH Kontron Type / Pin-out Type 6 R2.1 Type 6 Type 6 Type 6 Type 6 Intel® Xeon®, Core® i, Intel® Core® i, Xeon, Intel® Core™ i , Xeon (7th Intel® Core™ -

Embedded Computing Highlights About Congatec 02|03

Product Guide Spring 2014 EMBEDDED COMPUTING HIGHLIGHTS About congatec 02|03 congatec AG is the preferred global vendor for innovative embedded solutionsto enable competitive advantages for our customers. Letter from the CEO Since the company’s inception in December Moreover, we bolstered our sales presence in adopting in order to not only offer benefits for 2004, congatec AG has established itself as a Australia and New Zealand through opening customers, but also to further tap target markets. globally recognized expert and reliable partner a new branch in Queensland. The Australian for embedded computer-on-modules solutions, market offers great potential, especially in the This would all be impossible without our coupled with excellent service and support. We segments of entertainment (gaming), agricultural employees’ commitment. I would like to take have secured second ranking worldwide in our technology, transportation management and this opportunity to again express my thanks to all market segment within the space of just eight medical technology, where congatec products congatec employees. In the passion with which years after our founding thanks to our clear can be deployed optimally. they pursue their daily activities, and through focus. customer-orientation, creativity and team Following the opening of the branches in Japan spirit, they have already brought the company congatec has already ranked among the Deloitte Australia, congatec is now represented with six to a leading position, and, together with the On our way to market leadership Technology Fast 50 for the second consecutive branches on four continents – Asia (Taiwan and company’s management, continue to stand for year1. This award distinguishes Germany’s Japan), Australia, Europe (Germany and the a sustainable and partnership-based corporate congatec AG, headquartered in Deggendorf, highest-growth technology companies. -

ETX Driving Embedded

An ACCES I/O Products Whitepaper ETX Driving Embedded I/O ACCES I/O Products, Inc., 10623 Roselle Street, San Diego, CA 92121 (858) 550-9559 • Fax (858) 550-7322 • [email protected] • www.accesio.com One of the fastest-growing concepts in the embedded world is the “computer-on-module” or COM.The COM approach takes the traditional concept of a computer motherboard with plug- in I/O modules and turns it around so that the motherboard, now called a baseboard, con- tains all the I/O and the CPU with its core support chips and memory plug in as a module. The result of this reversal is an approach that blends the advantages of custom design with those of standard products. Products based on the COM approach maintain long-term viabil- ity while retaining access to the latest in computer technology. One of the principal COM implementations available in the market is the Embedded Technology eXtended (ETX) specification, first developed by Kontron in early 2000. The ETX specification defines a module that is approximate- ly 100-mm square (see Figure 1) and contains the core of a personal computer (PC), including CPU, chipset, mem- aper ory, and core I/O capability. The core I/O includes Ethernet, graphics, USB, keyboard, mouse, and serial interfaces along with a PCI/ISA bus for connection to additional peripherals. Four surface-mount connectors route the mod- ule’s I/O to the baseboard, which can be designed to meet an application’s specific needs. P The original ETX specification was quickly adopted in the embedded industry and is now monitored by the ETX Industrial Group (ETXIG), which is dedicated to keeping the specification in line with advancing technology and market needs. -

Line Up-A Copy

Industrial Cloud Services Embedded Core Platforms Intelligent Self-Management Agent for Embedded Platforms One-Click Installation for Industrial Clouds Full Spectrum of Embedded Boards, A built-in chip with a standardized API provides a perfect solution and integrates several unique platform consolidating Featuring auto-synchronization and an intuitive interface, CloudBuilder functions to improve consistency, lighten the development effort and speed-up product time-to-market. provides resources and tools for developers to build their own cloud-based Modules and Software Services services in just 3 steps to effectively keep software current and up-to-date. Self Management • Dynamic Control Smart Fan • Multi-stage CPU Throttling • Smart Power Saving Mode Computer On Modules Embedded Single Board Computers Auto Protection MI/O Extension SBCs • Multi-level Watchdog • Real-time Detection & Response Industrial Motherboards Slot Single Board Computers Secure Storage Industrial Peripherals & Modules • Encrypted Data Space • EEPROM User Storage Regional Service & Customization Centers China Taiwan Netherlands Poland USA/ Canada Kunshan Taipei Eindhoven Warsaw Milpitas, CA Smart Access to Embedded Devices 86-512-5777-5666 886-2-2692-6076 31-40-267-7000 48-22-33-23-730 1-408-519-3800 SUSIAccess is an application for System Integrators that centralizes monitoring and management of embedded devices. By providing a ready-to-use remote access solution, system integrators can focus more on their own applications, and let Worldwide Offices SUSIAccess configure -

Kontron Design Guide ®

® Kontron Design Guide ® ETX® Document Revision 2.4 This page intentionally left blank Table of Contents Table of Contents 1 User Information ........................................................................................................ 6 1.1 Objective ......................................................................................................... 6 1.2 Target Audience ................................................................................................ 6 1.3 Assumptions .................................................................................................... 6 1.4 Scope.............................................................................................................. 6 1.5 About This Document ......................................................................................... 6 1.6 Copyright Notice ............................................................................................... 7 1.7 Trademarks ...................................................................................................... 7 1.8 Standards ........................................................................................................ 7 1.9 Warranty ......................................................................................................... 7 1.10 Technical Support .............................................................................................. 8 2 Introduction ............................................................................................................. -

Ampro XTX 830 Core™ Duo Computer-On-Module

Computer-On-Module Products RoHS Ampro XTX 830 2002/95/EC Core™ Duo Computer-On-Module Blazing Performance, Power Management Choose Ampro XTX 830 for… Specifications Modular, ultra high performance applications that PROCESSORS NETWORK INTERfacE require notebook-style power management. • Choice of • Ethernet – Intel 82562 (10/100BaseT) ™ – Core Duo T2500 2.0GHz VIDEO INTERfacE Description – Core™ Solo TBD • Controller – Integrated Intel GMA 950 Ampro XTX 830 is a small ultra high- • Cache – 2MB Level 2 – AGP 3D engine performance, Dual Core processor module with • Chipset – Intel 945GM/ICH7M – Supports resolutions to 2048x1536 advanced networking and high-performance • FSB – 533MHz or 667MHz – Up to 224MB DVMT Frame Buffer graphics in a modular format that plugs into your • System Controllers – PC-compatible DMA and • Multiple Display support existing ETX baseboard with minimal design interrupt controllers and timers – LVDS, TV-out CRT change. • Watchdog Timer SOFTWARE & DEVELOPMENT TOOLS ® MEMORY • OS Support – Windows CE 5.0, XP, XPe • DRAM – Up to 1GB DDR2 400/533/667 (See Web site for details) • Up to 1GB DDR2 Memory SODIMM • BIOS – AMI with ACPI 2.0 including S3 BUS INTERfacE MECHANICAL • New XTX standard • PCI Express™ 4 x1, PCI and LPC • Size – 95x114mm (3.7x4.5"); XTX form factor • Power Requirements • PCI Express, SATA I/O • EIDE –Single PCI-bus Enhanced Ultra DMA (w/512MB RAM, 100% Loaded) – 2.0GHz TBD @ 5V • ACPI 2.0 with S3 support 66/100 Synchronous IDE Interface supports up to two hard drives • Temperature (100 CFM system air flow) • Latest chipset, without a complete • SATA – 2 ports – Standard: 0° to +60°C baseboard re-design • Serial – 2 ports, TTL, transceivers on baseboard – Storage: –20° to +75°C • Parallel – EPP/ECP bidirectional port • Floppy – Supports 1 or 2 drives, shared with parallel • USB – 6 USB 2.0 ports For more information, pricing, and • Keyboard/Mouse – PS/2 interface details on volume discounts, please • Audio – AC97/HD speaker, mic, headphone call us at 1. -

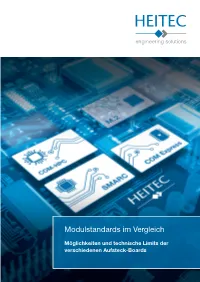

FA143 Modulstandards

Modulstandards im Vergleich Möglichkeiten und technische Limits der verschiedenen Aufsteck-Boards 1 Seit knapp 2 Jahrzehnten sind Aufsteckmodule verfügbar, die über standardisierte Schnittstellen an ein Doch was bedeuten diese Abkürzungen, Base-Board kontaktiert werden können. Die eindeu- welche Schnittstellen verbergen sich tigen Vorteile bescheren diesen Modulen eine immer dahinter und wo haben diese Konzepte stärker wachsende Nachfrage: Geringere Entwick- Ihre Vorteile im Vergleich zu anderen? lungszeit und -kosten, Verfügbarkeit, Skalierbarkeit von Performance und Preis, die Austauschbarkeit zwischen unterschiedlichen Anbietern und die Reduzierung von Risiken durch das Verwenden von zertifizierten Modulen Nachfolgend werden die geläufigen Abkürzungen rund sind Gründe, sich für Plug-On Boards zu entscheiden. um das Thema Plug-On Modul-Lösungen und Begriffe inkl. deren Schnittstellen und deren Möglichkeiten Die Anforderungen hinsichtlich Größe, Preis, Verfüg- näher erklärt. barkeit und die rasch voranschreitenden Chip-Tech- nologien stellen die Anbieter von Systemlösungen vor Package on a Package (PoP) Herausforderungen, die jedoch durch die Verwendung von Aufsteck-Modulen sehr gut managebar sind. Sind Ein „Package on a Package“ stapelt Einzel-Packages während der Designphase Anforderungen an Perfor- in Form von kleinen bestückten Platinen vertikal über- mance, Schnittstellen, Abmessungen, aber auch z.B. einander, welche durch Ball-Grid-Arrays miteinander Temperaturbereich und Störaussendung definiert, kann verbunden werden. Sozusagen -

Product Guide 2020 Congatec International Partnerships

Product Guide 2020 congatec International partnerships congatec Sales Partner Solution Partner We simplify the use of embedded technology. congatec A story of courage and passion. Pursuing this dream calls for a lot of courage and absolute conviction. It’s a dream that inspires us, drives us anew every day. It’s a dream that requires passionate supporters to push it forward. People who help others progress and improve themselves in the process. People who inspire and are inspired. This is the story of congatec. The story of people who carry this spirit within them. People who put their all into developing new ideas – while remaining flexible and creative. Who respond quickly and solve problems. Who are always learning and want to explore the unknown. Who always beat a new path, whenever possible. Who stand out – when it’s good to be an individual. And who do it all for the customer and their needs. Embedded in your success. Pure-Play Roadmap Solid World’s largest vendor focused on Most complete roadmap Stable finance. COMs, SBCs and customized of COM products. Strong growth, no debt and designs only. solid profit. Design-In Innovative Logistics Proven superior design-in support. Close partnerships to Intel, AMD Logistics and stability of supply. Review of customers designs for and NXP. Strategy for long lead time compliance, thermal and Active player in standardization components. Flexibility through mechanical design to reduce risk committees SGET and PICMG. last time buy process. Proven and shorten design cycles. quality for more than -

Specifications Ordering Information Features

Intel® Core™ 2 Duo/ Core™ Duo/ Celeron® M ETX ESM-945ETX Module with Intel® 945GME + ICH7-M Chipset Features n Supports Intel® Core™ 2 Duo/ Core™ Duo/ Celeron® M CPU ® n Intel 945GME/ ICH7-M Chipset Supports 65nm Intel® µFC-PGA 478 / n One 200-pin SODIMM Up to 2GB DDR2 SDRAM µFC-BGA 479 Core™ 2 Duo / Core™ Duo CPU n Dual View, Dual-channel LVDS 1 Embedded System n Realtek RTL8101L LAN Intel® 945GME Chipset 2 n 4 PCI, 1 ISA Bus Qseven Module n 2 SATA, 4 USB , 2 COM 3 2 SATA ETX/XTX COM Express 4 3.5” SBC ® ® Intel Dual Intel ICH7-M Chipset One 200-pin up to 2 GB 2 LVDS LAN 4 PCI 5 DDR2 SDRAM 945GME View EPIC ISA 2 SATA 4 USB 2 COM Bus 6 5.25” SBC Specifications 7 ATX System Audio • CPU Intel® Core™ 2 Duo/ Core™ Duo/ Celeron® M CPU Socket • Intel® ICH7-M 8 Chipset Micro Onboard Intel® Core™ 2 Duo L7400 1.5GHz CPU/ • AC97 Codec Realtek ALC203 ATX Onboard Intel® Celeron M ULV 423 1.06GHz CPU Note: T7400 Can't be Used Due to Power Issue • Audio Interface Line-in, Line-out & Mic-in 9 • BIOS Award 4Mbit Flash BIOS Mini ITX • System Chipset Intel® 945GME/ ICH7-M Ethernet • System Memory One 200-pin SODIMM Socket Supports Up to 2GB • LAN Realtek RTL8101L 10 DDR2 400/ 533/ 667 SDRAM Nano • Ethernet Interface 10/ 100 Base-Tx Fast Ethernet compatible ITX • Watchdog Timer Reset: 1sec. ~ 255min. and 1sec. or 1min./ step • Expansion 4 x PCI, 1 x ISA Bus 11 Mechanical & Environmental ACP • Power Requirement +5V I/O • Power Type AT/ ATX 12 • MIO 1 x EIDE (Ultra DMA 100), 2 x SATA, 1 x FDD/ LPT, Rack Mount • Operating Temperature 0 ~ 60°C (32 ~ 140°F)