Naval Postgraduate School Petite Amateur Navy Satellite

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ssc09-Xii-03

SSC09-XII-03 The Promise of Innovation from University Space Systems: Are We Meeting It? Michael Swartwout St. Louis University 3450 Lindell Boulevard St. Louis, Missouri 63103; (314) 977-8240 [email protected] ABSTRACT A popular notion among universities is that we are innovation-drivers in the staid, risk-adverse spacecraft industry – we are to professional small satellites what small satellites are to the “battlestars”. By contrast, professional industry takes a much different perspective on university-class spacecraft; these programs are good for attracting students to space and providing valuable pre-career training, but the actual flight missions are ancillary, even unimportant. Which opinion is correct? Both are correct. The vast majority of the 111 student-built spacecraft that have flown have made no innovative contributions. That is not to say that they have been without contribution. In addition to the inarguable benefits to education, many have served as radio Amateur communications, science experiments and even technological demonstrations. But “innovative”? Not so much. However, there have been two innovative contributors, whose contributions are large enough to settle the question: the University of Surrey begat SSTL, which helped create the COTS-based small satellite industry. Stanford and Cal Poly begat CubeSats, whose contributions are still being created today. This paper provides an update to our earlier submissions on the history of student-built spacecraft. Major trends identified in previous years will be re-examined with new data -- especially the bifurcation between larger-scale, larger-scope "flagship" programs and small-scale, reduced-mission "independents". In particular, we will demonstrate that the general history of student-built spacecraft has not been one of innovation, nor of development of new space systems -- with those few, extremely noteworthy, exceptions. -

Repeaters, Satellites, EME and Direction Finding 23

Repeaters, Satellites, EME and Direction Finding 23 Repeaters his section was written by Paul M. Danzer, N1II. In the late 1960s two events occurred that changed the way radio amateurs communicated. The T first was the explosive advance in solid state components — transistors and integrated circuits. A number of new “designed for communications” integrated circuits became available, as well as improved high-power transistors for RF power amplifiers. Vacuum tube-based equipment, expensive to maintain and subject to vibration damage, was becoming obsolete. At about the same time, in one of its periodic reviews of spectrum usage, the Federal Communications Commission (FCC) mandated that commercial users of the VHF spectrum reduce the deviation of truck, taxi, police, fire and all other commercial services from 15 kHz to 5 kHz. This meant that thousands of new narrowband FM radios were put into service and an equal number of wideband radios were no longer needed. As the new radios arrived at the front door of the commercial users, the old radios that weren’t modified went out the back door, and hams lined up to take advantage of the newly available “commer- cial surplus.” Not since the end of World War II had so many radios been made available to the ham community at very low or at least acceptable prices. With a little tweaking, the transmitters and receivers were modified for ham use, and the great repeater boom was on. WHAT IS A REPEATER? Trucking companies and police departments learned long ago that they could get much better use from their mobile radios by using an automated relay station called a repeater. -

PANSAT) Was Launched Aboard the STS-95 Discovery Shuttle

777 Dyer Rd., Rm. 125, Code (SP/Sd), Monterey, California 93943 (831) 656-2299; email: [email protected] Abstract. The Petite Amateur Navy Satellite (PANSAT) was launched aboard the STS-95 Discovery Shuttle. The hist flight noted mainly by John Glenn’s return to space also marks the Naval Postgraduate School’s first smal space. PANSAT, which is in a circular, low-Earth orbit (LEO), is the culmination of 50 officer studen theses over approximately a nine-year period. The satellite continues to support the educational mission will soon provide on-orbit capability of store-and-forward digital communications for the amateur radio using direct sequence, spread spectrum modulation. The spacecraft includes the communications payloa power subsystem, digital control subsystem, and structure. This paper describes the overall architecture of th bus, a discussion of the NPS command ground station, and some lessons learned. Introduction Mission Requirements and Object The Space Systems Academic Group at NPS provides Education direction and a focal point for Naval Postgraduate School (NPS) space research and the space curricula: Space The primary objective for PANSAT is to pro Systems Engineering and Space Systems Operations. The on educational opportunities for the officer Petite Amateur Navy Satellite (PANSAT) is the first NPS NPS. The first phase of the program prov satellite in space. Approximately 50 Master’s degree support to the engineering disciplines through theses were published on the satellite. Officer students development, integration, and test. A numb played a vital role in the successful development of the were also related to operations. Now that satellite and gained invaluable experience through their operating in space, the emphasis has shift part in the project. -

The Petite Amateur Navy Satellite (PANSAT) Hitchhiker Ejectable

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Calhoun, Institutional Archive of the Naval Postgraduate School Calhoun: The NPS Institutional Archive Faculty and Researcher Publications Faculty and Researcher Publications Collection 1998 The Petite Amateur Navy Satellite (PANSAT) Hitchhiker Ejectable Sakoda, Daniel Monterey, California: Naval Postgraduate School. http://hdl.handle.net/10945/37436 THE PETITE AMATEUR NAVY SATELLITE (PANSAT) HITCHHIKER EJECTABLE Daniel Sakoda Aerospace Engineer, Naval Postgraduate School ABSTRACT The Petite Amateur Navy Satellite (PANSAT) was successfully launched aboard the STS- 95 Discovery Shuttle as part of the third International Extreme Ultraviolet Hitchhiker (IEH-3), and placed into a circular, low-Earth orbit with 555 km (300 nmi.) altitude and 28.5° inclination. The culmination of approximately 50 graduate student theses, PANSAT provides the amateur radio community with digital, store-and-forward, direct sequence, spread spectrum communications, as well as providing officer students at NPS a space-based instructional laboratory. The spacecraft hardware was built and tested almost entirely at NPS to the component level. Rigorous analysis and testing was performed to ensure compatibility with Shuttle payload requirements. This paper describes the spacecraft design as relates to both compliance with Shuttle safety requirements and ensuring overall mission success. Specifically, PANSAT design requirements for structures, radio frequency emissions, and batteries will be discussed along with some lessons learned in the verification process. INTRODUCTION The Petite Amateur Navy Satellite (PANSAT) is the Naval Postgraduate School's (NPS) first satellite in space. The main objective is to provide a hands-on, educational tool for the officer students at NPS in the Space Systems Engineering and Space Systems Operations curricula. -

Some of the Women of Goddard Involved in the Space Shuttle

Space Shuttle Discovery, March 7, 2011, as photographed from the International Space Station. Space Shuttle: A Key to NASA’s Space Transportation System Following the spectacular successes of the Apollo program, NASA designed the Space Transportation System (STS), including the crew-tended Space Shuttle orbiter, to provide a reusable vehicle for launching heavy payloads, maintaining low Earth orbit, and returning to ground with a runway landing. The Shuttle made its first orbital flight in April 1981 and its last flight in July 2011. The manifests for Space Shuttle Endeavour, making its final landing at Kennedy Space Center, the 135 flights were very diverse, from deploying planetary spacecraft June 1, 2011. and servicing the Hubble Space Telescope to construction of the International Space Station in low Earth orbit. The Shuttle program is centered at NASA’s Johnson Space Center and Kennedy Space Center, but it has important NASA Goddard Space Flight Center contributions. Astronaut Mary Cleave conducting an experiment on Space Shuttle Atlantis in May 1989. A rare event with two Space Shuttle Orbiters (Atlantis and Endeavour) simultaneously being prepared for separate launches at Kennedy Space Center, September 20, 2008. Photo by Jack Pfaller Space Shuttle Atlantis, July 8, 2011, lifting off with its four-member crew on the Shuttle program’s final mission. International Space Station Freedom, a laboratory dedicated to humans living and working in Low Earth Orbit, March 7, 2011, as The edge of the Earth’s atmosphere on photographed from -

Monitoring Times 2000 INDEX

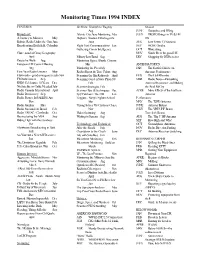

Monitoring Times 1994 INDEX FEATURES: Air Show: Triumph to Tragedy Season Aug JUNE Duopolies and DXing Broadcast: Atlantic City Aero Monitoring May JULY TROPO Brings in TV & FM A Journey to Morocco May Dayton's Aviation Extravaganza DX Bolivia: Radio Under the Gun June June AUG Low Power TV Stations Broadcasting Battlefield, Colombia Flight Test Communications Jan SEP WOW, Omaha Dec Gathering Comm Intelligence OCT Winterizing Chile: Land of Crazy Geography June NOV Notch filters for good DX April Military Low Band Sep DEC Shopping for DX Receiver Deutsche Welle Aug Monitoring Space Shuttle Comms European DX Council Meeting Mar ANTENNA TOPICS Aug Monitoring the Prez July JAN The Earth’s Effects on First Year Radio Listener May Radio Shows its True Colors Aug Antenna Performance Flavoradio - good emergency radio Nov Scanning the Big Railroads April FEB The Half-Rhombic FM SubCarriers Sep Scanning Garden State Pkwy,NJ MAR Radio Noise—Debunking KNLS Celebrates 10 Years Dec Feb AntennaResonance and Making No Satellite or Cable Needed July Scanner Strategies Feb the Real McCoy Radio Canada International April Scanner Tips & Techniques Dec APRIL More Effects of the Earth on Radio Democracy Sep Spy Catchers: The FBI Jan Antenna Radio France Int'l/ALLISS Ant Topgun - Navy's Fighter School Performance Nov Mar MAY The T2FD Antenna Radio Gambia May Tuning In to a US Customs Chase JUNE Antenna Baluns Radio Nacional do Brasil Feb Nov JULY The VHF/UHF Beam Radio UNTAC - Cambodia Oct Video Scanning Aug Traveler's Beam Restructuring the VOA Sep Waiting -

Amateur Satellite Beginners Session

Amateur Satellite Beginners Session Presented by Dave Johnson, G4DPZ AMSAT-UK / AMSAT-NA In association with Carlos Eavis, G0AKI RSGB Welcome We are going to cover: z OSCAR? z History z A bit of orbit theory z Satellite operation z Satellite modes z Ground station equipment z What's up! Oscar... z An OSCAR is an Orbiting Satellite Carrying Amateur Radio z Built for non-commercial purposes z Originally built by Project OSCAR members in garages in Silicon Valley z Now built by and/or funded by members of AMSAT and AMSAT affiliates z Originally a “bleep sat” but now carry sophisticated repeaters or transponders z Are encouraged to carry sensors and other scientific experiments A bit of History z OSCAR-I , which had a battery powered 140mw transmitter operating in the 2 meter band. z Transmit it’s message of “HI” for three weeks and re- entered the atmosphere on January 31, 1962 after making 312 orbits. z The greeting “HI” is used in almost all beacons, including AO-40’s telemetry beacon, built and launched by the Amateur Satellite service. A bit of History z Sputnik 1 was the world's first Earth- orbiting artificial satellite. Launched by the Soviet Union on October 4, 1957. How is a Satellite Designed FM v Linear Transponder Some important terms Threats to Satellites Orbital Comparison Satellite Orbit Tracks Inclined Orbit Molnya Satellite Coverage High Earth Orbit (HEO) Low Earth Orbit (LEO) CubeSats z Based on a 10cm cube but some can be a bit bigger z Operate in Amateur Satellite allocation z AX-25 protocol & others Student Satellites -

Satellites Frequency List Update

All Satellites Frequency List Update 30 Sept 2013, Latest Update by JE9PEL Satellite Number Uplink Downlink Beacon Mode Callsign Active ------------ ----- ----------- ----------- ------- ----------------- ------------ ------ AO-1 (Oscar-1) 00214 . 144.983 CW AO-2 (Oscar-2) 00305 . 144.983 CW AO-3 (Oscar-3) 01293 145.975-146.025 144.325-375 . SSB,CW AO-4 (Oscar-4) 01902 432.145-155 144.300-310 . SSB,CW AO-5 (Oscar-5) 04321 . 29.450 144.050 CW AO-6 (Phase-2A) 06236 145.900-999 29.450-550 . SSB,CW AO-7 (Phase-2B) 07530 145.850-950 29.400-500 29.502 A * AO-7 (Phase-2B) 07530 432.125-175 145.975-925 145.970 B,C * AO-7 (Phase-2B) 07530 . 2304.100 435.100 D(RTTY) AO-8 (Phase-2D) 10703 145.850-900 29.400-500 29.402 SSB,CW AO-8 (Phase-2D) 10703 145.900-999 435.200-100 435.095 SSB,CW UO-9 (UoSAT-1) 12888 . 145.825/435.025 2401.000 SSB,CW AO-10 (Phase-3B) 14129 435.030-180 145.975-825 145.810 SSB,CW UO-11 (UoSAT-2) 14781 . 145.826/435.025 2401.500 (V)FM,(S)PSK UOSAT-2 * MIR 16609 145.985 145.985 145.985 Packet R0MIR-1 RS-12 (Sputnik) 21089 21.210-250 29.410-450 29.408 SSB,CW RS-13 (Sputnik) 21089 21.260-300 145.860-900 145.862 SSB,CW AO-13 (Phase-3C) 19216 435.423-573 145.975-825 145.812 SSB,CW UO-14 (UoSAT-3) 20437 145.975 435.070 . -

UNIVERSIDADE CATÓLICA DE SANTOS Márcia Alvarenga Dos

UNIVERSIDADE CATÓLICA DE SANTOS Márcia Alvarenga dos Santos Regime Internacional Aplicável a Pequenos Satélites de Baixa Complexidade: Propostas para Salvaguardar Atores Espaciais e Mitigar Impactos Ambientais no Espaço Exterior Santos 2019 Márcia Alvarenga dos Santos Regime Internacional Aplicável a Pequenos Satélites de Baixa Complexidade: Propostas para Salvaguardar Atores Espaciais e Mitigar Impactos Ambientais no Espaço Exterior Tese do Programa de Pós Graduação da Universidade Católica de Santos defendida como requisito à obtenção do Grau de Doutor em Direito. Área de Concentração: Direito Ambiental Internacional. Orientador: Prof. Dr. Olavo de Oliveira Bittencourt Neto. Co-orientador: Prof. Dr. Marcelo Lopes de Oliveira e Souza. Santos 2019 [Dados Internacionais de Catalogação] Departamento de Bibliotecas da Universidade Católica de Santos ________________________________________________________________________________________ Santos, Márcia Alvarenga dos S237r Regime Internacional Aplicável a Pequenos Satélites de Baixa Complexidade: Propostas para Salvaguardar Atores Espaciais e Mitigar Impactos Ambientais no Espaço Exterior / Márcia Alvarenga dos Santos; orientadores Olavo de Oliveira Bittencourt Neto e Marcelo Lopes de Oliveira e Souza.-- 2019. 258 f.; 30 cm Tese (doutorado) - Universidade Católica de Santos, Programa de Pós-Graduação Stricto Sensu em Direito Ambiental Internacional, 2019 Inclui bibliografia 1. Direito ambiental internacional. 2. Direito espacial. 3. Satélites. I.Bittencourt Neto, Olavo de Oliveira. II.Souza, Marcelo Lopes de Oliveira e. III. Título. CDU 1997 -- 34(043.2) ________________________________________________________________________________________ Viviane Santos da Silva – CRB 8/6746 “There is freedom waiting for you, On the breezes of the sky, And you ask “What if I fall?” Oh but my darling, What if you fly?” - Erin Hanson Em homenagem ao Prof. Júnior Torres de Castro: um brasileiro, um visionário, um sonhador. -

January 5, 1998 KSC Contact: Bruce Buckingham KSC Release No

January 5, 1998 KSC Contact: Bruce Buckingham KSC Release No. 1-98 KENNETH PAYNE NAMED KSC LOGISTICS OPERATIONS DIRECTOR Kenneth Payne, a veteran leader in the field of acquisition and logistics management, is being named director of Logistics Operations at the Kennedy Space Center, effective Feb. 1, 1998 by Center Director Roy Bridges. "I am very pleased that Ken Payne is joining our KSC staff," said Bridges. "He is a man with world-class credentials in leading change in large, high technology acquisition and logistics organizations." Payne's responsibilities as Logistics Operations director will include management of the contract for Space Shuttle orbiter flight hardware spares, repairs, and all the associated planning and management of the supply vendor infrastructure. He also will oversee technical management of logistics functions of repair and spares for all launch processing ground systems and facilities for both Shuttle and payloads processing, as well as Center support. Other responsibilities include management of all Center logistics functions such as supply, transportation, equipment management, property disposal, and associated technical training. "I believe Ken has the right experience, energy and vision to lead our logistics organization into the 21st Century. We have opportunities to contribute more to NASA in this area. Ken, with the support of a great team at KSC, will make things happen," said Bridges. Payne, a member of the Senior Executive Service, currently serves as deputy director of Requirements, Headquarters Air Force Materiel Command, Wright-Patterson Air Force Base, Ohio. The directorate is the command focal point for program and product management policy, processes and resources. -

PANSAT) Project

Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 1995-12 An overview of the Petite Amateur Navy Satellite (PANSAT) project Severson, Fred J. Monterey, California. Naval Postgraduate School http://hdl.handle.net/10945/31379 NAVAL POSTGRADUATE SCHOOL Monterey, California THESIS AN OVERVIEW OF THE PETITE AMATEUR NAVY SATELLITE (PANSAT) PROJECT by Fred J. Severson December, 1995 Thesis Advisor: I. Michael Ross Co-Advisors: Daniel Sakoda Todd Morris Approved for public release; distribution is unlimited. THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY. Form Approved REPORT DOCUMENTATION PAGE OMB No. 0704-0188 Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washingon headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302. and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503. 1.AGENCY USE ONLY (Leave blank) 2.REPORT DATE 3.REPORT TYPE AND DATES COVERED December 1995 Master's Thesis 4.TITLE AND SUBTITLE AN OVERVIEW OF THE PETITE AMATEUR NAVY 5.FUNDING NUMBERS SATELLITE (PANSAT) PROJECT 6.AUTHOR(S) Severson, Fred J. 7.PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) 8.PERFORMING ORGANIZATION Naval Postgraduate School REPORT NUMBER Monterey CA 93943-5000 •».SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10.SPONSORING/MONITORING AGENCY REPORT NUMBER 11.SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. -

Politecnico Di Torino Esami Di Stato Per L’Abilitazione All’Esercizio Della Professione Di Ingegnere Industriale

POLITECNICO DI TORINO ESAMI DI STATO PER L’ABILITAZIONE ALL’ESERCIZIO DELLA PROFESSIONE DI INGEGNERE INDUSTRIALE II Sessione 2019 - Sezione A Settore Industriale Prova PRATICA del 20 dicembre 2019 Il Candidato svolga uno a scelta fra i seguenti temi proposti. Gli elaborati prodotti dovranno essere stilati in forma chiara, ordinata, sintetica e leggibile. La completezza, l’attinenza e la chiarezza espositiva costituiranno elementi di valutazione. Tema n. 1 La missione PRISMA (PRecursore IperSpettrale della Missione Applicativa) è una missione dell’Agenzia Spaziale Italiana (ASI) lanciata il 22 Marzo 2019 con il vettore VEGA. PRISMA è una missione sviluppata per fornire un contributo unico all’osservazione delle risorse naturali e fornire dati fondamentali per l’analisi dei processi ambientali. Per poter raggiungere gli obbiettivi di missione, il segmento spazio della missione è provvisto di strumenti elettro-ottici costituiti da un sensore iperspettrale e da una macchina fotografica a media risoluzione sensibile a tutti i colori (pancromatica). Si assumano i seguenti requisiti di missione ad alto livello: • Dimostrare nuove tecnologie in orbita utilizzando un satellite di piccole dimensioni; • Identificare e monitorare le risorse naturali e le caratteristiche dell’atmosfera (informazioni sullo stato delle colture, inquinamento, fiumi e laghi, stato delle zone costiere e del Mar Mediterraneo, composizione del terreno e ciclo del carbonio). Si considerino inoltre i seguenti requisiti: • Capacità di puntamento dello spacecraft di ±14.7º (off-nadir); • Accuratezza di puntamento sui 3 assi di 0.07°; • Peso massimo di 830 kg; • Quota massima: 615 km; • Orbita operativa: 97.85º. Si fornisce in allegato il dettaglio di: • Mission statement e obbiettivi di missione • Requisiti di alto livello di missione e di sistema • Requisiti dei payload Fig.