CA3140, CA3140A Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta

International Journal of Engineering Trends and Technology (IJETT) – Volume 7 Number 1- Jan 2014 Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta Assistant Professor, Electrical and Electronic Department, Uttar Pradesh Technical University, Lucknow Uttar Pradesh, India Abstract-- common problems like input common mode range, This paper describes a CMOS analogy voltage supper output swing, and linearity of the device. In the buffer designed to have extremely low static current resulting form to implement the desired analogue Consumption as well as high current drive capability. A device we apply the CMOS technology with low new technique is used to reduce the leakage power of voltage and low power techniques. Voltage supper class-AB CMOS buffer circuits without affecting dynamic power dissipation. The name of applied buffers are essential building blocks in analog and technique is TRANSISTOR GATING TECHNIQUE, mixed-signal circuits and processing systems, which gives the high speed buffer with the reduced low especially for applications where the weak signal power dissipation (1.105%), low leakage and reduced needs to be delivered to a large capacitive load area (3.08%) also. The proposed buffer is simulated at without being distorted To achieve higher density and 45nm CMOS technology and the circuit is operated at performance and lower power consumption, CMOS 3.3V supply[11]. Consumption is comparable to the devices have been scaled for more than 30 years. switching component. Reports indicate that 40% or Transistor delay times have decreased by more than even higher percentage of the total power consumption 30% per technology generation resulting in doubling is due to the leakage of transistors. -

High-Speed Rail-To-Rail Class-AB Buffer Amplifier with Compact

electronics Article High-Speed Rail-to-Rail Class-AB Buffer Amplifier with Compact, Adaptive Biasing for FPD Applications Chang-Ho An 1,* and Bai-Sun Kong 2,3,* 1 Department of Digital Electronics, Daelim University College, 29 Imgok-ro, Dongan-gu, Anyang-si 13916, Gyeonggi-do, Korea 2 Department of Electrical and Computer Engineering, Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon 16419, Gyeonggi-do, Korea 3 Department of Artificial Intelligence, Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon 16419, Gyeonggi-do, Korea * Correspondence: [email protected] (C.-H.A.); [email protected] (B.-S.K.) Received: 21 October 2020; Accepted: 25 November 2020; Published: 29 November 2020 Abstract: A high-slew-rate, low-power, CMOS, rail-to-rail buffer amplifier for large flat-panel-display (FPD) applications is proposed. The major circuit of the output buffer is a rail-to-rail, folded-cascode, class-AB amplifier which can control the tail current source using a compact, novel, adaptive biasing scheme. The proposed output buffer amplifier enhances the slew rate throughout the entire rail-to-rail input signal range. To obtain a high slew rate and low power consumption without increasing the static current, the tail current source of the adaptive biasing generates extra current during the transition time of the output buffer amplifier. A column driver IC incorporating the proposed buffer amplifier was fabricated in a 1.6-µm 18-V CMOS technology, whose evaluation results indicated that the static current was reduced by up to 39.2% when providing an identical settling time. The proposed amplifier also achieved up to 49.1% (90% falling) and 19.9 % (99.9% falling) improvements in terms of settling time for almost the same static current drawn and active area occupied. -

Common Gate Amplifier

© 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company COMMON GATE AMPLIFIER • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Common Gate Amplifier A common-gate amplifier is one of three basic single-stage field-effect transistor (FET) amplifier topologies, typically used as a current buffer or voltage amplifier. In the circuit the source terminal of the transistor serves as the input, the drain is the output and the gate is connected to ground, or common, hence its name. The analogous bipolar junction transistor circuit is the common-base amplifier. Input signal is applied to the source, output is taken from the drain. current gain is about unity, input resistance is low, output resistance is high a CG stage is a current buffer. It takes a current at the input that may have a relatively small Norton equivalent resistance and replicates it at the output port, which is a good current source due to the high output resistance. • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Circuit Topology • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company Waveforms Input Voltage Output Voltage • ACTIVATE solidThinking © 2017 solidThinking, Inc. Proprietary and Confidential. All rights reserved. An Altair Company The common-source and common-drain configurations have extremely high input resistances because the gate is the input terminal. In contrast, the common-gate configuration where the source is the input terminal has a low input resistance. Common gate FET configuration provides a low input impedance while offering a high output impedance. -

Digital Simulation and Recreation of a Vacuum Tube Guitar Amp by John

Digital Simulation and Recreation of a Vacuum Tube Guitar Amp by John Ragland A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science Auburn, Alabama May 2, 2020 Keywords: guitar, amplifier, nonlinear modeling, digital audio, vacuum-tube, distortion, signal processing, real-time simulation, guitar effects pedal Copyright 2020 by John Ragland Approved by Thaddeus Roppel, Associate Professor, Electrical and Computer Engineering Christopher Harris, Assistant Professor, Electrical and Computer Engineering Yin Sun, Assistant Professor, Electrical and Computer Engineering Abstract This thesis presents the process of designing, building, and testing a system that will be referred to herein as the Digital Guitar Amplifier. The Digital Guitar Amplifier is a real time digital audio signal processing unit that implements a signal processing algorithm that emulates the sound of a Fender Blues Jr. The Digital Guitar Amplifier fits within a reasonable footprint for a guitar effects pedal. The digital signal processor has CD level audio quality. The signal processing algorithm attempts to maintain the legacy of the vacuum tube within the math and processing of the algorithm by physically modelling the vacuum tube circuit. A mathematical comparison and human hearing survey is presented, which demonstrates that the sound of the Digital Guitar Amplifier compares favorably to the sound of a real Fender Blues Jr. amplifier. The algorithm that is developed can be extended to emulate any tube amplifier. 2 Acknowledgments I would like to thank my advisor Dr. Roppel for his guidance throughout my thesis research and writing process. I would like to thank Dr. -

United States Patent (19) 11 Patent Number: 6,034,316

US00603431.6A UnitedO States Patent (19) 11 Patent Number: 6,034,316 HOOver (45) Date of Patent: Mar. 7, 2000 54 CONTROLS FOR MUSICAL INSTRUMENT 5,378,850 1/1995 Tumura. SUSTANERS 5,449,858 9/1995 Menning et al.. 5,523,526 6/1996 Shattil. 76 Inventor: Alan Anderson Hoover, 3937 5,585,588 12/1996 Tumura. Cranbrook Dr., Indianapolis, Ind. 46240 OTHER PUBLICATIONS 21 Appl. No.: 09/258,251 NAMM Statistical Review of U.S. Music Products Industry, 1-1. 1998 National ASSociation of Music Merchants Publication, 22 Filed: Feb. 25, 1999 Carlsbad, CA. (51) Int. Cl." ..................................................... G10H 1/057 52 U.S. Cl. ......................................... 84/738; 84/DIG. 10 (List continued on next page.) 58 Field of Search ................................ 84/738, DIG. 10 Primary Examiner Stanley J. Witkowski 56) References Cited 57 ABSTRACT U.S. PATENT DOCUMENTS A Sustainer is provided for prolonging the vibrations of 472,019 3/1892 Omhart. Strings of a Stringed musical instrument. The instrument has 1,002,036 8/1911 Clement. at least one magnetic pickup means responsive to the 1,893,895 6/1933 Hammond. Vibrations of the Strings. The pickup produces an output 2,001,723 5/1935 Hammond. Signal in response to the vibrations of the instrument Strings. 2,600,870 6/1952 Hathaway et al.. At least one control potentiometer provides the capability to 2,672,781 3/1954 Miessner. control at least one parameter of the output Signal. The 3,185,755 5/1965 Williams et al.. Sustainer comprises a String driver transducer capable of E. 8.7 R et al. -

Opto Coupled Devices Module 5.0

Module www.learnabout-electronics.org 5 Opto Coupled Devices Module 5.0 What you’ll learn in Module 5.0 Opto Devices & Phototransistors After studying this section, you should be able to: Describe the operation of a phototransistor. Describe typical uses for photo couplers. Describe the advantages and disadvantages of different optocouplers: • Phototransistor types. • Photodiode types. Fig. 5.0.1 Transistor Optocouplers & Opto Sensors Optocouplers or opto isolators consisting of a combination of an infrared LED (also IRED or ILED) and an infra red sensitive device such as a photodiode or a phototransistor are widely used to pass information between two parts of a circuit that operate at very different voltage levels. Their main purpose is to provide electrical isolation between two parts of a circuit, increasing safety for users by reducing the risk of electric shocks, and preventing damage to equipment by potential short circuits between high-energy output and low-energy input circuits. They are also used in a number of sensor applications to sense the presence of physical objects. Transistor Optocouplers The devices shown in Fig. 5.0.1 use phototransistors as their sensing elements as they are many times more sensitive than photodiodes and can therefore produce higher values of current at their outputs. Example 1 in Fig. 5.0.1 illustrates the simplest form of opto coupling consisting of an infrared LED (with a clear plastic case) and an infrared phototransistor with a black plastic case that shields the phototransistor from light in the visible spectrum whilst allowing infrared light to pass through. Notice that the phototransistor has only two connections, collector and emitter, the input to the base being infrared light. -

2/24/2021 16:01 Common Collector CC Amplifier Design Vout Is Not

Common Collector CC Amplifier Design Vout is not inverted so the gains Av and Ai are positive. Designing procedure of common collector BJT amplifier has three areas. First, we have to set the Q-point, which is the DC operating point. Since, there is no specification regarding the Q-point in the design requirements; it leaves the designer enough freedom to choose the operating point as necessary for the application. However, remember that the specifications are in terms of input and output impedance, gain, frequency response characteristics and peak output voltages ultimately restricts the Q-point in a narrow window. It is difficult to derive this point without some intelligent guess and the following steps would work out for the given conditions. We will start to choose a Q-point to allow maximum output voltage swing For the Common Collector configuration, the circuit diagram shown in CC Figure 1. The small signal equivalent model in CC Figure 3. For this configuration, same steps are involved for the calculation of Rb1, Rb2 and Re with few minor changes. Note that Rc is absent in this case. Vpos Vpos Cbyp Vin Vin2 Rb1 Ri Cin Vb Vout NPN Riso Cout Rgen 50 Rb2 Chi Re Chi2 Rload Vneg Function Generator Rin Rin2 Vneg Rout Figure 1: BJT Common Collector CC configuration Page 1 of 9 Revised: 2/24/2021 16:01 CC Part 1: Measure the device parameters use CC Figure 2 Measure transistor parameters ICest , VCEsat, βDC, βDC,VE, VCE, βAC, βDC, ro, and rπ Step CC 1.1: Estimate the Ic collector current Q-point use IC estimate ≈ 2.6 * Iload peak this is not the solution to your design Q-point. -

AD636 Low Level, True RMS-To-DC Converter

Low Level, True RMS-to-DC Converter Data Sheet AD636 FEATURES FUNCTIONAL BLOCK DIAGRAM True rms-to-dc conversion V ABSOLUTE 200 mV full scale IN VALUE Laser-trimmed to high accuracy 0.5% maximum error (AD636K) SQUARER dB 1.0% maximum error (AD636J) COM DIVIDER Wide response capability CAV +VS Computes rms of ac and dc signals +VS 1 MHz, −3 dB bandwidth: V rms > 100 mV CURRENT Signal crest factor of 6 for 0.5% error MIRROR dB output with 50 dB range 10kΩ Low power: 800 μA quiescent current RL +VS Single or dual supply operation IOUT Monolithic integrated circuit BUFFER IN BUF Low cost 10kΩ BUFFER OUT AD636 40kΩ GENERAL DESCRIPTION –VS The AD636 is a low power monolithic IC that performs true –V S 00787-001 rms-to-dc conversion on low level signals. It offers performance Figure 1. that is comparable or superior to that of hybrid and modular converters costing much more. The AD636 is specified for a The AD636 is available in two accuracy grades. The total error of the signal range of 0 mV to 200 mV rms. Crest factors up to 6 can J-version is typically less than ±0.5 mV ± 1.0% of reading, while be accommodated with less than 0.5% additional error, allowing the total error of the AD636K is less than ±0.2 mV to ±0.5% of accurate measurement of complex input waveforms. reading. Both versions are temperature rated for operation between 0°C and 70°C and available in 14-lead SBDIP and 10-lead The low power supply current requirement of the AD636, TO-100 metal can. -

Operational-Amplifier Design Techniques

CHAPTER VIII OPERATIONAL-AMPLIFIER DESIGN TECHNIQUES 8.1 INTRODUCTION This chapter introduces some of the circuit configurations that are used for the design of high-performance operational amplifiers. This brief exposure cannot make operational-amplifier designers of us all, since con siderable experience coupled with a sprinkling of witchcraft seems essential to the design process. Fortunately, there is little need to become highly proficient in this area, since a continuously updated assortment of excellent designs is available commercially. However, the optimum performance can only be obtained from these circuits when their capabilities and limitations are appreciated. Furthermore, this is an area where good design practice has evolved to a remarkable degree, and the techniques used for opera tional-amplifier design are often valuable in other applications. The input stage of an operational amplifier usually consists of a bipolar- transistor differential amplifier that provides the differential input connec tion and the low drift essential in many applications. The design of this type of amplifier was investigated in detail in Chapter 7. The input stage is normally followed by one or more intermediate stages that combine with it to provide the voltage gain of the amplifier. Some type of buffer amplifier that isolates the final voltage-gain stage from loads and provides low output impedance completes the design. Configurations that are used for the inter mediate and output stages are described in this chapter. The interplay between a number of conflicting design considerations leads to a complete circuit that reflects a number of engineering compro mises. For example, one simple way to provide the high voltage gain char acteristic of operational amplifiers is to use several voltage-gain stages. -

Operational Amplifier Applications - Wikipedia, the Free Encyclopedia

Operational amplifier applications - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/Operational_amplifier_applications Operational amplifier applications From Wikipedia, the free encyclopedia This article illustrates some typical applications of solid-state integrated circuit operational amplifiers. A simplified schematic notation is used, and the reader is reminded that many details such as device selection and power supply connections are not shown. The resistors used in these configurations are typically in the kΩ range. <1 kΩ range resistors cause excessive current flow and possible damage to the device. >1 MΩ range resistors cause excessive thermal noise and make the circuit operation susceptible to significant errors due to bias currents. Note: It is important to realize that the equations shown below, pertaining to each type of circuit, assume that it is an ideal op amp. Those interested in construction of any of these circuits for practical use should consult a more detailed reference. See the External links and References sections. Contents 1 Linear circuit applications 1.1 Differential amplifier 1.1.1 Amplified difference 1.1.2 Difference amplifier 1.2 Inverting amplifier 1.3 Non-inverting amplifier 1.4 Voltage follower 1.5 Summing amplifier 1.6 Integrator 1.7 Differentiator 1.8 Comparator 1.9 Instrumentation amplifier 1.10 Schmitt trigger 1.11 Inductance gyrator 1.12 Zero level detector 1.13 Negative impedance converter (NIC) 2 Non-linear configurations 2.1 Precision rectifier 2.2 Peak detector 2.3 Logarithmic output 2.4 Exponential output 3 Other applications 4 See also 5 References 6 External links Linear circuit applications 1 of 9 2/2/07 10:50 AM Operational amplifier applications - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/Operational_amplifier_applications Differential amplifier The circuit shown is used for finding the difference of two voltages each multiplied by some constant (determined by the resistors). -

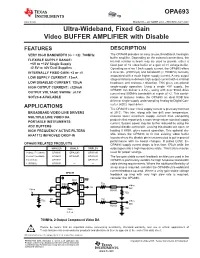

OPA693: Ultra-Wideband, Fixed Gain Video Buffer Amplifier with Disable

OP A6 93 OPA693 OP A6 93 www.ti.com SBOS285A – OCTOBER 2003 – REVISED JULY 2008 Ultra-Wideband, Fixed Gain Video BUFFER AMPLIFIER with Disable FEATURES DESCRIPTION ● VERY HIGH BANDWIDTH (G = +2): 700MHz The OPA693 provides an easy to use, broadband, fixed gain ● buffer amplifier. Depending on the external connections, the FLEXIBLE SUPPLY RANGE: internal resistor network may be used to provide either a +5V to +12V Single Supply fixed gain of +2 video buffer or a gain of ±1 voltage buffer. ±2.5V to ±6V Dual Supplies Operating on a low 13mA supply current, the OPA693 offers ● INTERNALLY FIXED GAIN: +2 or ±1 a slew rate (2500V/µs) and bandwidth (> 700MHz) normally associated with a much higher supply current. A new output ● LOW SUPPLY CURRENT: 13mA stage architecture delivers high output current with a minimal ● LOW DISABLED CURRENT: 120µA headroom and crossover distortion. This gives exceptional ● HIGH OUTPUT CURRENT: ±120mA single-supply operation. Using a single +5V supply, the ● ± OPA693 can deliver a 2.5VPP swing with over 90mA drive OUTPUT VOLTAGE SWING: 4.1V current and 500MHz bandwidth at a gain of +2. This combi- ● SOT23-6 AVAILABLE nation of features makes the OPA693 an ideal RGB line driver or single-supply undersampling Analog-to-Digital Con- APPLICATIONS verter (ADC) input driver. The OPA693’s low 13mA supply current is precisely trimmed ● BROADBAND VIDEO LINE DRIVERS at 25°C. This trim, along with low drift over temperature, ● MULTIPLE LINE VIDEO DA ensures lower maximum supply current than competing ● products that report only a room temperature nominal supply PORTABLE INSTRUMENTS current. -

Basic Electronics Lab Manual

Basic Electronics Lab Manual School of Physical Sciences National Institute of Science Education and Research Bhubaneswar 1 IDENTIFICATION OF CIRCUIT COMPONENTS Breadboards: In order to temporarily construct a circuit without damaging the components used to build it, we must have some sort of a platform that will both hold the components in place and provide the needed electrical connections. In the early days of electronics, most experimenters were amateur radio operators. They constructed their radio circuits on wooden breadboards. Although more sophisticated techniques and devices have been developed to make the assembly and testing of electronic circuits easier, the concept of the breadboard still remains in assembling components on a temporary platform. (a) (b) Fig. 1: (a) A typical Breadboard and (b) its connection details A real breadboard is shown in Fig. 1(a) and the connection details on its rear side are shown in Fig. 1(b). The five holes in each individual column on either side of the central groove are electrically connected to each other, but remain insulated from all other sets of holes. In addition to the main columns of holes, however, you'll note four sets or groups of holes along the top and bottom. Each of these consists of five separate sets of five holes each, for a total of 25 holes. These groups of 25 holes are all connected together on either side of the dotted line indicated on Fig.1(a) and needs an external connection if one wishes the entire row to be connected. This makes them ideal for distributing power to multiple ICs or other circuits.