Operational-Amplifier Design Techniques

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta

International Journal of Engineering Trends and Technology (IJETT) – Volume 7 Number 1- Jan 2014 Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta Assistant Professor, Electrical and Electronic Department, Uttar Pradesh Technical University, Lucknow Uttar Pradesh, India Abstract-- common problems like input common mode range, This paper describes a CMOS analogy voltage supper output swing, and linearity of the device. In the buffer designed to have extremely low static current resulting form to implement the desired analogue Consumption as well as high current drive capability. A device we apply the CMOS technology with low new technique is used to reduce the leakage power of voltage and low power techniques. Voltage supper class-AB CMOS buffer circuits without affecting dynamic power dissipation. The name of applied buffers are essential building blocks in analog and technique is TRANSISTOR GATING TECHNIQUE, mixed-signal circuits and processing systems, which gives the high speed buffer with the reduced low especially for applications where the weak signal power dissipation (1.105%), low leakage and reduced needs to be delivered to a large capacitive load area (3.08%) also. The proposed buffer is simulated at without being distorted To achieve higher density and 45nm CMOS technology and the circuit is operated at performance and lower power consumption, CMOS 3.3V supply[11]. Consumption is comparable to the devices have been scaled for more than 30 years. switching component. Reports indicate that 40% or Transistor delay times have decreased by more than even higher percentage of the total power consumption 30% per technology generation resulting in doubling is due to the leakage of transistors. -

1.5A, 24V, 17Mhz Power Operational Amplifier Datasheet (Rev. E)

OPA564 www.ti.com SBOS372E –OCTOBER 2008–REVISED JANUARY 2011 1.5A, 24V, 17MHz POWER OPERATIONAL AMPLIFIER Check for Samples: OPA564 1FEATURES 23• HIGH OUTPUT CURRENT: 1.5A DESCRIPTION • WIDE POWER-SUPPLY RANGE: The OPA564 is a low-cost, high-current operational – Single Supply: +7V to +24V amplifier that is ideal for driving up to 1.5A into reactive loads. The high slew rate provides 1.3MHz – Dual Supply: ±3.5V to ±12V full-power bandwidth and excellent linearity. These • LARGE OUTPUT SWING: 20VPP at 1.5A monolithic integrated circuits provide high reliability in • FULLY PROTECTED: demanding powerline communications and motor control applications. – THERMAL SHUTDOWN – ADJUSTABLE CURRENT LIMIT The OPA564 operates from a single supply of 7V to 24V, or dual power supplies of ±3.5V to ±12V. In • DIAGNOSTIC FLAGS: single-supply operation, the input common-mode – OVER-CURRENT range extends to the negative supply. At maximum – THERMAL SHUTDOWN output current, a wide output swing provides a 20VPP (I = 1.5A) capability with a nominal 24V supply. • OUTPUT ENABLE/SHUTDOWN CONTROL OUT • HIGH SPEED: The OPA564 is internally protected against over-temperature conditions and current overloads. It – GAIN-BANDWIDTH PRODUCT: 17MHz is designed to provide an accurate, user-selected – FULL-POWER BANDWIDTH AT 10VPP: current limit. Two flag outputs are provided; one 1.3MHz indicates current limit and the second shows a – SLEW RATE: 40V/ms thermal over-temperature condition. It also has an Enable/Shutdown pin that can be forced low to shut • DIODE FOR JUNCTION TEMPERATURE down the output, effectively disconnecting the load. MONITORING The OPA564 is housed in a thermally-enhanced, • HSOP-20 PowerPAD™ PACKAGE surface-mount PowerPAD™ package (HSOP-20) with (Bottom- and Top-Side Thermal Pad Versions) the choice of the thermal pad on either the top side or the bottom side of the package. -

Designing Linear Amplifiers Using the IL300 Optocoupler Application Note

Application Note 50 Vishay Semiconductors Designing Linear Amplifiers Using the IL300 Optocoupler INTRODUCTION linearizes the LED’s output flux and eliminates the LED’s This application note presents isolation amplifier circuit time and temperature. The galvanic isolation between the designs useful in industrial, instrumentation, medical, and input and the output is provided by a second PIN photodiode communication systems. It covers the IL300’s coupling (pins 5, 6) located on the output side of the coupler. The specifications, and circuit topologies for photovoltaic and output current, IP2, from this photodiode accurately tracks the photoconductive amplifier design. Specific designs include photocurrent generated by the servo photodiode. unipolar and bipolar responding amplifiers. Both single Figure 1 shows the package footprint and electrical ended and differential amplifier configurations are discussed. schematic of the IL300. The following sections discuss the Also included is a brief tutorial on the operation of key operating characteristics of the IL300. The IL300 photodetectors and their characteristics. performance characteristics are specified with the Galvanic isolation is desirable and often essential in many photodiodes operating in the photoconductive mode. measurement systems. Applications requiring galvanic isolation include industrial sensors, medical transducers, and IL300 mains powered switchmode power supplies. Operator safety 1 8 and signal quality are insured with isolated interconnections. These isolated interconnections commonly use isolation 2 K2 7 amplifiers. K1 Industrial sensors include thermocouples, strain gauges, and pressure transducers. They provide monitoring signals to a 3 6 process control system. Their low level DC and AC signal must be accurately measured in the presence of high 4 5 common-mode noise. -

NTE7144 Integrated Circuit BIMOS Operational Amplifier W/MOSFET Input, Bipolar Output

NTE7144 Integrated Circuit BIMOS Operational Amplifier w/MOSFET Input, Bipolar Output Description: The NTE7144 is an integrated circuit operational amplifier in an 8–Lead Mini–DIP type package that combines the advantages of high–voltage PMOS transistors with high–voltage bipolar transistors on a single monolithic chip. This device features gate–protected MOSFET (PMOS) transistors in the in- put circuit to provide very–high–input impedance, very–low–input current, and high–speed perfor- mance. The NTE7144 operates at supply voltages from 4V to 36V (either single or dual supply) and is internally phase–compensated to achieve stable operation in unity–gain follower operation. The use of PMOS field–effect transistors in the input stage results in common–mode input–voltage capability down to 0.5V below the negative–supply terminal, an important attribute for single–supply applications. The output stage uses bipolar transistors and includes built–in protection against dam- age from load–terminal short–circuiting to either supply–rail or to GND. Features: D MOSFET Input Stage: Very High Input Impedance Very Low Input Current Wide Common–Mode Input Voltage Range Output Swing Complements Input Common–Mode Range D Directly Replaces Industry Type 741 in Most Applications Applications: D Ground–Referenced Single–Supply Amplifiers in Automobile and Portable Instrumentation D Sample and Hold Amplifiers D Long–Duration Timers/Multivibrators (Microseconds – Minutes – Hours) D Photocurrent Instrumentation D Peak Detectors D Active Filters D Comparators D Interface in 5V TTL Systems and other Low–Supply Voltage Systems D All Standard Operational Amplifier Applications D Function Generators D Tone Controls D Power Supplies D Portable Instruments D Intrusion Alarm Systems Absolute Maximum Ratings: DC Supply Voltage (Between V+ and V– Terminals). -

Example of a MOSFET Operational Amplifier

Example of a MOSFET Operational Amplifier: This circuit is one I “designed” as an example for Engineering 1620. It is certainly not fully optimized and I am not sure it is free of errors. It is based on a 1.5 micron, P-well process and therefore uses an N-channel differential pair for its input. This is somewhat unusual because P-channel devices have lower intrinsic noise and are the device-type of choice for the input stage. I did this simply to avoid doing your SPICE assignment for you. The overall properties of the circuit are given in the table below. Amplifier Property Value A0 – DC Gain 86 DB (X20,000) fp – dominant pole position 400 Hz fGBW 8.0 MHz fU – unity gain frequency 5.6 MHz Output stage resistance at low frequency 277 K Zero position 10.7 MHz Slew Rate 710 6 V/sec Output stage quiescent current 65 a Opamp quiescent current 103 a Bias circuit quiescent current 104 a Total system quiescent current 210 a VDD 5.0 volts Total system power 1.1 mW MOSFET Operational Amplifier Gain and Phase 10 0 18 0 80 12 0 60 Gain 60 Phase 40 0 Gain (DB) 20 -60 Phase (deg.) 0 -120 -20 -180 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Frequency (Hz) Phase margin = 60 deg. Parameter Table for MOSFET Opamp Example element model vds vgs vth vov id gm ro m1 nssb 0.748 0.851 0.547 0.304 3.77E-05 2.90E-04 5.54E+05 m10 nssb 3.368 0.851 0.547 0.304 4.12E-05 3.11E-04 8.09E+05 m12 nssb 0.711 0.711 0.546 0.165 3.51E-05 5.01E-04 5.05E+05 m13 nssb 0.838 0.851 0.547 0.304 3.79E-05 2.91E-04 5.92E+05 m14 nssb 3.078 1.079 0.840 0.239 3.51E-05 -

AN55 Power Supply Bypassing for High-Voltage Operational Amplifiers

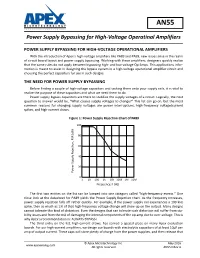

AN55 Power Supply Bypassing for High-Voltage Operatinal Amplifiers POWER SUPPLY BYPASSING FOR HIGH-VOLTAGE OPERATIONAL AMPLIFIERS With the introduction of Apex’s high-voltage amplifiers like PA89 and PA99, new issues arise in the realm of circuit board layout and power supply bypassing. Working with these amplifiers, designers quickly realize that the same rules do not apply between bypassing high- and low-voltage Op-Amps. This applications infor- mation is meant to assist in designing the bypass system in a high-voltage operational amplifier circuit and choosing the perfect capacitors for use in such designs. THE NEED FOR POWER SUPPLY BYPASSING Before finding a couple of high-voltage capacitors and tacking them onto your supply rails, it is vital to realize the purpose of these capacitors and what we need them to do. Power supply bypass capacitors are there to stabilize the supply voltages of a circuit. Logically, the next question to answer would be, “What causes supply voltages to change?” This list can go on, but the most common reasons for changing supply voltages are power interruptions, high-frequency voltage/current spikes, and high-current draws. Figure 1: Power Supply Rejection Chart of PA89 100 80 60 40 20 WŽǁĞƌ^ƵƉƉůLJZĞũĞĐƟŽŶ͕W^Z;ĚͿ 0 1 10100 1k 10k 100k1M 10M Frequency, F (Hz) The first two entries on the list can be lumped into one category called “high-frequency events.” One close look at the datasheet for PA89 yields the Power Supply Rejection chart. As the frequency increases, power supply rejection falls off rather quickly. For example, if the power supply rail experiences a 100 kHz spike, then as much as 1% of that high-frequency voltage change will show up on the output. -

A Differential Operational Amplifier Circuit Collection

Application Report SLOA064A – April 2003 A Differential Op-Amp Circuit Collection Bruce Carter High Performance Linear Products ABSTRACT All op-amps are differential input devices. Designers are accustomed to working with these inputs and connecting each to the proper potential. What happens when there are two outputs? How does a designer connect the second output? How are gain stages and filters developed? This application note answers these questions and gives a jumpstart to apprehensive designers. 1 INTRODUCTION The idea of fully-differential op-amps is not new. The first commercial op-amp, the K2-W, utilized two dual section tubes (4 active circuit elements) to implement an op-amp with differential inputs and outputs. It required a ±300 Vdc power supply, dissipating 4.5 W of power, had a corner frequency of 1 Hz, and a gain bandwidth product of 1 MHz(1). In an era of discrete tube or transistor op-amp modules, any potential advantage to be gained from fully-differential circuitry was masked by primitive op-amp module performance. Fully- differential output op-amps were abandoned in favor of single ended op-amps. Fully-differential op-amps were all but forgotten, even when IC technology was developed. The main reason appears to be the simplicity of using single ended op-amps. The number of passive components required to support a fully-differential circuit is approximately double that of a single-ended circuit. The thinking may have been “Why double the number of passive components when there is nothing to be gained?” Almost 50 years later, IC processing has matured to the point that fully-differential op-amps are possible that offer significant advantage over their single-ended cousins. -

9 Op-Amps and Transistors

Notes for course EE1.1 Circuit Analysis 2004-05 TOPIC 9 – OPERATIONAL AMPLIFIER AND TRANSISTOR CIRCUITS . Op-amp basic concepts and sub-circuits . Practical aspects of op-amps; feedback and stability . Nodal analysis of op-amp circuits . Transistor models . Frequency response of op-amp and transistor circuits 1 THE OPERATIONAL AMPLIFIER: BASIC CONCEPTS AND SUB-CIRCUITS 1.1 General The operational amplifier is a universal active element It is cheap and small and easier to use than transistors It usually takes the form of an integrated circuit containing about 50 – 100 transistors; the circuit is designed to approximate an ideal controlled source; for many situations, its characteristics can be considered as ideal It is common practice to shorten the term "operational amplifier" to op-amp The term operational arose because, before the era of digital computers, such amplifiers were used in analog computers to perform the operations of scalar multiplication, sign inversion, summation, integration and differentiation for the solution of differential equations Nowadays, they are considered to be general active elements for analogue circuit design and have many different applications 1.2 Op-amp Definition We may define the op-amp to be a grounded VCVS with a voltage gain (µ) that is infinite The circuit symbol for the op-amp is as follows: An equivalent circuit, in the form of a VCVS is as follows: The three terminal voltages v+, v–, and vo are all node voltages relative to ground When we analyze a circuit containing op-amps, we cannot use the -

High-Speed Rail-To-Rail Class-AB Buffer Amplifier with Compact

electronics Article High-Speed Rail-to-Rail Class-AB Buffer Amplifier with Compact, Adaptive Biasing for FPD Applications Chang-Ho An 1,* and Bai-Sun Kong 2,3,* 1 Department of Digital Electronics, Daelim University College, 29 Imgok-ro, Dongan-gu, Anyang-si 13916, Gyeonggi-do, Korea 2 Department of Electrical and Computer Engineering, Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon 16419, Gyeonggi-do, Korea 3 Department of Artificial Intelligence, Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon 16419, Gyeonggi-do, Korea * Correspondence: [email protected] (C.-H.A.); [email protected] (B.-S.K.) Received: 21 October 2020; Accepted: 25 November 2020; Published: 29 November 2020 Abstract: A high-slew-rate, low-power, CMOS, rail-to-rail buffer amplifier for large flat-panel-display (FPD) applications is proposed. The major circuit of the output buffer is a rail-to-rail, folded-cascode, class-AB amplifier which can control the tail current source using a compact, novel, adaptive biasing scheme. The proposed output buffer amplifier enhances the slew rate throughout the entire rail-to-rail input signal range. To obtain a high slew rate and low power consumption without increasing the static current, the tail current source of the adaptive biasing generates extra current during the transition time of the output buffer amplifier. A column driver IC incorporating the proposed buffer amplifier was fabricated in a 1.6-µm 18-V CMOS technology, whose evaluation results indicated that the static current was reduced by up to 39.2% when providing an identical settling time. The proposed amplifier also achieved up to 49.1% (90% falling) and 19.9 % (99.9% falling) improvements in terms of settling time for almost the same static current drawn and active area occupied. -

Fully-Differential Amplifiers

Application Report S Fully-Differential Amplifiers James Karki AAP Precision Analog ABSTRACT Differential signaling has been commonly used in audio, data transmission, and telephone systems for many years because of its inherent resistance to external noise sources. Today, differential signaling is becoming popular in high-speed data acquisition, where the ADC’s inputs are differential and a differential amplifier is needed to properly drive them. Two other advantages of differential signaling are reduced even-order harmonics and increased dynamic range. This report focuses on integrated, fully-differential amplifiers, their inherent advantages, and their proper use. It is presented in three parts: 1) Fully-differential amplifier architecture and the similarities and differences from standard operational amplifiers, their voltage definitions, and basic signal conditioning circuits; 2) Circuit analysis (including noise analysis), provides a deeper understanding of circuit operation, enabling the designer to go beyond the basics; 3) Various application circuits for interfacing to differential ADC inputs, antialias filtering, and driving transmission lines. Contents 1 Introduction . 3 2 What Is an Integrated, Fully-Differential Amplifier? . 3 3 Voltage Definitions . 5 4 Increased Noise Immunity . 5 5 Increased Output Voltage Swing . 6 6 Reduced Even-Order Harmonic Distortion . 6 7 Basic Circuits . 6 8 Circuit Analysis and Block Diagram . 8 9 Noise Analysis . 13 10 Application Circuits . 15 11 Terminating the Input Source . 15 12 Active Antialias Filtering . 20 13 VOCM and ADC Reference and Input Common-Mode Voltages . 23 14 Power Supply Bypass . 25 15 Layout Considerations . 25 16 Using Positive Feedback to Provide Active Termination . 25 17 Conclusion . 27 1 SLOA054E List of Figures 1 Integrated Fully-Differential Amplifier vs Standard Operational Amplifier. -

E Basic Circuit of an Operational Amplifier Is As Shown in Above Fig

www.getmyuni.com UNIT - 1 OPERATIONAL AMPLIFIER FUNDAMENTALS 1.1 Basic operational amplifier circuit- heT basic circuit of an operational amplifier is as shown in above fig. has a differential amplifier input stage and an emitter follower output. Supply voltages +Vcc and -Vcc are provided. Transistors Q1 and Q2 constitute a differential amplifier, which produces a voltage change as the collector of Q2 where a difference input voltage is applied to the bases of Q1 and Q2. Transistor Q2 operates as an emitter follower to provide low output impedance. Vo = Vcc –VRC –VBE3 = Vcc – IC2Rc – VBE Assume that Q1 and Q2 are matched transistors that are they have equal VBE levels and equalcurrent gains. With both transistor bases at ground level, the emitter currents are equal and both IE1 and IE2 flow through the common emitter resistor RE. The emitter current is given by:- www.getmyuni.com IE1 + IE2 = VRE/RE With Q1 and Q2 bases grounded, 0 – VBE – VRE + VEE = 0 VEE – VBE = VRE VRE = VEE – VBE IE1 + IE2 = – Vcc = 10 V, VEE = - 10 V, RE = 4.7 K, Rc = 6.8 K, VBE = 0.7, IE1 + IE2 = (10 – 0.7)/4.7 K + 2 mA IE1 = IE2 = 1mA Ic2 = IE2 = 1 mA Vo = 10 – 1mA x 6.8 K – 0.7 Vo = 2.5 V If a positive going voltage is applied to the non-inverting input terminal, Q1 base is pulled up by the input voltage and its emitter terminal tends to follow the input signal. Since Q1 and Q2 emitters are connected together, the emitter of Q2 is also pulled up by the positive going signal at the non-inverting input terminal. -

CA3140, CA3140A Datasheet

DATASHEET CA3140, CA3140A FN957 4.5MHz, BiMOS Operational Amplifier with MOSFET Input/Bipolar Output Rev.10.00 Jul 11, 2005 The CA3140A and CA3140 are integrated circuit operational Features amplifiers that combine the advantages of high voltage • MOSFET Input Stage PMOS transistors with high voltage bipolar transistors on a - Very High Input Impedance (Z ) -1.5T (Typ) single monolithic chip. IN - Very Low Input Current (Il) -10pA (Typ) at 15V The CA3140A and CA3140 BiMOS operational amplifiers - Wide Common Mode Input Voltage Range (VlCR) - Can be feature gate protected MOSFET (PMOS) transistors in the Swung 0.5V Below Negative Supply Voltage Rail input circuit to provide very high input impedance, very low - Output Swing Complements Input Common Mode input current, and high speed performance. The CA3140A Range and CA3140 operate at supply voltage from 4V to 36V • Directly Replaces Industry Type 741 in Most Applications (either single or dual supply). These operational amplifiers are internally phase compensated to achieve stable • Pb-Free Plus Anneal Available (RoHS Compliant) operation in unity gain follower operation, and additionally, have access terminal for a supplementary external capacitor Applications if additional frequency roll-off is desired. Terminals are also • Ground-Referenced Single Supply Amplifiers in provided for use in applications requiring input offset voltage Automobile and Portable Instrumentation nulling. The use of PMOS field effect transistors in the input • Sample and Hold Amplifiers stage results in common mode input voltage capability down to 0.5V below the negative supply terminal, an important • Long Duration Timers/Multivibrators attribute for single supply applications. The output stage (seconds-Minutes-Hours) uses bipolar transistors and includes built-in protection • Photocurrent Instrumentation against damage from load terminal short circuiting to either • Peak Detectors supply rail or to ground.