We are going to write the code to implement a 2-input NAND gate, specifically a SN74HC00. Note that “SN74HC00” represents an IC that contains 4 of these gates, but for simulation purposes, we’ll just use the IC part # to represent the logic function. Next, we’ll learn how to use a test bench to check the function of our unit. In this case, the simulation will be pretty boring since we are only looking at the function of one gate. Finally, we’ll see how to build a circuit from multiple gates. We will build a small circuit using the 2-input NAND gates created above and then confirm that the circuit’s output matches what we’d expect it to. Take note of commenting, formatting and naming procedures/conventions. I will expect you to use them in your projects during this class.

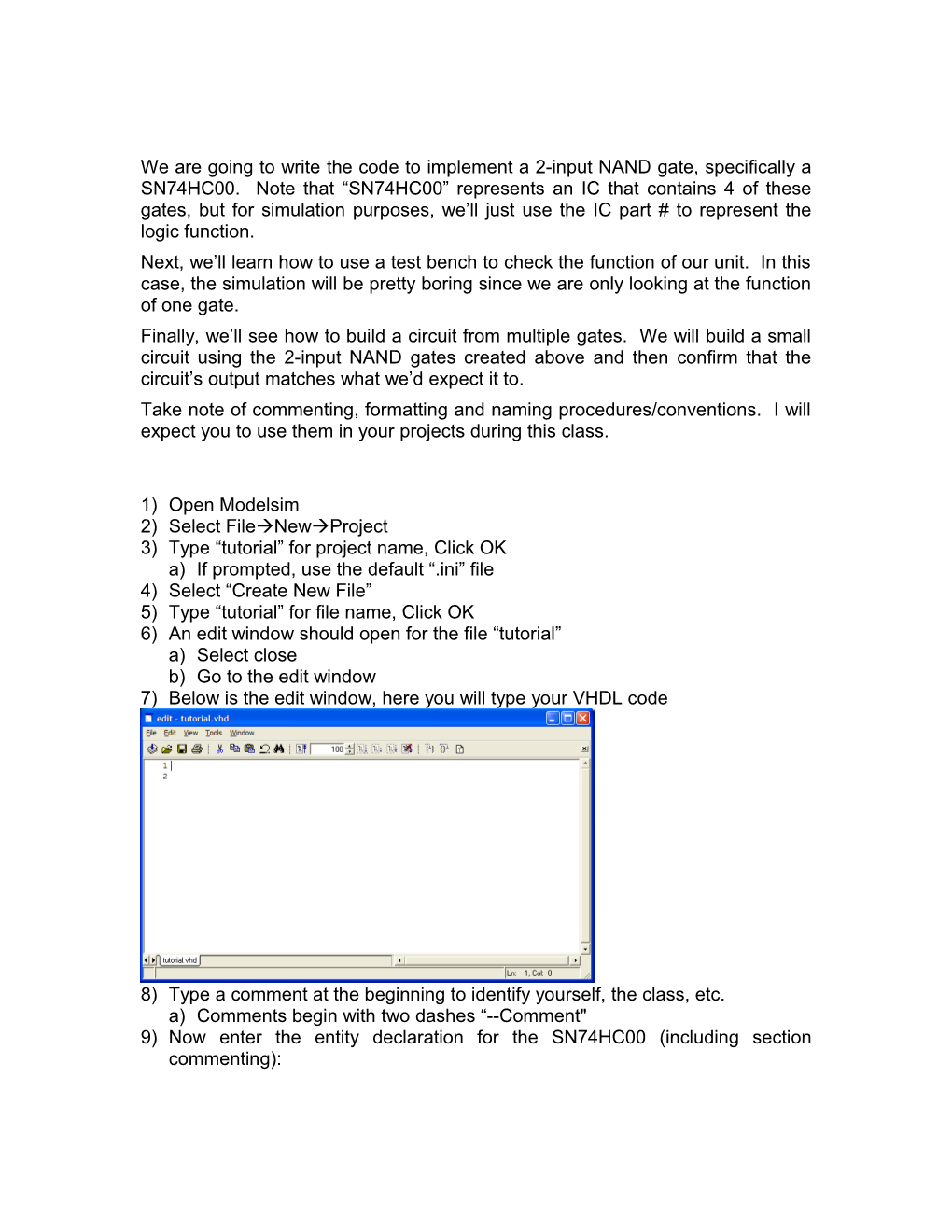

1) Open Modelsim 2) Select FileNewProject 3) Type “tutorial” for project name, Click OK a) If prompted, use the default “.ini” file 4) Select “Create New File” 5) Type “tutorial” for file name, Click OK 6) An edit window should open for the file “tutorial” a) Select close b) Go to the edit window 7) Below is the edit window, here you will type your VHDL code

8) Type a comment at the beginning to identify yourself, the class, etc. a) Comments begin with two dashes “--Comment" 9) Now enter the entity declaration for the SN74HC00 (including section commenting): 10) Take a moment to look over what you have just entered and make sure you understand what everything means. 11) Now enter the architecture of our SN74HC00:

12) Look at the function… it is wrong. Correct it to represent a NAND function. 13) Also the propagation delay (shown as 50 ns) is wrong. a) Go to www.ti.com b) Search for SN74HC00 and download (or open) the data sheet c) Find the correct propagation delay (look for tpd MAX for Vcc = 6V) d) Note that in this case, the propagation delay is the same from all inputs to all output(s). Later in the course, we may see devices where this is not the case. 14) Take a moment to look over the architecture body and make sure you understand what everything means. a) “ basic” identifies a specific instance of an SN74HC00 architecture. For now, we’ll use “basic” here for all architectures. b) This type of architecture is called Behavioral 15) Click Save 16) Click the Compile icon (top left of edit window) 17) A file-dialog will open. Click the “Compile” Button. a) Any compile errors or warnings will be shown in the main ModelSim Window b) Click the “Done” button to close the Compile file dialog 18) Switch to the main ModelSim window and check for any errors a) if there are none, move on b) if there are errors, try to correct them 19) Go to the Library tab in the left portion of the ModelSim window a) right-click on “sn74hc00” under the heading work b) Select “Simulate”

20) The “sim” tab should now appear. Under it, right-click on “sn74hc00…” and select AddAdd to Wave… 21) The wave window should pop up. This is where you will later observe the inputs and outputs of your gate/circuit. 22) Go back to the main ModelSim window and select ViewSignals. This is where we edit the signals for simulation 23) We will now enter the input signals a) Click on ‘b’. Under general conventions, this is the “Least-Significant Bit” since it is the last alphabetically. b) Select EditClock… c) The “Define Clock” window will pop up. Here we can define a repeating pattern. d) Set “Period” to 100,000. This corresponds to 100,000ps or 100ns. The other settings should default to the numbers shown above. Click OK. e) Repeat for ‘a’, but in this case set “Period” to 200,000 (note that this is 2x the next less-significant bit). 24) Go to the main ModelSim window. Select SimulateRunRun All… a) This will run the simulation Continuously 25) Select SimulateBreak a) This stops the simulation b) The source window pops up and shows where simulation halted. Close this window 26) Go to the “Wave” window a) Scroll all the way to the left so that time=0 is reached b) Zoom out until the range 0ns to at least 225ns can be seen

c) You should see something like the function above 27) Check and see if the input/output waveforms match the expected NAND function. Note the propagation delay that you entered earlier. Part II: Multiple Gate Circuits 28) Go back to the “Edit” window and add the following code in between your current entity declaration section and architecture section:

29) The above code defines the input/output structure for a “circuit” which will interconnect other gates such as the NAND created earlier. 30) At the end of your VHDL file, add the following:

This code corresponds to the following logic circuit:

A B W C D 31) The section above defines the connections of your circuit. Take a look through it and see if you understand all of the components. a) Component SN74HC00… says that the SN74HC00 NAND gate that you created earlier will be part of this circuit. If other components were to be in the circuit, they would be listed next (after “end component”). b) Signal defines local variables c) After “begin” each component in the circuit is listed and how they are interconnected. Here all 3 components are the NAND gates that you created earlier. A,B,C,D will all be external inputs. Temp1 and Temp2 are outputs of the first level circuit which will be inputted to the second level. W the only external output. d) This architecture type is called “structural” 32) Save and Compile as before. 33) Simulate as before, but, this time, make sure you select the component “Circuit” for simulation. 34) Prepare for testing as before: add the signals to “wave”, then go so “signals” and plan out an input pattern which covers all possibilities as before (try to use the same conventions for order of most-significant bit to least-significant bit). 35) Run simulation then stop as done before 36) Look at the results in the “wave” window and confirm that they match what you would expect in the circuit shown by drawing a logic table.