10-Configurable Logic.Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

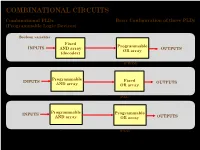

COMBINATIONAL CIRCUITS Combinational Plds Basic Configuration of Three Plds (Programmable Logic Devices)

COMBINATIONAL CIRCUITS Combinational PLDs Basic Configuration of three PLDs (Programmable Logic Devices) Boolean variables Fixed Programmable INPUTS AND array OUTPUTS OR array (decoder) Programmable Read-Only Memory (PROM) Programmable INPUTS Fixed OUTPUTS AND array OR array Programmable Array Logic (PAL) Programmable INPUTS Programmable AND array OR array OUTPUTS (Field) Programmable Logic Array (PLA) 1 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Two-level AND-OR Arrays (Programmable Logic Devices) F (C,B, A) = CBA + CB A A AND B + V B C A C B F C F AND F + V 1 B OR C Multiple functions Simplified equivalent circuit for two-level AND-OR array 2 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) Field-programmable logic elements are devices that contain uncommitted AND/OR arrays that are (programmed) configured by the designer. + V + V A A F (C,B, A) F (C,B, A) = CBA B B C C Unprogrammed AND array Fuse can be "blown" by passing a high current through it. 3 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Field-programmable AND and OR Arrays (Programmable Logic Devices) F (P1 ,P2 ,P3 ) = P1 + P3 P1 P1 P2 P2 P3 P3 F F (P1 ,P2 ,P3 ) Unprogrammed OR array Programmed OR array P1 P2 P3 P1 + P3 4 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Output Polarity Options (Programmable Logic Devices) I1 Ik Active high Active low Complementary outputs Programmable polarity P P 1 m + V 5 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs Bidirectional Pins and Feed back Lines (Programmable Logic Devices) I1 Ik Feedback IOm Three-state driver 6 ©Loberg COMBINATIONAL CIRCUITS Combinational PLDs PLA (Programmable Logic Array) (Programmable Logic Devices) If we use ROM to implement the Boolean function we will waste the silicon area. -

ASIC Implemented Microblaze-Based Coprocessor for Data Stream

ASIC-IMPLEMENTED MICROBLAZE-BASED COPROCESSOR FOR DATA STREAM MANAGEMENT SYSTEMS A Thesis Submitted to the Faculty of Purdue University by Linknath Surya Balasubramanian In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical and Computer Engineering May 2020 Purdue University Indianapolis, Indiana ii THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF THESIS APPROVAL Dr. John J. Lee, Chair Department of Electrical and Computer Engineering Dr. Lauren A. Christopher Department of Electrical and Computer Engineering Dr. Maher E. Rizkalla Department of Electrical and Computer Engineering Approved by: Dr. Brian King Head of Graduate Program iii ACKNOWLEDGMENTS I would first like to express my gratitude to my advisor Dr. John J. Lee and my thesis committee members Dr. Lauren A. Christopher and Dr. Maher E. Rizkalla for their patience, guidance, and support during this journey. I would also like to thank Mrs. Sherrie Tucker for her patience, help, and encouragement. Lastly, I must thank Dr. Pranav Vaidya and Mr. Tareq S. Alqaisi for all their support, technical guidance, and advice. Thank you all for taking time and helping me complete this study. iv TABLE OF CONTENTS Page LIST OF TABLES :::::::::::::::::::::::::::::::::: vi LIST OF FIGURES ::::::::::::::::::::::::::::::::: vii ABSTRACT ::::::::::::::::::::::::::::::::::::: ix 1 INTRODUCTION :::::::::::::::::::::::::::::::: 1 1.1 Previous Work ::::::::::::::::::::::::::::::: 1 1.2 Motivation :::::::::::::::::::::::::::::::::: 2 1.3 Thesis Outline :::::::::::::::::::::::::::::::: -

Development of a Programmable Array Logic

i DEVELOPMENT OF A PROGRAMMABLE ARRAY LOGIC PROGRAMMER USING A HOME COMPUTER by GERT DANIEL JORDAAN Dissertation submitted in compliance with the requirements for the MASTER'S DIPLOMA in TECHNOLOGY in the Department of Electronics at the TECHNIKON O. F . S . OCTOBER, 1988. Supervisor: Prof. F.W. Bruwer Co-supervisor: Mr. B. de Witt © Central University of Technology, Free State ACKNOWLEDGEMENTS I would like to thank the following persons without whose help this project could hardly have been completed: The supervisor, prof. F.W. Bruwer, and co-supervisor, mr. 8. de Witt, for help and guidance during the course of the project. Mr. H.F. Coetzer for technical as well as philolog ical assistance. It is really appreciated that time could be found in his very full schedule, for this assistance. Dr. C.A.J. van Rensburg for his per_onal interest in the research project and for continuous encouragement and help. Dr. J. van der Mer-we for his assistance - in particular with respect to the registration and other administrative aspects of the project. / Miss M. du Toit who was largely responsible for the word processing. For the guidance provided by my parents and the opportuni- ties which they afforded me. My children, Tania, Johan, Madelie and Lourens,. whose main contribution was to have to forego much of my attention and time for such a long period. Last, but not least, my wife, Christa, for her encouragement and understanding. © Central University of Technology,ii Free State CONTENTS PAGE Cilapter 1 1 Intr--oduc tion 1.1 Recent Trends in Electronics 1 1.2 Problem Investigated 1 1.3 Development of PAL Programmer 3 1.3.1 Generation of Fuse Map 3 1.3.2 Programming of Programmable Array Logic 3 Devices 1 . -

MACABEL ABEL for the APPLE MACINTOSH Nor IIX WORKSTATION A/UX VERSION

SPECIFICATIONS MACABEL ABEL FOR THE APPLE MACINTOSH nOR IIX WORKSTATION A/UX VERSION GENERAL DESCRIPTION ABEL.'" the industry standard PLD design software, is now available on the Apple Macintosh® II or IIx workstation. MacABEL allows you to take advantage of the personal productivity features of the Macintosh to easily describe and implement logic designs in programmable logic devices (PLDs) and PROMs. Like ABEL Version 3.0 for other popular workstations, MacABEL combines a natural high-level design language with a language processor that converts logic descriptions to programmer load files. These files contain the required information to program and test PLDs. MacABEL allows you to describe your design in any combi nation of Boolean equations, truth tables or state diagrams whichever best suits the logic you are describing or your comfort level. Meaningful names can be assigned to signals; signals grouped into sets; and macros used to simplify logic descriptions - making your logic design easy to read and • Boolean equations understand. • State machine diagram entry, using IF-THEN-ELSE, CASE, In addition, the software's language processor provides GOTQ and WITH-ENDWITH statements powerful logic reduction, extensive syntax and logic error • Truth tables to specify input to output relationships for both checking - before your device is programmed. MacABEL combinatorial and registered outputs supports the most powerful and innovative complex PLDs just • High-level equation entry, incorporating the boolean introduced on the market, as well as many still in development. operators used in most logic designs < 1 1 & 1 # 1 $ 1 1 $ ) , MacABEL runs under the Apple A/UX'" operating system arithmetic operators <- I + I * I I I %I < < I > > ) , relational utilizing the Macintosh user interface. -

Intel Quartus Prime Pro Edition User Guide: Partial Reconfiguration Send Feedback

Intel® Quartus® Prime Pro Edition User Guide Partial Reconfiguration Updated for Intel® Quartus® Prime Design Suite: 19.3 Subscribe UG-20136 | 2019.11.18 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Creating a Partial Reconfiguration Design.......................................................................4 1.1. Partial Reconfiguration Terminology..........................................................................5 1.2. Partial Reconfiguration Process Sequence..................................................................6 1.3. Internal Host Partial Reconfiguration........................................................................ 7 1.4. External Host Partial Reconfiguration........................................................................ 9 1.5. Partial Reconfiguration Design Considerations............................................................9 1.5.1. Partial Reconfiguration Design Guidelines.................................................... 11 1.5.2. PR File Management.................................................................................12 1.5.3. Evaluating PR Region Initial Conditions....................................................... 16 1.5.4. Creating Wrapper Logic for PR Regions........................................................16 1.5.5. Creating Freeze Logic for PR Regions.......................................................... 17 1.5.6. Resetting the PR Region Registers.............................................................. 18 1.5.7. Promoting -

CHAPTER 3: Combinational Logic Design with Plds

CHAPTER 3: Combinational Logic Design with PLDs LSI chips that can be programmed to perform a specific function have largely supplanted discrete SSI and MSI chips in board-level designs. A programmable logic device (PLD), is an LSI chip that contains a “regular” circuit structure, but that allows the designer to customize it for a specific application. PLDs sold in the market is not customized with specific functions. Instead, it is programmed by the purchaser to perform a function required by a particular application. PLD-based board-level designs often cost less than SSI/MSI designs for a number of reasons. Since PLDs provide more functionality per chip, the total chip and printed- circuit-board (PCB) area are less. Manufacturing costs are reduced in other ways too. A PLD-based board manufacturer needs to keep samples of few, “generic” PLD types, instead of many different MSI part types. This reduces overall inventory requirements and simplifies handling. PLD-type structures also appear as logic elements embedded in LSI chips, where chip count and board areas are not an issue. Despite the fact that a PLD may “waste” a certain number of gates, a PLD structure can actually reduce circuit cost because its “regular” physical structure may use less chip area than a “random logic” circuit. More importantly, the logic function performed by the PLD structure can often be “tweaked” in successive chip revisions by changing just one or a few metal mask layers that define signal connections in the array, instead of requiring a wholesale addition of gates and gate inputs and subsequent re-layout of a “random logic” design. -

A Soft Processor Microblaze-Based Embedded System for Cardiac Monitoring

(IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 4, No. 9, 2013 A Soft Processor MicroBlaze-Based Embedded System for Cardiac Monitoring El Hassan El Mimouni Mohammed Karim University Sidi Mohammed Ben Abdellah University Sidi Mohammed Ben Abdellah Fès, Morocco Fès, Morocco Abstract—this paper aims to contribute to the efforts of recent years, and has become also an important way to assert design community to demonstrate the effectiveness of the state of the heart’s condition [5 - 9]. the art Field Programmable Gate Array (FPGA), in the embedded systems development, taking a case study in the II. SYSTEM OVERVIEW biomedical field. With this design approach, we have developed a We have designed and implemented a prototype of basic System on Chip (SoC) for cardiac monitoring based on the soft embedded system for cardiac monitoring, whose functional processor MicroBlaze and the Xilkernel Real Time Operating block diagram is shown in the figure 2; it exhibits a modular System (RTOS), both from Xilinx. The system permits the structure that facilitates the development and debugging. Thus, acquisition and the digitizing of the Electrocardiogram (ECG) analog signal, displaying heart rate on seven segments module it includes 2 main modules: and ECG on Video Graphics Adapter (VGA) screen, tracing the An analog module intended for acquiring and heart rate variability (HRV) tachogram, and communication conditioning of the analog ECG signal to make it with a Personal Computer (PC) via the serial port. We have used appropriate for use by the second digital module ; the MIT_BIH Database records to test and evaluate our implementation performance. -

RESEARCH INSIGHTS – Hardware Design: FPGA Security Risks

RESEARCH INSIGHTS Hardware Design: FPGA Security Risks www.nccgroup.trust CONTENTS Author 3 Introduction 4 FPGA History 6 FPGA Development 10 FPGA Security Assessment 12 Conclusion 17 Glossary 18 References & Further Reading 19 NCC Group Research Insights 2 All Rights Reserved. © NCC Group 2015 AUTHOR DUNCAN HURWOOD Duncan is a senior consultant at NCC Group, specialising in telecom, embedded systems and application review. He has over 18 years’ experience within the telecom and security industry performing almost every role within the software development cycle from design and development to integration and product release testing. A dedicated security assessor since 2010, his consultancy experience includes multiple technologies, languages and platforms from web and mobile applications, to consumer devices and high-end telecom hardware. NCC Group Research Insights 3 All Rights Reserved. © NCC Group 2015 GLOSSARY AES Advanced encryption standard, a cryptography OTP One time programmable, allowing write once cipher only ASIC Application-specific integrated circuit, non- PCB Printed circuit board programmable hardware logic chip PLA Programmable logic array, forerunner of FPGA Bitfile Binary instruction file used to program FPGAs technology CLB Configurable logic block, an internal part of an PUF Physically unclonable function FPGA POWF Physical one-way function CPLD Complex programmable logic device PSoC Programmable system on chip, an FPGA and EEPROM Electronically erasable programmable read- other hardware on a single chip only memory -

Performance Evaluation of FPGA Based Embedded ARM Processor

10.1109/ULTSYM.2013.0135 Performance Evaluation of FPGA based Embedded ARM Processor for Ultrasonic Imaging Spenser Gilliland, Pramod Govindan, Thomas Gonnot and Jafar Saniie Department of Electrical and Computer Engineering Illinois Institute of Technology, Chicago IL, U.S.A. Abstract- This study evaluates the performance of an FPGA based embedded ARM processor system to implement signal processing for ultrasonic imaging and nondestructive testing applications. FPGA based embedded processors possess many advantages including a reduced overall development time, increased performance, and the ability to perform hardware- software (HW/SW) co-design. This study examines the execution performance of split spectrum processing, chirplet signal decomposition, Wigner-Ville distributions and short time Fourier transform implementations, on two embedded processing platforms: a Xilinx Virtex-5 FPGA with embedded MicroBlaze processor and a Xilinx Zynq FPGA with embedded ARM processor. Overall, the Xilinx Zynq FPGA significantly outperforms the Virtex-5 based system in software applications I. INTRODUCTION Figure 1. RUSH SoC setup Generally, ultrasonic imaging applications use personal computers or hand held devices. As these devices are not frequency diverse flaw detection [1], parametric echo specifically designed for efficiently executing estimation [2], and joint time-frequency distribution [3]) on computationally intensive ultrasonic signal processing the RUSH platform using a Xilinx Virtex-5 FPGA with an algorithms, the performance of these applications can be embedded soft-core MicroBlaze processor [4,5] and a improved by executing the algorithms using a dedicated Xilinx Zynq 7020 FPGA with an embedded ARM processor embedded system-on-chip (SoC) hardware. However, [6,7] as shown in Figure 2. porting these applications onto an embedded system requires deep knowledge of the processor architecture and RUSH embedded software development tools. -

Review of FPD's Languages, Compilers, Interpreters and Tools

ISSN 2394-7314 International Journal of Novel Research in Computer Science and Software Engineering Vol. 3, Issue 1, pp: (140-158), Month: January-April 2016, Available at: www.noveltyjournals.com Review of FPD'S Languages, Compilers, Interpreters and Tools 1Amr Rashed, 2Bedir Yousif, 3Ahmed Shaban Samra 1Higher studies Deanship, Taif university, Taif, Saudi Arabia 2Communication and Electronics Department, Faculty of engineering, Kafrelsheikh University, Egypt 3Communication and Electronics Department, Faculty of engineering, Mansoura University, Egypt Abstract: FPGAs have achieved quick acceptance, spread and growth over the past years because they can be applied to a variety of applications. Some of these applications includes: random logic, bioinformatics, video and image processing, device controllers, communication encoding, modulation, and filtering, limited size systems with RAM blocks, and many more. For example, for video and image processing application it is very difficult and time consuming to use traditional HDL languages, so it’s obligatory to search for other efficient, synthesis tools to implement your design. The question is what is the best comparable language or tool to implement desired application. Also this research is very helpful for language developers to know strength points, weakness points, ease of use and efficiency of each tool or language. This research faced many challenges one of them is that there is no complete reference of all FPGA languages and tools, also available references and guides are few and almost not good. Searching for a simple example to learn some of these tools or languages would be a time consuming. This paper represents a review study or guide of almost all PLD's languages, interpreters and tools that can be used for programming, simulating and synthesizing PLD's for analog, digital & mixed signals and systems supported with simple examples. -

Ice40 Ultraplus Family Data Sheet

iCE40 UltraPlus™ Family Data Sheet FPGA-DS-02008 Version 1.4 August 2017 iCE40 UltraPlus™ Family Data Sheet Copyright Notice Copyright © 2017 Lattice Semiconductor Corporation. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Lattice Semiconductor Corporation and/or its affiliates. All rights are reserved. You are permitted to use this document and any information contained therein expressly and only for bona fide non-commercial evaluation of products and/or services from Lattice Semiconductor Corporation or its affiliates; and only in connection with your bona fide consideration of purchase or license of products or services from Lattice Semiconductor Corporation or its affiliates, and only in accordance with the terms and conditions stipulated. Contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Lattice Semiconductor Corporation and/or its affiliates. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, create derivative works of, transfer, sublicense, publicly display, distribute or otherwise make these materials available, in whole or in part, to any third party. You are not permitted to reverse engineer, disassemble, or decompile any device or object code provided herewith. Lattice Semiconductor Corporation reserves the right to revoke these permissions and require the destruction or return of any and all Lattice Semiconductor Corporation proprietary materials and/or data. Patents The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Lattice Semiconductor Corporation and/or its affiliates. -

Programmable Logic Design Quick Start Hand Book

Second Edition Programmable Logic Design Quick Start Hand Book By Karen Parnell & Nick Mehta January 2002 ABSTRACT Whether you design with discrete logic, base all of your designs on microcontrollers, or simply want to learn how to use the latest and most advanced programmable logic software, you will find this book an interesting insight into a different way to design. Programmable logic devices were invented in the late seventies and since then have proved to be very popular and are now one of the largest growing sectors in the semiconductor industry. Why are programmable logic devices so widely used? Programmable logic devices provide designers ultimate flexibility, time to market advantage, design integration, are easy to design with and can be reprogrammed time and time again even in the field to upgrade system functionality. This book was written to complement the popular XilinxÒ Campus Seminar series but can also be used as a stand-alone tutorial and information source for the first of your many programmable logic designs. After you have finished your first design this book will prove useful as a reference guide or quick start handbook. The book details the history of programmable logic, where and how to use them, how to install the free, full functioning design software (Xilinx WebPACKä ISE included with this book) and then guides you through your first of many designs. There are also sections on VHDL and schematic capture design entry and finally a data bank of useful applications examples. We hope you find the book practical, informative and above all easy to use.