Worked Solutions to Selected Problems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lab 7: Floating-Point Addition 0.0

Lab 7: Floating-Point Addition 0.0 Introduction In this lab, you will write a MIPS assembly language function that performs floating-point addition. You will then run your program using PCSpim (just as you did in Lab 6). For testing, you are provided a program that calls your function to compute the value of the mathematical constant e. For those with no assembly language experience, this will be a long lab, so plan your time accordingly. Background You should be familiar with the IEEE 754 Floating-Point Standard, which is described in Section 3.6 of your book. (Hopefully you have read that section carefully!) Here we will be dealing only with single precision floating- point values, which are formatted as follows (this is also described in the “Floating-Point Representation” subsec- tion of Section 3.6 in your book): Sign Exponent (8 bits) Significand (23 bits) 31 30 29 ... 24 23 22 21 ... 0 Remember that the exponent is biased by 127, which means that an exponent of zero is represented by 127 (01111111). The exponent is not encoded using 2s-complement. The significand is always positive, and the sign bit is kept separately. Note that the actual significand is 24 bits long; the first bit is always a 1 and thus does not need to be stored explicitly. This will be important to remember when you write your function! There are several details of IEEE 754 that you will not have to worry about in this lab. For example, the expo- nents 00000000 and 11111111 are reserved for special purposes that are described in your book (representing zero, denormalized numbers and NaNs). -

AMD Athlon™ Processor X86 Code Optimization Guide

AMD AthlonTM Processor x86 Code Optimization Guide © 2000 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other applica- tion in which the failure of AMD’s product could create a situation where per- sonal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, AMD Athlon, K6, 3DNow!, and combinations thereof, AMD-751, K86, and Super7 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. -

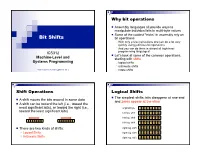

Bit Shifts Bit Operations, Logical Shifts, Arithmetic Shifts, Rotate Shifts

Why bit operations Assembly languages all provide ways to manipulate individual bits in multi-byte values Some of the coolest “tricks” in assembly rely on Bit Shifts bit operations With only a few instructions one can do a lot very quickly using judicious bit operations And you can do them in almost all high-level ICS312 programming languages! Let’s look at some of the common operations, Machine-Level and starting with shifts Systems Programming logical shifts arithmetic shifts Henri Casanova ([email protected]) rotate shifts Shift Operations Logical Shifts The simplest shifts: bits disappear at one end A shift moves the bits around in some data and zeros appear at the other A shift can be toward the left (i.e., toward the most significant bits), or toward the right (i.e., original byte 1 0 1 1 0 1 0 1 toward the least significant bits) left log. shift 0 1 1 0 1 0 1 0 left log. shift 1 1 0 1 0 1 0 0 left log. shift 1 0 1 0 1 0 0 0 There are two kinds of shifts: right log. shift 0 1 0 1 0 1 0 0 Logical Shifts right log. shift 0 0 1 0 1 0 1 0 Arithmetic Shifts right log. shift 0 0 0 1 0 1 0 1 Logical Shift Instructions Shifts and Numbers Two instructions: shl and shr The common use for shifts: quickly multiply and divide by powers of 2 One specifies by how many bits the data is shifted In decimal, for instance: multiplying 0013 by 10 amounts to doing one left shift to obtain 0130 Either by just passing a constant to the instruction multiplying by 100=102 amounts to doing two left shifts to obtain 1300 Or by using whatever -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Emergent Formal Functions in Schubert's Piano Sonatas

Louisiana State University LSU Digital Commons LSU Master's Theses Graduate School June 2020 Emergent Formal Functions in Schubert's Piano Sonatas Yiqing Ma Louisiana State University and Agricultural and Mechanical College Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool_theses Part of the Musicology Commons, and the Music Theory Commons Recommended Citation Ma, Yiqing, "Emergent Formal Functions in Schubert's Piano Sonatas" (2020). LSU Master's Theses. 5156. https://digitalcommons.lsu.edu/gradschool_theses/5156 This Thesis is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Master's Theses by an authorized graduate school editor of LSU Digital Commons. For more information, please contact [email protected]. EMEGERT FOMAL FUNCTIONS IN SCHUBERT’S PIANO SONATAS A Thesis Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirement for the degree of Master of Music in School of Music by Yiqing Ma B.A., University of Minnesota, 2017 August 2020 ã Copyright by Yiqing Ma, 2020. All rights reserved. ii ACKNOWLEDGMENT I first encountered Franz Schubert’s A minor piano sonata in my sophomore year by Dr. Rie Tanaka—a piece that I also performed in my first piano recital. As a psychology major at the time, I never would have thought I will pursue graduate studies in Music Theory, a discipline that my parents still do not understand what it is all about. Now, I am lucky enough to dedicate a master’s thesis on my favorite piano repertoire. -

National Numbering Plan – a Revised Approach Suggested by TRAI for Achieving Greater Transparency and Efficiency

Telecom Regulatory Authority of India (TRAI) National Numbering Plan – a revised approach suggested by TRAI for achieving greater transparency and efficiency March 2009 Mahanagar Doorsanchar Bhawan Jawahar Lal Nehru Marg New Delhi-110002 Web: www.trai.gov.in Preface Telecommunications sector in the country is undergoing a transformation brought about by rapid growth and technological developments. New paradigms are emerging as telecommunications, IT and broadcasting industries converge. Being conscious of the fact that some of these developments would have a profound impact on the National Numbering Plan, the Authority constituted an internal Research Team to suggest a revised approach to the numbering plan for achieving greater transparency and efficiency. The following issues have been analyzed in the Research Paper in detail: 1. Measures that can be taken for optimal utilization of numbers, short codes and IN SCP Codes 2. Pricing of numbers 3. Long term suitability of numbering plan keeping in view the growth of traditional and development of IP networks 4. Impact of Mobile Number Portability (MNP) and Carrier Selection on the numbering plan 5. Review of SDCA based Numbering Scheme The research paper has been placed on the TRAI's website (www.trai.gov.in). Written comments on the issues raised in the paper may please be furnished th to Principal Advisor (FN), TRAI by 20 March, 2009. The comments may be sent in writing and also preferably be sent in electronic form e-mail: [email protected], [email protected], Tel.: 011-23216930, Fax: -

MUS 233 Form I Form: the Shape of a Musical Composition As Defined By

MUS 233 Form I Form: The shape of a musical composition as defined by all of its pitches, rhythms, dynamics, and timbres...a loose group of general features shared in varying degrees by a relatively large number of works, no two which are exactly the same. The New Harvard Dictionary of Music. Randel, Don Michael, ed. Cambridge: The Belknap Press of Harvard University Press, 1986. P. 320. Binary Form: A two part-form where the sections are equivalent, but not necessarily equal in length; as long as they balance each other in some sense. Each part usually repeats. The second half is longer and usually touches on other keys (X) before returning to the tonic. Balanced: In a binary form where the A and B sections end in a parallel (same melodic/harmonic material) way, but not necessarily in the same key. (Please disregard the Kostka/Payne definition, which relates the term to merely the length of each section). Sectional: The first part ends in tonic harmony (i.e. an authentic cadence on the original tonic). Thematic material ||: A :||: B :|| Harmonic content (maj) I-----------I V--------(X)-----------I (min) i-----------i V, V/III, III--(X)-----i Continuous: The first part ends in something other than tonic harmony (like on V, or on the tonic of a new key). Thematic material ||: A :||: B :|| Harmonic content (maj) I-----------V -----------(X)-----------I (min) i-----------V, V/III, III---(X)--------i Two reprise: A term used when the sections repeat (either written-out repeats or not). Ternary Form: A three-part (ABA’) form: ||:A :||: B A’ :|| (repeats not required) • A and A’ need not be 100% identical • Often the B section material is thematically related to the A section material. -

Simple Computer Example Register Structure

Simple Computer Example Register Structure Read pp. 27-85 Simple Computer • To illustrate how a computer operates, let us look at the design of a very simple computer • Specifications 1. Memory words are 16 bits in length 2. 2 12 = 4 K words of memory 3. Memory can be accessed in one clock cycle 4. Single Accumulator for ALU (AC) 5. Registers are fully connected Simple Computer Continued 4K x 16 Memory MAR 12 MDR 16 X PC 12 ALU IR 16 AC Simple Computer Specifications (continued) 6. Control signals • INCPC – causes PC to increment on clock edge - [PC] +1 PC •ACin - causes output of ALU to be stored in AC • GMDR2X – get memory data register to X - [MDR] X • Read (Write) – Read (Write) contents of memory location whose address is in MAR To implement instructions, control unit must break down the instruction into a series of register transfers (just like a complier must break down C program into a series of machine level instructions) Simple Computer (continued) • Typical microinstruction for reading memory State Register Transfer Control Line(s) Next State 1 [[MAR]] MDR Read 2 • Timing State 1 State 2 During State 1, Read set by control unit CLK - Data is read from memory - MDR changes at the Read beginning of State 2 - Read is completed in one clock cycle MDR Simple Computer (continued) • Study: how to write the microinstructions to implement 3 instructions • ADD address • ADD (address) • JMP address ADD address: add using direct addressing 0000 address [AC] + [address] AC ADD (address): add using indirect addressing 0001 address [AC] + [[address]] AC JMP address 0010 address address PC Instruction Format for Simple Computer IR OP 4 AD 12 AD = address - Two phases to implement instructions: 1. -

The Hexadecimal Number System and Memory Addressing

C5537_App C_1107_03/16/2005 APPENDIX C The Hexadecimal Number System and Memory Addressing nderstanding the number system and the coding system that computers use to U store data and communicate with each other is fundamental to understanding how computers work. Early attempts to invent an electronic computing device met with disappointing results as long as inventors tried to use the decimal number sys- tem, with the digits 0–9. Then John Atanasoff proposed using a coding system that expressed everything in terms of different sequences of only two numerals: one repre- sented by the presence of a charge and one represented by the absence of a charge. The numbering system that can be supported by the expression of only two numerals is called base 2, or binary; it was invented by Ada Lovelace many years before, using the numerals 0 and 1. Under Atanasoff’s design, all numbers and other characters would be converted to this binary number system, and all storage, comparisons, and arithmetic would be done using it. Even today, this is one of the basic principles of computers. Every character or number entered into a computer is first converted into a series of 0s and 1s. Many coding schemes and techniques have been invented to manipulate these 0s and 1s, called bits for binary digits. The most widespread binary coding scheme for microcomputers, which is recog- nized as the microcomputer standard, is called ASCII (American Standard Code for Information Interchange). (Appendix B lists the binary code for the basic 127- character set.) In ASCII, each character is assigned an 8-bit code called a byte. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

Franz Schubert's Impromptus D. 899 and D. 935: An

FRANZ SCHUBERT’S IMPROMPTUS D. 899 AND D. 935: AN HISTORICAL AND STYLISTIC STUDY A doctoral document submitted to the Division of Research and Advanced Studies of the University of Cincinnati In partial fulfillment of the requirements for the degree of DOCTOR OF MUSICAL ARTS In the Keyboard Studies Division of the College-Conservatory of Music 2005 by Ina Ham M.M., Cleveland Institute of Music, 1999 M.M., Seoul National University, 1996 B.M., Seoul National University, 1994 Committee Chair: Dr. Melinda Boyd ABSTRACT The impromptu is one of the new genres that was conceived in the early nineteenth century. Schubert’s two sets of impromptus D. 899 and D. 935 are among the most important examples to define this new genre and to represent the composer’s piano writing style. Although his two sets of four impromptus have been favored in concerts by both the pianists and the audience, there has been a lack of comprehensive study of them as continuous sets. Since the tonal interdependence between the impromptus of each set suggests their cyclic aspects, Schubert’s impromptus need to be considered and be performed as continuous sets. The purpose of this document is to provide useful resources and performance guidelines to Schubert’s two sets of impromptus D. 899 and D. 935 by examining their historical and stylistic features. The document is organized into three chapters. The first chapter traces a brief history of the impromptu as a genre of piano music, including the impromptus by Jan Hugo Voŕišek as the first pieces in this genre. -

MIPS IV Instruction Set

MIPS IV Instruction Set Revision 3.2 September, 1995 Charles Price MIPS Technologies, Inc. All Right Reserved RESTRICTED RIGHTS LEGEND Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and / or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor / manufacturer is MIPS Technologies, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94039-7311. R2000, R3000, R6000, R4000, R4400, R4200, R8000, R4300 and R10000 are trademarks of MIPS Technologies, Inc. MIPS and R3000 are registered trademarks of MIPS Technologies, Inc. The information in this document is preliminary and subject to change without notice. MIPS Technologies, Inc. (MTI) reserves the right to change any portion of the product described herein to improve function or design. MTI does not assume liability arising out of the application or use of any product or circuit described herein. Information on MIPS products is available electronically: (a) Through the World Wide Web. Point your WWW client to: http://www.mips.com (b) Through ftp from the internet site “sgigate.sgi.com”. Login as “ftp” or “anonymous” and then cd to the directory “pub/doc”. (c) Through an automated FAX service: Inside the USA toll free: (800) 446-6477 (800-IGO-MIPS) Outside the USA: (415) 688-4321 (call from a FAX machine) MIPS Technologies, Inc.