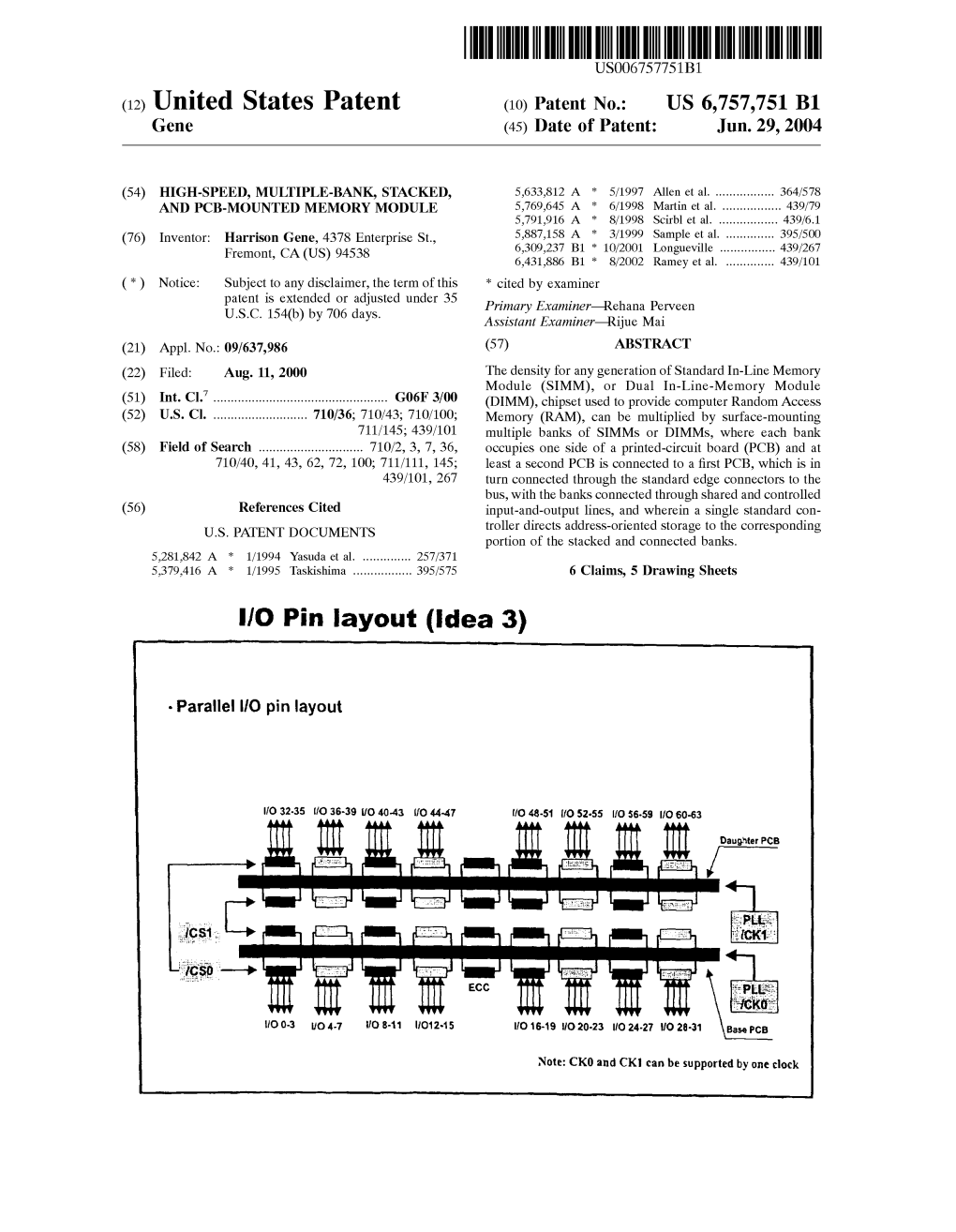

I/O Pin Layout (Idea 3)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Kontron Design Guide ®

® Kontron Design Guide ® ETX® Document Revision 2.4 This page intentionally left blank Table of Contents Table of Contents 1 User Information ........................................................................................................ 6 1.1 Objective ......................................................................................................... 6 1.2 Target Audience ................................................................................................ 6 1.3 Assumptions .................................................................................................... 6 1.4 Scope.............................................................................................................. 6 1.5 About This Document ......................................................................................... 6 1.6 Copyright Notice ............................................................................................... 7 1.7 Trademarks ...................................................................................................... 7 1.8 Standards ........................................................................................................ 7 1.9 Warranty ......................................................................................................... 7 1.10 Technical Support .............................................................................................. 8 2 Introduction ............................................................................................................. -

A4000/A3000 Hardware

A4000/A3000 H ardware D eveloper N otes P art I: T he Z orro III Bus S pecification P art II: T he A miga Local B us Slot P art III: T he A miga V ideo S lot Document Revision 1.11 December 1992 by Dave Haynie with Scott Schaeffer, Scott Hood and Dan Baker Copyright © 1990,1991,1992 Commodore-Amiga, Inc. Important Information "A life spent maJäng mistakes is not onty more honorable but more usefuljhan a life spent doing nothing." -George Bernard Shaw This Pocument Contains Preliminarv Information The Information contained here is preliminary in nature and subject to possible errors and omissions. Few Zorro ID cards have yet been designed, so some features described here have not actually been tested in a System, or in some cases, actuaUy implemented as of this wridng. That, of course, is one major reason for having a specification in the first place. Commodore Technology reserves the right to correct any mistake, error, omission (or viscious lie). Corrections will be published as Updates to this document, which will be released as necessary. Revisions will be tracked via the revison number that appears on the front cover. New revisions will always list the conections up front, and developers will be kept up to date on released revisions via the normal CATS channels. All Information herein is Copyright © 1990,1991,1992 by Commodore-Amiga, Inc., and may not be reproduced in any form without permission. A cknowledgements "Art is I; Science is we." -Claude Bernard I’d like to acknowledge the following people and groups, without whom this new stuff would have been impossible: • The original Amiga designers, for designing the first microcomputer bus with support for multiple masters, Software board configuration, and room to grow. -

PCI Local Bus Specification

PCI Local Bus Specification Revision 2.2 December 18, 1998 Revision 2.2 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and expansion board specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 7KH3&,6SHFLDO,QWHUHVW*URXSGLVFODLPVDOOZDUUDQWLHVDQGOLDELOLW\IRUWKHXVHRIWKLVGRFXPHQW DQGWKHLQIRUPDWLRQFRQWDLQHGKHUHLQDQGDVVXPHVQRUHVSRQVLELOLW\IRUDQ\HUURUVWKDWPD\DSSHDU LQ WKLV GRFXPHQW QRU GRHV WKH 3&, 6SHFLDO ,QWHUHVW *URXS PDNH D FRPPLWPHQW WR XSGDWH WKH LQIRUPDWLRQFRQWDLQHGKHUHLQ &RQWDFWWKH3&,6SHFLDO,QWHUHVW*URXSRIILFHWRREWDLQWKHODWHVWUHYLVLRQRIWKHVSHFLILFDWLRQ 4XHVWLRQVUHJDUGLQJWKH3&,VSHFLILFDWLRQRUPHPEHUVKLSLQWKH3&,6SHFLDO,QWHUHVW*URXSPD\EH IRUZDUGHGWR 3&,6SHFLDO,QWHUHVW*URXS 1(.DWKU\Q +LOOVERUR2UHJRQ 3KRQH ,QVLGHWKH86 2XWVLGHWKH86 )D[ HPDLO SFLVLJ#SFLVLJFRP http://www.pcisig.com ',6&/$,0(5 7KLV3&,/RFDO%XV6SHFLILFDWLRQLVSURYLGHGDVLVZLWKQRZDUUDQWLHVZKDWVRHYHU LQFOXGLQJDQ\ZDUUDQW\RIPHUFKDQWDELOLW\QRQLQIULQJHPHQWILWQHVVIRUDQ\SDUWLFXODU SXUSRVHRUDQ\ZDUUDQW\RWKHUZLVHDULVLQJRXWRIDQ\SURSRVDOVSHFLILFDWLRQRUVDPSOH 7KH3&,6,*GLVFODLPVDOOOLDELOLW\IRULQIULQJHPHQWRISURSULHWDU\ULJKWVUHODWLQJWRXVH RILQIRUPDWLRQLQWKLVVSHFLILFDWLRQ1ROLFHQVHH[SUHVVRULPSOLHGE\HVWRSSHORU RWKHUZLVHWRDQ\LQWHOOHFWXDOSURSHUW\ULJKWVLVJUDQWHGKHUHLQ $/3+$LVDUHJLVWHUHGWUDGHPDUNRI'LJLWDO(TXLSPHQW&RUSRUDWLRQ )LUH:LUHLVDWUDGHPDUNRI$SSOH&RPSXWHU,QF 7RNHQ5LQJDQG9*$DUHWUDGHPDUNVDQG36,%00LFUR&KDQQHO26DQG3&$7DUHUHJLVWHUHG WUDGHPDUNVRI,%0&RUSRUDWLRQ :LQGRZV06'26DQG0LFURVRIWDUHUHJLVWHUHGWUDGHPDUNVRI0LFURVRIW&RUSRUDWLRQ -

OMB-PER/488 Operator's Manual

OMEGAnetSM On-Line Service Internet e-mail http://www.omega.com [email protected] Servicing North America: USA: One Omega Drive, Box 4047 Stamford, CT 06907-0047 Tel: (203) 359-1660 FAX: (203) 359-7700 e-mail: [email protected] Canada: 976 Berger Laval (Quebec) H7L 5A1 Tel: (514) 856-6928 FAX: (514) 856-6886 e-mail: [email protected] For immediate technical or application assistance: USA and Canada: Sales Service: 1-800-826-6342 / 1-800-TC-OMEGASM Customer Service: 1-800-622-2378 / 1-800-622-BESTSM Engineering Service: 1-800-872-9436 / 1-800-USA-WHENSM TELEX: 996404 EASYLINK: 62968934 CABLE: OMEGA Mexico and Latin America: Tel: (95) 800-TC-OMEGASM FAX: (95) 203-359-7807 En Espanol: (95) 203-359-7803 e-mail: [email protected] Servicing Europe: Benelux: Postbus 8034, 1180 LA Amstelveen, The Netherlands Tel: (31) 20 6418405 FAX: (31) 20 6434643 Toll Free in Benelux: 06 0993344 e-mail: [email protected] Czech Republic: ul. Rude armady 1868 733 01 Karvina-Hranice Tel: 420 (69) 6311899 FAX: 420 (69) 6311114 e-mail:[email protected] France: 9, rue Denis Papin, 78190 Trappes Tel: (33) 130-621-400 FAX: (33) 130-699-120 Toll Free in France: 0800-4-06342 e-mail: [email protected] Germany/Austria: Daimlerstrasse 26, D-75392 Deckenpfronn, Germany Tel: 49 (07056) 3017 FAX: 49 (07056) 8540 Toll Free in Germany: 0130 11 21 66 e-mail: [email protected] United Kingdom: 25 Swannington Road, P.O. Box 7, Omega Drive, Broughton Astley, Leicestershire, Irlam, Manchester, LE9 6TU, England M44 5EX, England Tel: 44 (1455) 285520 Tel: 44 (161) 777-6611 FAX: 44 (1455) 283912 FAX: 44 (161) 777-6622 Toll Free in England: 0800-488-488 e-mail: [email protected] It is the policy of OMEGA to comply with all worldwide safety and EMC/EMI regulations that apply. -

Bus Interface Bus Interfaces Different Types of Buses: ISA (Industry

Systems Design & Programming Bus Interface CMPE 310 Bus Interfaces Different types of buses: P ISA (Industry Standard Architecture) P EISA (Extended ISA) P VESA (Video Electronics Standards Association, VL Bus) P PCI (Peripheral Component Interconnect) P USB (Universal Serial Bus) P AGP (Advanced Graphics Port) ISA is the oldest of all these and today's computers still have a ISA bus interface in form of an ISA slot (connection) on the main board. ISA has 8-bit and 16-bit standards along with the 32-bit version (EISA). All three versions operate at 8MHz. 1 Systems Design & Programming Bus Interface CMPE 310 8-Bit ISA Bus connector Pin # 1 GND IO CHK 2 RESET 3 +5V 4 IRQ9 5 -5V 6 DRQ2 D0-D7 7 -12V 8 OWS 9 +12V ISA Bus Connector Contains 10 GND IO RDY } 11 MEMW AEN 12 MEMR 8- bit Data Bus 13 IOW 14 IOR 15 DACK3 Demultiplexed 20-bit address Bus 16 DRQ3 17 DACK1 18 DRQ1 I/O and Memory Control Signals 19 DACK0 20 CLOCK 21 IRQ7 Interrupt Request Lines (IRQ2->IRQ9) 22 IRQ6 A0-A19 23 IRQ5 DMA channels 1-3 Control Signals 24 IRQ4 25 IRQ3 26 DACK2 Power, RESET and misc. signals 27 T/C 28 ALE 29 +5V 30 OSC 31 GND } 2 Systems Design & Programming Bus Interface CMPE 310 8-Bit ISA Bus Output Interface D0-D7 Connector DB37 D0 1Y1 . D0. Q0. D7 2Y1 74LS244 D7 Q7 OC 74LS374 CLK A0 A Y0 A1 B . D0 Q0 . IOW C . A3 G1 . G2A Y7 G2B D7 74LS374 Q7 OC CLK D0 Q0 A4 A Y0 . -

PCI Local Bus Specification

PCI Local Bus Specification Revision 2.3 March 29, 2002 Revision 2.3 REVISION REVISION HISTORY DATE 1.0 Original issue 6/22/92 2.0 Incorporated connector and add-in card specification 4/30/93 2.1 Incorporated clarifications and added 66 MHz chapter 6/1/95 2.2 Incorporated ECNs and improved readability 12/18/98 2.3 Incorporated ECNs, errata, and deleted 5 volt only keyed 3/29/02 add-in cards The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does the PCI Special Interest Group make a commitment to update the information contained herein. Contact the PCI Special Interest Group office to obtain the latest revision of the specification. Questions regarding the PCI specification or membership in the PCI Special Interest Group may be forwarded to: PCI Special Interest Group 5440 SW Westgate Drive Suite 217 Portland, Oregon 97221 Phone: 800-433-5177 (Inside the U.S.) 503-291-2569 (Outside the U.S.) Fax: 503-297-1090 e-mail [email protected] http://www.pcisig.com DISCLAIMER This PCI Local Bus Specification is provided "as is" with no warranties whatsoever, including any warranty of merchantability, noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The PCI SIG disclaims all liability for infringement of proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein. -

Power Macintosh 8600/ 9600 & WS 9650

K Service Source Power Macintosh 8600/ 9600 & WS 9650 Power Macintosh 8600/200, 8600/250, 8600/300, 9600/200, 9600MP/200, 9600/233, 9600/300, 9600/350, WS 9650/233, and WS 9650/350 K Service Source Basics Power Macintosh 8600/9600 & WS 9650 Basics Overview - 1 Overview The Power Macintosh 8600, 9600, and Workgroup Server 9650 computers share the same housing. These systems feature a chassis design that allows you to access the logic board and its components (including the plug-in microprocessor card) simply by removing the side access panel. This flexible design makes these systems easy to service and upgrade. Basics Overview - 2 Features of the Power Macintosh 8600/200 include • 200 MHz PowerPC™ 604e microprocessor card with built-in FPU • 32 MB of DRAM, expandable to 512 MB using 168-pin, 70 ns, 64-bit EDO* DRAM DIMMs • 256K Level 2 cache • 2 MB VRAM, expandable to 4 MB • 2 GB hard drive • Two SCSI DMA buses supporting up to eight SCSI devices and transfers up to 10 MB/s (internal bus only) • Three PCI expansion slots • 24-bit video input/output support • Built-in AAUI and 10BASE-T Ethernet • Two GeoPort serial ports • CD-ROM drive at 12x-speed • Zip drive • CD-quality stereo sound in/out Basics Overview - 3 • Support for Open Transport networking • Mac™ OS system software 7.5.5 Features of the Power Macintosh 8600/250 and 8600/300 include • 250 or 300 MHz PowerPC™ 604e microprocessor card with built-in FPU • 32 MB of DRAM, expandable to 512 MB using 168-pin, 70 ns, 64-bit EDO* DRAM DIMMs • 1 MB of Inline Cache • 2 MB VRAM, expandable -

PET and the IEEE488

E M : C,r * « M II p^PET and the IEEE 488 Bus (GPIB) Eugene Fisher -C.W.Jensen PET and the IEEE 488 Bus (GPIB) Eugene Fisher - C.W. Jensen OSBORNE/McGraw-Hill Berkeley, California Published by OSBORNE/McGraw-Hill 630 Bancroft Way Berkeley, California 94710 U.S.A For information on translations and book distributors outside of the U.S.A., please write OSBORNE/McGraw-Hill. PET AND THE IEEE 488 BUS (GPIB) Copyright ® 1 980 McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without the prior written permission of the publishers, with the exception that the program listings may be entered, stored, and executed in a computer system, but they may not be reproduced for publication. 1234567890 DODO 89876543210 ISBN 0-931988-31-4 Cartoons by Bruce Mishkin. In recognition of their understanding and support in this project, we dedicate this work to our families — the Fishers and the Jensens — for in a large sense, it's a family affair. Melissa, Christine and Randy Fisher Mary Belle, Tom, Carl, Reg, and Edna Jensen Thank you all Gene Bill Contents Preface 1. Layman's Introduction to the GPIB 1 Development of the IEEE Std 488 Bus 5 Evolution of Digital Interface Systems 5 Perspectives for Interface Design 6 2. GPIB Lines and Signals 9 The Bus Structure 10 Control Lines 12 Data Bus Lines 16 Data Transfer 16 The Handshake Procedure 20 How the Handshake Procedure Works — A Simplified Version 20 Handshake Sequence for the PET as a Controller/Talker 22 Handshake Sequence for the PET as a Controller/Listener 25 Accessing the GPIB from PET I/O Memory 28 Data Lines 28 Control Lines 30 viii Contents 3. -

The Hardware Book by Joakim Ögren

The Hardware Book by Joakim Ögren Visit Cable City at <http://www.cablecity.com> Welcome to the Hardware Book. Your electronic reference guide. Created and maintained by Joakim Ögren. This is the PDF (Adobe Acrobat) version. It's converted from HTML to PDF so the result may sometimes look a bit strange. Please let me know if you find any major visual errors. You will find the online version and the latest PDF version at HwB <http://www.blackdown.org/~hwb/hwb.html>. Current version 1.3 BETA. Converted from HTML 1997-11-23. Contents: Connectors Pinouts for connectors, buses etc. Connectors Top 10 Too many? These are the most common. Cables How to build serial cables and many other cables. Adapters How to build adapters. Circuits Misc circuits (active filters etc). Misc Misc information (encyclopaedia). Tables Misc tables with info. (AWG..) Download Download a WinHelp or HTML version for offline viewing. HwB-News Subscribe to the HwB Newsletter! Info about updates etc. Wanted Information I am currently looking for. About Who did this? And why? Comment Send your comments to the author. Note: This PDF file may NOT be sold in printed form. (C) Joakim Ögren 1996,1997 The Hardware Book is freely distributable but copyrighted to Joakim Ögren. It may not be modified and re-distributed without the authors permission. PRELIMINARY BETA. NOT FOR REDISTRIBUTION. BETA RELEASE Chapter 1 Connector Menu What does the information that is listed for each connector mean? See the tutorial. Buses: - ISA - (Technical) - EISA - (Technical) - PCI - (Technical) - VESA LocalBus (VLB) - (Technical) - CompactPCI - (Technical) - IndustrialPCI - SmallPCI - Miniature Card - (Technical) - NuBus - NuBus 90 - Zorro II - Zorro II/III - CPU-port (A1200) - Ramex (A1000) - Video Expansion (Amiga) - CD32 Expansion - CardBus - PC Card - PC Card ATA - PCMCIA - CompactFlash - C-bus II - SSFDC - PC-104 - Unibus Serial In/Out: The Hardware Book is freely distributable but copyrighted to Joakim Ögren. -

Lecture16-Bus Interfacing

CMPE - 310 Lecture 16 – Bus Interfacing Source: computerhope.com, https://www.computerhope.com/cdn/bigmb.jpg Adapted from slides prepared by Dr. Chintan Patel for CMPE 310 2 Source: computerhope.com, https://www.computerhope.com/cdn/bigmb.jpg Adapted from slides prepared by Dr. Chintan Patel for CMPE 310 3 Bus Interfaces Different types of buses: O ISA (Industry Standard Architecture) O EISA (Extended ISA) O VESA (Video Electronics Standards Association, VL Bus) O PCI (Peripheral Component Interconnect) O USB (Universal Serial Bus) O AGP (Advanced Graphics Port) ISA is the oldest of all these and today's computers still have a ISA bus interface in form of an ISA slot (connection) on the main board. ISA has 8-bit and 16-bit standards along with the 32-bit version (EISA). All three versions operate at 8MHz. Adapted from slides prepared by Dr. Chintan Patel for CMPE 310 4 8-Bit ISA Bus connector Pin # 1 GND IO CHK 2 RESET 3 +5V 4 IRQ2 5 -5V 6 DRQ2 D0-D7 7 -12V 8 OWS 9 +12V ISA Bus Connector Contains 10 GND IO RDY 11 MEMW AEN 12 MEMR 8- bit Data Bus 13 IOW 14 IOR Demultiplexed 20-bit address Bus 15 DACK3 16 DRQ3 17 DACK1 I/O and Memory Control Signals 18 DRQ1 19 RESET 20 CLOCK Interrupt Request Lines (IRQ2->IRQ7) 21 IRQ7 22 IRQ6 A0-A19 23 IRQ5 DMA channels 1-3 Control Signals 24 IRQ4 25 IRQ3 26 DACK2 Power, RESET and misc. signals 27 T/C 28 ALE 29 +5V 30 OSC 31 GND Source: http://smallformfactors.mil-embedded.com/articles/isa-bus-going-strong-pc104/ Adapted from slides prepared by Dr. -

Commodore Amiga 4000

------ User's Guide A4000 AM/CA (:: Commodore User's Guide A4000 AM/CA • C:::: Commodore Copyright © 1992 by Commodore Electronics Limited. All rights Reserved. This document may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine readable form without prior consent, in writing, from Commodore Electronics Limited. With this document Commodore makes no warranties or representations, either expressed, or implied, with respect to the products described herein. The information presented herein is being supplied on an "AS IS" basis and is expressly subject to change without notice. The entire risk as to the use of this information is assumed by the user. IN NO EVENT WILL COMMODORE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY CLAIM ARISING OUT OF THE INFORMATION PRESENTED HEREIN, EVEN IF IT HAS BEEN ADVISED OF THE POSSIBILITIES OF SUCH DAMAGES. SOME STATES DO NOT ALLOW THE LIMITATION OF IMPLIED WARRANTIES OR DAMAGES, SO THE ABOVE LIMITATIONS MAY NOT APPLY. Commodore, the Commodore logo, CBM, and AUTOCONFIG are trademarks of Commodore Electronics Limited in the United States and other countries. Amiga, AmigaDOS, Kickstart, Workbench and Bridgeboard are trademarks of Commodore-Amiga, Inc. in the United States and other countries. PCIXT, PC/AT, and PS/2 are trademarks of International Business Machines Corp. Hayes is a registered trademark of Hayes Microcomputer Products, Inc. MS-DOS is a registered trademark, and Windows is a trademark, of Microsoft Corp. Centronics is a registered trademark of Centronics Data Computer Corp. Motorola, 68040, and 68EC040 are trademarks of Motorola Inc. -

Barramento PCI

Barramento PCI PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Mon, 29 Apr 2013 11:40:35 UTC Contents Articles Conventional PCI 1 PCI-X 25 PCI Express 29 References Article Sources and Contributors 46 Image Sources, Licenses and Contributors 47 Article Licenses License 48 Conventional PCI 1 Conventional PCI Conventional PCI PCI Local Bus Three 5-volt 32-bit PCI expansion slots on a motherboard (PC bracket on left side) Year created July 1993 Created by Intel Supersedes ISA, EISA, MCA, VLB Superseded by PCI Express (2004) Width in bits 32 or 64 Capacity 133 MB/s (32-bit at 33 MHz--the standard configuration) 266 MB/s (32-bit at 66 MHz or 64-bit at 33 MHz) 533 MB/s (64-bit at 66 MHz) Style Parallel Hotplugging interface Optional Conventional PCI (PCI is an initialism formed from Peripheral Component Interconnect,[1] part of the PCI Local Bus standard and often shortened to just PCI) is a local computer bus for attaching hardware devices in a computer. The PCI bus supports the functions found on a processor bus, but in a standardized format that is independent of any particular processor. Devices connected to the bus appear to the processor to be connected directly to the processor bus, and are assigned addresses in the processor's address space.[2] Attached devices can take either the form of an integrated circuit fitted onto the motherboard itself, called a planar device in the PCI specification, or an expansion card that fits into a slot.