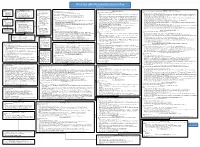

The Intel X86 Microarchitectures Map Version 3.4

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

ECE 574 – Cluster Computing Lecture 21

ECE 574 { Cluster Computing Lecture 21 Vince Weaver http://web.eece.maine.edu/~vweaver [email protected] 22 April 2021 Announcements • Projects (I'll send out presentation order) • Attend Faculty Interviews if you can • Midterms not graded yet • Reminder: no final 1 HW #7 notes • Fine grained parallelism • Running on the Pi-cluster ◦ Test with np=7, some code failed that worked with 2 9d4b6548fa8c6ff66602ef5993aca90f common seems to be not gathering in the extra lines ◦ Reading from each core rather than Bcast doesn't help anything. ◦ Some analysis of pi-cluster results Only scale up to 4. 2 cores load bcast convolve combine gather tail store total 1 1.0 0 12.8 3.8 0.1 0 3.4 21.2 2 1.0 0.1 6.4 1.9 1.8 0 2.4 13.7 4 1.0 0.3 3.2 0.9 3.0 0 2.4 10.9 8 1.0 5.6 1.7 0.5 4.6 0 2.4 15.8 16 1.0 7.3 0.7 0.2 6.5 0 2.4 18.2 32 1.0 8.0 0.3 0.1 6.4 0 2.4 18.3 64 1.0 8.8 0.1 0.06 6.9 0 2.4 19.5 3 HW #8 notes • Be careful memory copying, if copying an array of 9 ints need to copy 36 bytes (not 9) • Also, you can pass in ints as parameters (no need to allocate space and then memcpy in. Or you could, but if you do you would use points and allocate space properly) • Be sure you are using *unsigned char* for the image data, not signed char. -

Introducción a La Microarquitectura Sunny Cove, Ice Lake -10Ma Generación Intel Core

Introducción a la microarquitectura Sunny Cove, Ice Lake -10ma Generación Intel Core En estos días, cuando Computex ha dado el pistoletazo de salida, la buena noticia para los amantes y seguidores del mundo del hardware y del PC, es que la competencia entre Intel y AMD vuelve a estar a niveles similares a los que encontrábamos en los tiempos de la carrera hacia procesadores con frecuencias de 1 GHz. Ahora estamos ya entre los 3 GHz y los 5 GHz, con tecnologías de fabricación de 10 nm y hasta 7 nm en el caso de AMD, que supone hasta 25 veces de mejora frente a los 180 nm de los Pentium 3 de entonces. En estos meses ya se han ido desvelando detalles de las propuestas de Intel y AMD para los meses venideros, con el foco puesto en finales de 2019 y 2020 para hacer valer los respectivos argumentos de cada fabricante para convencer a los usuarios de que elijan una tecnología de procesador, conectividad o gráficos integrados determinada, ya sea de Intel o AMD. Por el momento, AMD es una fuerte competencia para Intel en el mundo del PC de escritorio, mientras que en el apartado de los equipos portátiles Intel sigue teniendo el favor mayoritario de fabricantes y usuarios. La clave está en factores como la optimización en el rendimiento por vatio y el rendimiento en single core, donde Intel sigue siendo mejor que AMD. Al menos de momento con sus arquitecturas Coffe Lake, Whiskey Lake y Amber Lake con tecnología de 14 nm. Con la llegada de Zen 2 de AMD, con tecnología de 7 nm y mejoras en el rendimiento por núcleo, la situación de liderazgo de Intel puede peligrar de aquí a unos meses, cuando AMD desarrolle sus APUs basadas en Zen 2 con gráficos integrados Vega y un TDP de 15W. -

Fact Sheet: Intel Unveils Biggest Architectural Shifts in a Generation

Intel Unveils Biggest Architectural Shifts in a Generation for CPUs, GPUs and IPUs Intel powers the next era of computing for data center, edge and client for the workloads and computing challenges of tomorrow. Aug. 19, 2021 – At Intel’s Architecture Day 2021, Raja Koduri and Intel architects provided details on two new x86 core architectures; Intel’s first performance hybrid architecture, code-named “Alder Lake,” with the intelligent Intel® Thread Director workload scheduler; “Sapphire Rapids,” the next-generation Intel® Xeon® Scalable processor for the data center; new infrastructure processing units; and upcoming graphics architectures, including the Xe HPG and Xe HPC microarchitectures, and Alchemist and Ponte Vecchio SoCs. These new architectures will power upcoming high-performance products and establish the foundations for the next era of Intel innovation aimed at meeting the world’s ever-growing demand for more computing power. Raja Koduri addressed the importance of architectural advancement to meet this demand, saying: “Architecture is alchemy of hardware and software. It blends the best transistors for a given engine, connects them through advanced packaging, integrates high-bandwidth, low-power caches, and equips them with high-capacity, high-bandwidth memories and low-latency scalable interconnects for hybrid computing clusters in a package, while also ensuring that all software accelerates seamlessly. … The breakthroughs we disclosed today demonstrate how architecture will satisfy the crushing demand for more compute performance as workloads from the desktop to the data center become larger, more complex and more diverse than ever.” x86 Cores Efficient-core Intel’s new Efficient-core microarchitecture, previously code-named “Gracemont,” is designed for throughput efficiency, enabling scalable multithreaded performance for modern multitasking. -

The Intel X86 Microarchitectures Map Version 4.1

The Intel x86 Microarchitectures Map Version 4.1 8086 (1978, 3 µm) P5 (1993, 0.80 to 0.35 μm) Willamette (2000, 180 nm) Skylake (2015, 14 nm to 14 nm++) 80386 (1985, 1.5 to 1 µm) P6 (1995, 0.50 to 0.35 μm) Alternative Names: Alternative Names: Pentium, Alternative Names: NetBurst, Pentium 4, Pentium IV, P4, , Pentium 4 180 nm Alternative Names: SKL (Desktop and Mobile), SKX (Server) (The Desktop 9th Generation Core processors have the same security fixes as CSL)(All Alternative Names: iAPX 386, 386, i386 Alternative Names: i686 MCS-86 80586, 586, i586 Series: U and Y processors have on-package PCH) Series: Series: Pentium Pro (used in desktops and servers) Series: Series: • Desktop: Pentium 4 1.x (except those with a suffix), Pentium 4 2.0 Series: • Desktop/Server: i386DX Variant: Klamath (1997, 0.35 μm) • 16-bit data bus: • Desktop/Server: P5, P54C • Desktop lower-performance: Celeron 1.x (where x is a single digit between 5-9, except Celeron 1.6 SL7EZ, • Desktop: Desktop 6th Generation Core i5 (i5-6xxx, S-H, 14 nm) • Desktop lower-performance: i386SX Alternative Names: Pentium II, PII 8086 (iAPX 86) • Desktop/Server higher- Willamette-128), Celeron 2.0 SL68F • Desktop higher-performance: Desktop 6th Generation Core i7 (i7-6xxx, S-H , 14 nm), Desktop 7th Generation Core i7 X (i7-7xxxX, X, 14 nm+), • Mobile: i386SL, 80376, i386EX, Series: Pentium II 233/266/300 steppings C0 and C1 (Klamath, used in desktops) • 8-bit data bus: performance: P54CQS, P54CS • Server: Foster (Xeon), Foster-MP (Xeon) Desktop 7th Generation Core i9 X (i9-7xxxXE, -

Architecture Day 2020 Unveils Willow Cove, Tiger Lake and Xe Architectures, Introduces New Transistor Technology As Intel Advances Its Six Pillars of Innovation

Intel Unpacks Architectural Innovations and Reveals New Transistor Technology at Architecture Day 2020 Architecture Day 2020 Unveils Willow Cove, Tiger Lake and Xe Architectures, Introduces New Transistor Technology as Intel Advances its Six Pillars of Innovation August 13, 2020 – At the Architecture Day 2020 press event, Chief Architect Raja Koduri and Intel fellows and architects provided details on the progress Intel is making on its six pillars of technology innovation strategy. Intel revealed its 10nm SuperFin technology, representing the largest single, intranode enhancement in the company’s history and delivering performance improvement comparable to a full-node transition. The company also unveiled details of its Willow Cove microarchitecture and the Tiger Lake SoC architecture for mobile client and provided a first look at its fully scalable Xe graphics architectures that serve markets ranging from consumer to high-performance computing to gaming usages. Intel’s disaggregated design approach, together with advanced packaging technology, XPU offerings and software-centric strategy, the company is focused on developing leading products across its portfolio to customers. 10nm SuperFin Technology • After years of refining the FinFET transistor, Intel is redefining the technology to enable the largest single intranode enhancement in its history, delivering performance improvement comparable to a full-node transition. 10nm SuperFin technology combines Intel’s enhanced FinFET transistors with Super metal insulator metal capacitor. SuperFin technology offers enhanced epitaxial source/drain, improved gate process and additional gate pitch to enable greater performance by: o Enhancing epitaxial growth of crystal structures on the source and drain, thus increasing strain and reducing resistance to allow more current through the channel. -

Nisu Tuomas.Pdf (6.119Mt)

TUOMAS NISU X86-64 prosessoriarkkitehtuurin lä- himenneisyys ja lähitulevaisuus TIETO- JA VIESTINTÄTEKNIIKAN TUTKINTO-OHJELMA 2016 Tekijä(t) Julkaisun laji Päivämäärä Nisu, Tuomas Opinnäytetyö, AMK toukokuu 2021 Sivumäärä Julkaisun kieli 106 Suomi Julkaisun nimi X86-64 prosessoriarkkitehtuurin lähimenneisyys ja lähitulevaisuus Tutkinto-ohjelma Tieto- ja viestintätekniikka Tiivistelmä Tämän opinnäytetyön tarkoitus on tutkia x86-64 prosessoriarkkitehtuurin lähimennei- syyttä ja lähitulevaisuutta. Työn alussa annetaan taustatietoa AMD:n ja Intelin prosessoreiden rakenteesta, ja pro- sessorin valmistuksesta lyhyesti. Tämän jälkeen käydään läpi AMD:n ja Intelin proses- soriarkkitehtuuri sukupolvia Zenin julkaisusta eteenpäin ja hieman tulevaisuuteen. Näitä sukupolvia vertaillaan edellisiin, ja työhön on liitetty rakennetta selventäviä kuvia tar- peen mukaan. Lopuksi tehdään yhteenveto muutoksista, joita nämä arkkitehtuurit ovat käyneet läpi, ja mitä muutoksia opinnäytetyössä tehdyn selvityksen perusteella voidaan tulevaisuudessa odottaa prosessorien kehityksessä. Asiasanat Mikroprosessorit, arkkitehtuuri, vertailu, kehitys Author(s) Type of Publication Date Nisu, Tuomas Bachelor’s thesis May 2021 ThesisAMKNumber of pages Language of publication: 106 Finnish Title of publication The recent past and near future of X86-64 processor architecture Degree program Information- and communication Technologies Abstract The purpose of this thesis is to examine the recent past and near future of x86-64 proces- sor architecture. At the beginning of this -

Daily Chip Clips

EQUITY RESEARCH INDUSTRY UPDATE August 23, 2021 Daily Chip Clips SUMMARY TECHNOLOGY/SEMICONDUCTORS & COMPONENTS ■ IT Industry Outlook (5): TSMC Under the Microscope (Digitimes) ■ Global Light Vehicle Production Impacts Now Expected Well into 2022 (Digitimes) ■ Intel Brings Chiplets to Data Center CPUs (EE Times) ■ Intel Architecture Day 2021: Alder Lake, Golden Cove, and Gracemont Detailed (AnandTech) ■ Tesla Packs 50 Billion Transistors Onto D1 Dojo Chip Designed to Conquer Artificial Intelligence Training (Tom's Hardware) KEY POINTS ■ Many ask if TSMC is a Taiwanese company. If you look at the equity structure, about three-fourths of the foundry house's shares are in the hands of foreign investors, so TSMC is not a Taiwanese company in this sense. And TSMC's customers are 62% American, 17% from China, and local customers in Taiwan account for only about 11%, so TSMC is a company that relies heavily on overseas customers. ■ Unlike foundries' capacity constraints, which affect mainly automotive MCUs, assembly capacity constraints impact all semiconductor types, including sensors, power supplies, and discretes. This is according to IHS in a recent report. Assembly and test locations are concentrated in China, South Korea, Japan, Singapore, Philippines, Indonesia, Thailand, Vietnam, and Malaysia. ■ Intel Corp.’s fourth-generation Xeon processor, codenamed Sapphire Rapids, consists of four chiplets. The company revealed this at its Architecture Day event. This marks the first time Intel has integrated chiplets into its Xeon data center CPU line, having added the technology to its Stratix 10 FPGA line last year. ■ Last week Intel held its annual Architecture Day event for select press and partners. -

Intel's Core 2 Family

Intel’s Core 2 family - TOCK lines Sunny Cove Dezső Sima Vers. 1.0 Januar 2019 Contents (1) • 1. Introduction • 2. The Core 2 line • 3. The Nehalem line • 4. The Sandy Bridge line • 5. The Haswell line • 6. The Skylake line • 7. The Kaby Lake line • 8. The Kaby Lake Refresh line • 9. The Coffee Lake line • 10. The Coffee Lake line Refresh Contents (2) • 11. The Cannon Lake line (outlook) • 12. Sunny Cove • 13. References 12. Sunny Cove • 12.1 Introduction to the Sunny Cove • 12.2 Major enhancements of the Sunny Cove 12.1 Introduction to the Sunny Cove 12.1 Introduction to the Sunny Cove (1) 12.1 Introduction to the Sunny Cove [296] • Announced in 12/2018 at Intel’s Architecture Day, to be launched in 2019. • Manufactured on Intel’s 10 nm technology. • Presumably, the Sunny Cove cores paired with Gen11 graphics will yield the Ice Lake processor. • Sunny Cove cores offer increased single-threaded performance, new instructions, and ‘improved scalability 12.1 Introduction to the Sunny Cove (2) Intel’s CPU roadmap 2019 – 2022 [297] 12.1 Introduction to the Sunny Cove (3) Evolution of Intel’s manufacturing technology [296] Intel Core Microarchitecture Roadmap Core Name Year Process Node Improvements Single Threaded Performance Skylake 2015 14 nm Lower Power Other Optimizations Kaby Lake 2016 14 nm+ Frequency Coffee Lake 2017 14 nm++ Frequency Coffee Refresh 2018 14 nm++ Frequency Single Threaded Performance Sunny Cove 2019 10 nm New Instructions Improved Scalability Cache Redesign Willow Cove 2020 ? 10 nm ? New Transistor Optimization Security Features Single Threaded Performance AI Performance Golden Cove 2021 ? 7 / 10 nm ? Networking / 5G Performance Security Features 12.1 Introduction1. -

The Intel X86 Microarchitectures Map Version 3.3

The Intel x86 Microarchitectures Map Version 3.3 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P6 (1995, 0.50 to 0.35 μm) Skylake (2015, 14 nm to 14 nm++?) NetBurst (2000 , 180 to 130 nm) Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: i686 Alternative Names: SKL (Desktop and Mobile), SKX (Server) (Note : all U and Y processors are MCPs) P5 (1993, 0.80 to 0.35 μm) Alternative Names: Pentium 4, Pentium IV, P4 • 16-bit data bus: Series: Series: Pentium Pro (used in desktops and servers) Series: Alternative Names: Pentium, Series: 8086 (iAPX 86) • Desktop/Server: i386DX Variant: Klamath (1997, 0.35 μm) • Desktop: Desktop 6th Generation Core i5 (i5-6xxx, S-H) 80586, 586, i586 • Desktop: Pentium 4 1.x (except those with a suffix, Willamette, 180 nm), Pentium 4 2.0 (Willamette, 180 • 8-bit data bus: • Desktop lower-performance: i386SX Alternative Names: Pentium II, PII • Desktop higher-performance: Desktop 6th Generation Core i7 (i7-6xxx, S-H), Desktop 7th Generation Core i7 X (i7-7xxxX, X), Desktop 7th Series: nm) 8088 (iAPX 88) • Mobile: i386SL, 80376, i386EX, Series: Pentium II 233/266/300 steppings C0 and C1 (Klamath, used in desktops) Generation Core i9 X (i7-7xxxXE, i7-7xxxX, X), Desktop 9th Generation Core i7 X (i7-9xxxX, X, 14 nm++?), Desktop 9th Generation Core i9 X • Desktop/Server: P5, P54C • Desktop higher-performance: Pentium 4 1.xA (Northwood, 130 nm), Pentium 4 2.x (except 2.0, 2.40A, i386CXSA, i386SXSA, i386CXSB New instructions: Deschutes (1998, 0.25 to 0.18 μm) (i7-9xxxXE, i7-9xxxX, X, 14 nm++?), Xeon W-3175X -

Cpus, Gpus and Accelerators X86 Intel Roadmap for 2019

CPUs, GPUs and accelerators x86 Intel roadmap for 2019- ● Intel focusing on new spaces - IoT, AI, DL, self-driving cars, … where AMD cannot yet compete ● 3D chip stacking ○ Enabled by Foveros interconnect technology ● FPGA ● Intel Nervana AI Processor NNP-L-1000 (H2 2019-) ○ Accelerates AI inference for companies with high workload demands ○ Optimized across memory, bandwidth, utilization and power ○ Spring Crest 3-4x faster training than Lake Crest, introduced in 2017 ○ Supports bfloat16 Intel server micro-architectures (1/2) Microarchitecture Technology Launch year Highlights Skylake 14nm 2015 Improved frontend and execution units More load/store bandwidth Improved hyperthreading AVX-512 Cascade Lake 14nm++ 2019 Vector Neural Network Instructions (VNNI) to improve inference performance Support 3D XPoint-based memory modules and Optane DC Security mitigations Cooper Lake 14nm++ 2020 bfloat16 (brain floating point format) Source: Anandtech Intel server micro-architectures (2/2) Microarchitecture Technology Launch Highlights CPU codename year Sunny Cove 10nm+ 2019 Single threaded performance Ice Lake Scalable New instructions Tiger Lake? Improved scalability Larger L1, L2, μop caches and 2nd level TLB More execution ports AVX-512 Willow Cove 10nm 2020? Cache redesign ? New transistor optimization Security Features Golden Cove 7/10nm? 2021? Single threaded performance ? AI Performance Networking/5G Performance Security Features Other Intel-related news ● Record Q3 2018 results ○ Data-centric revenue rose 22% ○ PC revenue rose 16% ● Could -

If You Know Someone Who Would Benefit from Being an Insider, Feel Free to Forward This PDF to Them So They Can Sign up Here

(December 17th, 2018) If you know someone who would benefit from being an Insider, feel free to forward this PDF to them so they can sign up here. Note: As an Insider, you can read all prior Insider newsletters here. Quick Tips for our Insider friends! Hey Insiders, As we’re winding down for the year, we’d like to wish you all a very happy holiday season, whatever and however much you celebrate it! All of our 2019 in-person classes have discounts (ranging from $100-200) for registering in 2018 – you’ve got two weeks left to save money; do you have budget to use or lose? See below for details! We also have a new two-day class on Power BI, Power BI Report Server, and SSRS, with a registration discount available until 1/15/19 – see here for details! Note: the next newsletter will be on the 14th or 15th of January. SQLskills News Live, ONLINE classes: we’ve announced six online classes running in the first quarter of 2019! It’s the perfect way to keep learning, keep your systems moving forward, and stay motivated! And our format is receiving rave reviews: each class is held over three, slightly- longer-than-half days with a combination of lecture/demo and open Q&A. It’s where you can really get your questions answered! Our online course line-up is as follows and now includes a new class on columnstore indexes taught by Jonathan: IEQS: Solving Common Performance Problems with Query Store o January 15-17 IEPUM2017: Planning and Implementing an Upgrade/Migration to SQL Server 2017 o January 29-31 IEQUERY: Fixing Slow Queries, Inefficient Code, and Caching/Statistics Problems o February 12-14 IETLB: Transactions, Locking, Blocking, Isolation, and Versioning o February 26-28 IEVLT: Very Large Tables: Optimizing Performance and Availability through Partitioning o March 12-14 IECS: Columnstore Indexes o March 26-28 ** NEW ** These classes will be delivered live from 10am-3pm PST, Tuesday-Thursday for three consecutive days.