ALD (Atomic Layer Deposition) Separates Reactive Precursors in Time (Or Space), and Grows Materials One “Atomic” Layer at a Time

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Atomic Layer Deposition of High-K Insulators on Epitaxial Graphene: a Review

applied sciences Review Atomic Layer Deposition of High-k Insulators on Epitaxial Graphene: A Review Filippo Giannazzo 1,* , Emanuela Schilirò 1,*, Raffaella Lo Nigro 1, Fabrizio Roccaforte 1 and Rositsa Yakimova 2 1 CNR-IMM, Strada VIII, 5 95121 Catania, Italy; raff[email protected] (R.L.N.); [email protected] (F.R.) 2 Department of Physics Chemistry and Biology, Linköping University, SE-58183 Linköping, Sweden; [email protected] * Correspondence: fi[email protected] (F.G.); [email protected] (E.S.) Received: 7 March 2020; Accepted: 27 March 2020; Published: 3 April 2020 Featured Application: Graphene-based electronics and sensing. Abstract: Due to its excellent physical properties and availability directly on a semiconductor substrate, epitaxial graphene (EG) grown on the (0001) face of hexagonal silicon carbide is a material of choice for advanced applications in electronics, metrology and sensing. The deposition of ultrathin high-k insulators on its surface is a key requirement for the fabrication of EG-based devices, and, in this context, atomic layer deposition (ALD) is the most suitable candidate to achieve uniform coating with nanometric thickness control. This paper presents an overview of the research on ALD of high-k insulators on EG, with a special emphasis on the role played by the peculiar electrical/structural properties of the EG/SiC (0001) interface in the nucleation step of the ALD process. The direct deposition of Al2O3 thin films on the pristine EG surface will be first discussed, demonstrating the critical role of monolayer EG uniformity to achieve a homogeneous Al2O3 coverage. -

Integrated Sustainability Analysis of Atomic Layer Deposition for Microelectronics Manufacturing

Integrated Sustainability Analysis of Atomic Layer Deposition for Microelectronics Manufacturing Chris Y. Yuan Atomic layer deposition (ALD) is a promising nanotechnology for wide applications in e-mail: [email protected] microelectronics manufacturing due to its ability to control layer growth at atomic scale. Sustainability of ALD technology needs to be quantitatively investigated in this early David A. Dornfeld development stage to improve its economic and environmental performance. In this pa- e-mail: [email protected] per, we present an integrated sustainability analysis of ALD technology through material and energy flow analyses. The study is performed on the ALD of Al2O3 high- dielectric Department of Mechanical Engineering, film through trimethylaluminum and water binary reactions. The precursor utilizations, University of California, Berkeley, methane emissions, and nanowaste generations from the ALD process are all quantita- 5100A Etcheverry Hall, tively studied. Energy flow analysis demonstrates that the ALD process energy consump- Berkeley, CA 94720-1740 tion is mainly determined by the ALD cycle time rather than the process temperature. Scale-up performance of the ALD technology is also studied for both emission genera- tions and energy consumptions. Strategies and methods for improving the sustainability performance of the ALD technology are suggested based on the analysis. ͓DOI: 10.1115/1.4001686͔ Keywords: atomic layer deposition, sustainable manufacturing, material flow analysis, energy flow analysis, Al2O3 dielectric film 1 Introduction as the oxidant. Deposition mechanism of Al2O3 by ALD is based ͑ ͒ ͑ ͒ on the chemical vapor deposition CVD reaction: 2Al CH3 3 As the miniaturization trend continues in the semiconductor → manufacturing industry, atomic layer deposition ͑ALD͒ has re- +3H2O Al2O3 +6CH4. -

High-Temperature Atomic Layer Deposition of Gan on 1D Nanostructures

nanomaterials Article High-Temperature Atomic Layer Deposition of GaN on 1D Nanostructures Aaron J. Austin 1 , Elena Echeverria 1 , Phadindra Wagle 1, Punya Mainali 1 , Derek Meyers 1, Ashish Kumar Gupta 2 , Ritesh Sachan 2 , S. Prassana 1,3 and David N. McIlroy 1,* 1 Department of Physics, Oklahoma State University, Stillwater, OK 74078-3072, USA; [email protected] (A.J.A.); [email protected] (E.E.); [email protected] (P.W.); [email protected] (P.M.); [email protected] (D.M.); [email protected] (S.P.) 2 School of Mechanical and Aerospace Engineering, Oklahoma State University, Stillwater, OK 74074-3072, USA; [email protected] (A.K.G.); [email protected] (R.S.) 3 Center for Surface Science, Department of Physics, PSG College of Technology, Coimbatore 641004, India * Correspondence: [email protected] Received: 13 November 2020; Accepted: 2 December 2020; Published: 5 December 2020 Abstract: Silica nanosprings (NS) were coated with gallium nitride (GaN) by high-temperature atomic layer deposition. The deposition temperature was 800 ◦C using trimethylgallium (TMG) as the Ga source and ammonia (NH3) as the reactive nitrogen source. The growth of GaN on silica nanosprings was compared with deposition of GaN thin films to elucidate the growth properties. The effects of buffer layers of aluminum nitride (AlN) and aluminum oxide (Al2O3) on the stoichiometry, chemical bonding, and morphology of GaN thin films were determined with X-ray photoelectron spectroscopy (XPS), high-resolution x-ray diffraction (HRXRD), and atomic force microscopy (AFM). Scanning and transmission electron microscopy of coated silica nanosprings were compared with corresponding data for the GaN thin films. -

Atomic Layer Deposition on Phase-Shift Lithography Generated Photoresist Patterns ARTICLE for 1D Nanochannel Fabrication

Atomic Layer Deposition on Phase-Shift Lithography Generated Photoresist Patterns ARTICLE for 1D Nanochannel Fabrication Firat Gu¨der,*,† Yang Yang,*,† Michael Kru¨ger,‡ Gregory B. Stevens,‡ and Margit Zacharias† Nanotechnology Group, Institute of Microsystems Engineering (IMTEK), Albert-Ludwigs-University Freiburg, Georges-Ko¨hler-Allee 103, 79110 Freiburg, Germany, and Freiburger Materialforschungszentrum, Stefan-Meier-Strae 21, 79104 Freiburg, Germany ABSTRACT A versatile, low-cost, and flexible approach is presented for the fabrication of millimeter-long, sub-100 nm wide 1D nanochannels with tunable wall properties (wall thickness and material) over wafer-scale areas on glass, alumina, and silicon surfaces. This approach includes three fabrication steps. First, sub-100 nm photoresist line patterns were generated by near-field contact phase- shift lithography (NFC-PSL) using an inexpensive homemade borosilicate mask (NFC-PSM). Second, various metal oxides were directly coated on the resist patterns with low-temperature atomic layer deposition (ALD). Finally, the remaining photoresist was removed via an acetone dip, and then planar nanochannel arrays were formed on the substrate. In contrast to all the previous fabrication routes, the sub-100 nm photoresist line patterns produced by NFC-PSL are directly employed as a sacrificial layer for the creation of nanochannels. Because both the NFC-PSL and the ALD deposition are highly reproducible processes, the strategy proposed here can be regarded as a general route for nanochannel fabrication in a simplified and reliable manner. In addition, the fabricated nanochannels were used as templates to synthesize various organic and inorganic 1D nanostructures on the substrate surface. KEYWORDS: ALD • near-field contact phase-shift lithography • nanochannel • nanotemplating • nanowire 1. -

Atomic Layer Deposition (ALD): from Precursors to Thin Film Structures

Thin Solid Films 409 (2002) 138–146 Review Atomic layer deposition (ALD): from precursors to thin film structures Markku Leskela*,¨ Mikko Ritala Department of Chemistry, P.O. Box 55, FIN-00014, University of Helsinki, Finland Abstract The principles of the atomic layer deposition (ALD) method are presented emphasizing the importance of precursor and surface chemistry. With a proper adjustment of the experimental conditions, i.e. temperatures and pulsing times, the growth proceeds via saturative steps. Selected recent ALD processes developed for films used in microelectronics are described as examples. These include deposition of oxide films for dielectrics, and nitride and metal films for metallizations. The use of a plasma source to form radicals is expanding the selection of ALD films to metals. Plasma-enhanced ALD also facilitates the deposition of nitride films at low temperatures. ᮊ 2002 Elsevier Science B.V. All rights reserved. Keywords: Atomic layer deposition (ALD); Atomic layer epitaxy (ALE); Thin films 1. Introduction II–VI compounds gained much interest w7–9x, but no real breakthrough was achieved in this area due to the The ALD method relies on alternate pulsing of the complicated surface chemistry. Since the mid 1990s, precursor gases and vapors onto the substrate surface rapidly increasing interest towards ALD has originated and subsequent chemisorption or surface reaction of the from the silicon based microelectronics. This increase is precursors w1x. The reactor is purged with an inert gas a consequence of the ever decreasing device dimensions between the precursor pulses. With a proper adjustment and increasing aspect ratios in integrated circuits (IC). of the experimental conditions the process proceeds via In addition, the required thickness of the films has, in saturative steps. -

Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices

University of Kentucky UKnowledge Theses and Dissertations--Electrical and Computer Engineering Electrical and Computer Engineering 2015 Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices Lei Han University of Kentucky, [email protected] Right click to open a feedback form in a new tab to let us know how this document benefits ou.y Recommended Citation Han, Lei, "Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices" (2015). Theses and Dissertations--Electrical and Computer Engineering. 69. https://uknowledge.uky.edu/ece_etds/69 This Doctoral Dissertation is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact [email protected]. STUDENT AGREEMENT: I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File. I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. -

Atomic Layer Deposition Applications in Nanotechnology Alexandra Burke Taylor University

Taylor University Pillars at Taylor University Chemistry Student Scholarship Chemistry and Biochemistry Spring 2019 Atomic Layer Deposition Applications in Nanotechnology Alexandra Burke Taylor University Follow this and additional works at: https://pillars.taylor.edu/chemistry-student Part of the Chemistry Commons, and the Higher Education Commons Recommended Citation Burke, Alexandra, "Atomic Layer Deposition Applications in Nanotechnology" (2019). Chemistry Student Scholarship. 3. https://pillars.taylor.edu/chemistry-student/3 This Thesis is brought to you for free and open access by the Chemistry and Biochemistry at Pillars at Taylor University. It has been accepted for inclusion in Chemistry Student Scholarship by an authorized administrator of Pillars at Taylor University. For more information, please contact [email protected]. Atomic Layer Deposition Applications in Nanotechnology Senior Thesis Literature Review – CHE420 Ally Burke Chapter 1: Introduction to Atomic Layer Deposition Atomic Layer Deposition (ALD) is a thin film technique used to create controlled-depth layers of atoms on various surfaces.1 The phrase “thin film” in the context of Atomic Layer Deposition refers to a thin layer of atoms that has been deposited on a target surface. This process is completed through a series of sequential half reactions, each reaction depositing a layer of atoms on the intended surface. These layers can be as thin as 1 atom or can be thicker depending on the cycle, and the contents of the layers can be specifically tailored depending on the system in question. This allows for a high degree of control in layer thickness and layer content. As technologies are becoming increasingly smaller, it has become necessary to create a technique which can create the thin layers required by these devices.2,3 Nanotechnology as the name implies has reached sizes of nano-scale proportions. -

Atomic Layer Deposition of Advanced Gate Oxides for Scaled MOSFET

2011 Master Thesis Atomic layer deposition of advanced gate oxides for scaled MOSFET Supervisor Professor Hiroshi Iwai Iwai Laboratory Department of Electronics and Applied Physics Tokyo Institute of Technology 09M36081 Kenji Ozawa -1 - LIST OF CONTENT Index………………………………………………………………………..1 Chapter 1 INTRODUCTION………………………………………………………..4 1.1 Background of This Study…………………………………………………..5 1.2 Scaling Method of MOSFETS……………………………………………...6 1.3 Scaling Limits of SiO2 Gate Dielectric……………………………………..8 1.4 Requirements of High-k Materials………………………………………...11 1.5 Properties of La2O3………………………………………………………...13 1.6 Requirements of Atomic Layer Deposition………………………………..15 1.7 Purpose of This Study……………………………………………………..16 Chapter 2 FBRICATION AND CHARACTERIZATION METHOD………….17 2.1 Experimental Procedure 2.1.1 Fabrication Method MOS Capacitor…………………………………...18 2.1.2 Wet Cleaning Method of Si Substrate.…………………………………19 2.1.3 Atomic Layer Deposition Method……………………………………...21 2.1.4 RF sputtering…………………………………………………………...23 2.1.5 Photolithography……………………………………………………….24 2.1.6 Reactive Ion Etching…………………………………………………...26 2.1.7 Rapid Thermal Annealing (RTA)………………………………………27 2.1.8 Vacuum Thermal Evaporation method………………………………...28 2.2 Measurement Methods 2.2.1 Atomic Force Microscopy……………………………………………...29 -2 - 2.2.2 C-V (Capacitance-Voltage) Measurement……………………………30 2.2.3 J-V (Leakage Current Density-Voltage) Measurement……………….32 Chapter 3 GROWTH CHARACTERISTICS OF ALD………………………….33 3.1 Self-limiting Growth Condition 3.1.1 La2O3.......................................................................................................34 -

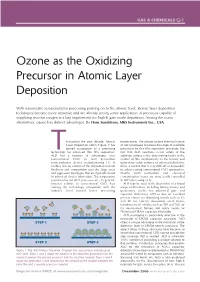

Ozone As the Oxidizing Precursor in Atomic Layer Deposition

p1-4 MKS Supp v3 8/2/06 3:22 pm Page 1 GAS & CHEMICALS G1 Ozone as the Oxidizing Precursor in Atomic Layer Deposition With nanometric semiconductor processing pushing on to the atomic level, atomic layer deposition techniques become more attractive and are already seeing some application. A precursor capable of supplying reactive oxygen is a key requirement for high-K gate oxide deposition. Among the many alternatives, ozone has distinct advantages. By Hans Sundstrom, MKS Instruments Inc., USA. hroughout the past decade, Atomic temperatures. The unique surface chemical nature Layer Deposition (ALD) (Figure 1) has of ALD processes broadens the range of available gained acceptance as a promising precursors for thin film deposition processes. The Ttechnology for advanced thin film deposition. fact that ALD reactions occur solely at the ALD has a number of advantages over substrate surface is the determining factor in the conventional CVD in next generation control of film stoichiometry in the ternary and semiconductor device manufacturing [1]. It quaternary oxide systems of advanced dielectric enables precise control of the deposited material films, a control that is very difficult or impossible thickness and composition over the large areas to achieve using conventional CVD approaches. and aggressive topologies that are typically found Finally, both particulate and chemical in advanced device fabrication. The temperature contamination issues are more easily controlled requirements for ALD processes are, in general, in ALD processing [2,3]. lowered relative to conventional CVD, thus ALD may be used in the deposition of a broad making the technology compatible with the scope of thin films, including binary, ternary and industry trend toward lower processing quaternary oxides for advanced gate and capacitor dielectrics. -

Development of Nanostructures by Atomic and Molecular Layer Deposition

Western University Scholarship@Western Electronic Thesis and Dissertation Repository 4-18-2018 2:30 PM Development of Nanostructures by Atomic and Molecular Layer Deposition Andrew P. Lushington The University of Western Ontario Supervisor Sun, Xueliang The University of Western Ontario Graduate Program in Mechanical and Materials Engineering A thesis submitted in partial fulfillment of the equirr ements for the degree in Doctor of Philosophy © Andrew P. Lushington 2018 Follow this and additional works at: https://ir.lib.uwo.ca/etd Part of the Other Materials Science and Engineering Commons Recommended Citation Lushington, Andrew P., "Development of Nanostructures by Atomic and Molecular Layer Deposition" (2018). Electronic Thesis and Dissertation Repository. 5354. https://ir.lib.uwo.ca/etd/5354 This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact [email protected]. Abstract Atomic layer deposition (ALD) is a thin film deposition technique that has a rich history of being an enabling technique. This vapor phase deposition process can produce a variety of thin films and nanostructures. ALD is based on sequential, self-limiting reactions and provides angstrom level control over film growth. Furthermore, ALD allows for conformal deposition on high-aspect ratio structures and can provide tunable film composition. As nanotechnology marches forward, the development of nanomaterials has significantly advanced. Additional functionality can be imparted to nanomaterials by using surface modification techniques. Given the advantages of ALD, this technique has become a powerful tool for modifying the surface of materials and increasing the functionality and application of nanomaterials. -

Atomic Layer Deposition of Aluminum (111) Thin Film by Dimethylethylaminealane

1 Atomic layer deposition of aluminum (111) thin film by dimethylethylaminealane precursor Sameh Okasha*a&b , Yoshiaki Sekinec, Satoshi Sasakic, and Yuichi Haradaa a Global Innovation Center, Kyushu University, 6-1 Kasuga-Koen, Kasuga, Fukuoka 816-8580, Japan b Molecular and material science department, Interdisciplinary Graduate School of Engineering Sciences, Kyushu University, Kasuga, Fukuoka 816-8580, Japan c NTT Basic Research Laboratories, NTT Corporation, 3-1 Morinosato Wakamiya, Atsugi, Kanagawa 243-0198, Japan Abstract: We report the growth of aluminum (111) thin film by atomic layer deposition (ALD) technique with dimethylethylaminealane (DMEAA) as a precursor. It is found that the metallic underlayer is essential to grow uniform aluminum films by DMEAA precursor. As a titanium thin film is used as the underlayer, grown aluminum thin film shows (111) orientation irrespective of substrates. The lattice constant and superconducting transition temperature of the aluminum thin films are the same as the bulk one. These findings suggest that ALD technique provides high quality of the aluminum thin films and have potential for the applications of superconducting devices. We discuss ALD technique with DMEAA precursor is the promising method for fabricating vertical small Josephson tunnel junctions, which can be used as the superconducting quantum bits. * Corresponding author: [email protected] 2 Keywords: aluminum (111) thin film, atomic layer deposition, dimethylethylaminealane, selective growth, superconducting thin film 1. INTRODUCTION Atomic layer deposition (ALD) technique enables us to fabricate atomically controlled thin films [1]. ALD technique can deposit insulating materials conformally which can cover the whole surface of nanowires [2] and realize quantum point contact made of a narrow In0.75 Ga0.25 As channel [3]. -

Planar Gaas Nanowire Tri-Gate Mosfets by Vaporâ

Solid-State Electronics 93 (2014) 40–42 Contents lists available at ScienceDirect Solid-State Electronics journal homepage: www.elsevier.com/locate/sse Planar GaAs nanowire tri-gate MOSFETs by vapor–liquid–solid growth ⇑ Chen Zhang, Xiuling Li Department of Electrical and Computer Engineering, Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Urbana, IL 61801, USA article info abstract Article history: Depletion-mode metal–oxide–semiconductor field effect transistors (MOSFETs) with GaAs planar nano- Received 23 October 2013 wire (NW) channels are successfully demonstrated. The Si-doped planar GaAs NWs are grown in a selec- Received in revised form 2 December 2013 tive lateral epitaxy manner via Au-assisted vapor–liquid–solid (VLS) mechanism. A SiO2 interlayer Accepted 9 December 2013 between the multi-faceted NW and Al O high-k dielectric formed by atomic layer deposition (ALD) Available online 3 January 2014 2 3 improves the NW MOSFET performance. The review of this paper was arranged by Ó 2013 Elsevier Ltd. All rights reserved. Prof. E. Calleja Keywords: Metalorganic chemical vapor deposition (MOCVD) Metal–oxide–semiconductor field effect transistor (MOSFET) Nanowire 1. Introduction on Si-doped n-type planar GaAs NWs using Al2O3 as the gate oxide. For III–V multi-gate transistors, simultaneous passivation of differ- III–V semiconductor nanowires (NWs) have received much ent crystal facets could be challenging since interface trap density attention recently due to their high intrinsic electron mobility has strong crystal orientation dependence [7]. We here use SiO2 and the inherent 3-dimensional geometry which facilitates the deposited by plasma-enhanced chemical vapor deposition (PECVD) realization of multi-gate transistors [1].