Technical Manual COMMODORE AMIGA

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Amigaos 3.2 FAQ 47.1 (09.04.2021) English

$VER: AmigaOS 3.2 FAQ 47.1 (09.04.2021) English Please note: This file contains a list of frequently asked questions along with answers, sorted by topics. Before trying to contact support, please read through this FAQ to determine whether or not it answers your question(s). Whilst this FAQ is focused on AmigaOS 3.2, it contains information regarding previous AmigaOS versions. Index of topics covered in this FAQ: 1. Installation 1.1 * What are the minimum hardware requirements for AmigaOS 3.2? 1.2 * Why won't AmigaOS 3.2 boot with 512 KB of RAM? 1.3 * Ok, I get it; 512 KB is not enough anymore, but can I get my way with less than 2 MB of RAM? 1.4 * How can I verify whether I correctly installed AmigaOS 3.2? 1.5 * Do you have any tips that can help me with 3.2 using my current hardware and software combination? 1.6 * The Help subsystem fails, it seems it is not available anymore. What happened? 1.7 * What are GlowIcons? Should I choose to install them? 1.8 * How can I verify the integrity of my AmigaOS 3.2 CD-ROM? 1.9 * My Greek/Russian/Polish/Turkish fonts are not being properly displayed. How can I fix this? 1.10 * When I boot from my AmigaOS 3.2 CD-ROM, I am being welcomed to the "AmigaOS Preinstallation Environment". What does this mean? 1.11 * What is the optimal ADF images/floppy disk ordering for a full AmigaOS 3.2 installation? 1.12 * LoadModule fails for some unknown reason when trying to update my ROM modules. -

A History of the Amiga by Jeremy Reimer

A history of the Amiga By Jeremy Reimer 1 part 1: Genesis 3 part 2: The birth of Amiga 13 part 3: The first prototype 19 part 4: Enter Commodore 27 part 5: Postlaunch blues 39 part 6: Stopping the bleeding 48 part 7: Game on! 60 Shadow of the 16-bit Beast 71 2 A history of the Amiga, part 1: Genesis By Jeremy Reimer Prologue: the last day April 24, 1994 The flag was flying at half-mast when Dave Haynie drove up to the headquarters of Commodore International for what would be the last time. Dave had worked for Commodore at its West Chester, Pennsylvania, headquarters for eleven years as a hardware engineer. His job was to work on advanced products, like the revolutionary AAA chipset that would have again made the Amiga computer the fastest and most powerful multimedia machine available. But AAA, like most of the projects underway at Commodore, had been canceled in a series of cost-cutting measures, the most recent of which had reduced the staff of over one thousand people at the factory to less than thirty. "Bringing your camera on the last day, eh Dave?" the receptionist asked in a resigned voice."Yeah, well, they can't yell at me for spreading secrets any more, can they?" he replied. Dave took his camera on a tour of the factory, his low voice echoing through the empty hallways. "I just thought about it this morning," he said, referring to his idea to film the last moments of the company for which he had given so much of his life. -

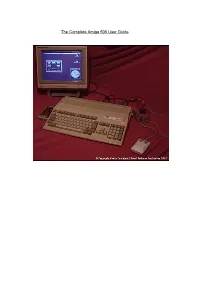

The Complete Amiga 500+ User Guide

The Complete Amiga 500+ User Guide By Peter Hutchison 8 2016 Revised: 23/10/2016 Contents Introduction Page 3 Setting up the Amiga for First Time Page 4 Guide to Workbench 2.04 Page 6 Menus Page 6 Mouse Page 8 Programs Page 9 Preferences Page 13 Workbench 2.1 Page 19 Beyond Workbench 2.x Page 19 Adding more Memory to the A500+ Page 20 Adding a CD or DVD ROM drive to the A500+ Page 20 Upgrading the Processor Page 21 Upgrading the Kickstart and Workbench Page 22 The Motherboard in details Page 23 Backward Compatibility Page 24 Adding a Hard Disk to A500+ Page 25 Installing Workbench onto a Hard Disk Page 27 2 Introduction Welcome to the Commodore Amiga A500+. The first replacement of the A500 Amiga. It was affordable and easy to use. It had a wide range of software, in particular, games which Jay Minor, the creator of the Amiga, had designed it for. The Amiga A500+ is based on the Motorola 68000 7.14MHz Processor with 1MbRAM, a single 880K floppy drive with support for three more floppy drives and a Custom Chipset that provides the Sound and Graphics. The new A500 Plus now supports the new Kickstart 2.0 and Workbench 2.0 upgrade from Kickstart/Workbench 1.3 and the new Enhanced Chipset (ESC) with up to 2MB of Chip RAM supported, and new high resolutions support for Productivity modes (640 x 470), Super HiRes (1280 x 200/256) and interlace modes. The Blitter can also now copy regions bigger than 1024x10124 pixels in one operation. -

Amigaone-XE G4 We Preview the Fastest Powerpc Motherboard in Eyetech’S Range

Issue 16, Autumn 2003 £4.00 8.00Euro Find out all about this feature-packed Zorro card inside. AmigaOne-XE G4 We preview the fastest PowerPC motherboard in Eyetech’s range. Improve your digital photos and scans with our image enhancement tutorial. Contents News PageStream Issue 16 EditorialChandler’s Amiga OS 4 Update for Amiga OS 4 Autumn 2003 elcome to another on page 10. This time he Grasshopper LLC has display. Hopefully this feature Wbumper 52-page edition reports some interesting announced that they will may be added to the new of Total Amiga! As I write this developments relating to support AmigaOS 4 with a new Amiga version too. The Contents the production of this issue has developing programs for OS 4 version of their professional standard retail price of the full gone very smoothly and it and some changes in priority DTP package, PageStream 4. version of PageStream has looks like it will be out on time. that should mean the As regular readers will know, been reduced to just $99 News This has largely been made AmigaOne version is available Editorial ..............................2 PageStream is a powerful (approximately £65) making it possible by all the people who earlier than would otherwise finding software currently in program and, I think most much more affordable. There is News Items ........................3 contributed to this issue, as have been possible. This development so we thought it people will agree, one of best also a new professional edition Amiga OS 4 Update........ 10 you will see there are several should please Mick and would be worth reviewing. -

Amigaguide NO

#amigaguide NO. 1 - 2008 - ISSUE 4 - News - Interview - Amiga at NASA • Computer in your car? : info Contents 1 Front cover page: Darkness these dark times? «There are a lot of Amiga freaks When the day is over, it is getting colder. in the Croatian Republic» It is getting darker, the sun is setting and With the sound of Ravels Bolero playing 3 ReadMeFirst - Editorial all the creeps of the night gains power of in your ears, your increasing fear fills the the realm of the darkness. Evil forces air like fog over a dark forest, and you 4 Disk.info - News wins terrain, and the hollow wind bears start to escape towards the only rescue 7 Cars and Computers news about a near future filled with that you can see: A cross standing in the - Erlend writes about why you should despair and coldness. hillside. It is not promising you anything, install a computer in your car... the only reason you run towards it, is that The ages of the good times are gone, left the cross is shining and white, in 10 Amiga at NASA are we with the sorrow and fears worrying complete opposite to the surrounding - Article about use of the Amiga at NASA our minds about what to eat, where to darkness of the night. The thought of 13 Trashcan sleep and where our heads shall find nearing this cross of light fills your heart rest. with promises of peace and love and 14 Interview: Edvision protection from the abandoned ship - Who are Edvision? Interview tells.. -

Workbench 16 Pgs.PGS

Workbench May 2008 Issue 250 May 2008 Workbench 1 Editorial A Big Hello to all Amigans out there. I see all sorts of strange and wonderful things are occurring in Editor the AMIGA world, mostly in our favour. Thank heaven! Barry Woodfield Phone:9917 2967 The latest version of AmigaSYS has been released at last. (Check out Mobile : 0448 915 283 page 4) It looks like being very good. Hope to get it up and running at the [email protected] ibutions next meeting. (With Michael’s help, that is ;-) Come and see how it turns out. Contributions can be soft copy (on floppy½ disk) or hard copy. It will be returned if requested and accompanied with a self- Hope to see some of you guys there. Until then. addressed envelope. The editor of the Amiga Users Group Inc. newsletter Ciao for now, Workbench retains the right to edit contributions for Barry R. Woodfield. clarity and length. Send contributions to: Amiga Users Group P.O. Box 2097 Seaford Victoria 3198 OR [email protected] rtising Advertising space is free for members to sell private items or services. For information on commercial rates, contact: Tony Mulvihill 0415 161 2721 [email protected] Deadlines Last Months Meeting Workbench is published each month. The deadline for each April 20th 2008 issue is the 1st Tuesday of Another good gather with a new the month of publication. Reprints member joining up and a bit of work All articles in Workbench are Copyright 2008 the being done by Michael, configuring Amiga Users Group Inc. -

Apov Issue 4 Regulars

issue 4 - june 2010 - an abime.net publication the amiga dedicated to amIga poInt of vIew AMIGA reviews w news tips w charts apov issue 4 regulars 8 editorial 10 news 14 who are we? 116 charts 117 letters 119 the back page reviews 16 leander 18 dragon's breath 22 star trek: 25th anniversary 26 operation wolf 28 cabal 30 cavitas 32 pinball fantasies 36 akira 38 the king of chicago ap o 40 wwf wrestlemania v 4 42 pd games 44 round up 5 features 50 in your face The first person shooter may not be the first genre that comes to mind when you think of the Amiga, but it's seen plenty of them. Read about every last one in gory detail. “A superimposed map is very useful to give an overview of the levels.” 68 emulation station There are literally thousands of games for the Amiga. Not enough for you? Then fire up an emulator and choose from games for loads of other systems. Wise guy. “More control options than you could shake a joypad at and a large number of memory mappers.” 78 sensi and sensibility Best football game for the Amiga? We'd say so. Read our guide to the myriad versions of Sensi. “The Beckhams had long lived in their estate, in the opulence which their eminence afforded them.” wham into the eagles nest 103 If you're going to storm a castle full of Nazis you're going to need a plan. colorado 110 Up a creek without a paddle? Read these tips and it'll be smooth sailing. -

Advanced 68000 CPU Accelerator for Amiga Computers

Advanced 68000 CPU Accelerator for Amiga Computers Owners Manual Table of Contents Introduction......................................................................................1 How It Works.....................................................................................1 AdSpeed Configuration.....................................................................2 Optional Speed Switch......................................................................2 Installation........................................................................................3 Opening an Amiga 500..................................................................3 Opening an Amiga 1000................................................................3 Opening an Amiga 2000................................................................5 Installing AdSpeed.........................................................................5 The AdSpeed Program.......................................................................6 Programming Information................................................................7 Compatibility....................................................................................8 Other Amiga Products from ICD.......................................................8 AdRAM 540..................................................................................8 AdRAM 560D...............................................................................9 AdRAM 2080................................................................................9 -

The Complete Amiga 500 User Guide the Complete Amiga 500 User Guide

The Complete Amiga 500 User Guide The Complete Amiga 500 User Guide by Peter Hutchison (2003) Introduction Page 2 Setting up the Amiga for First Time Page 3 Guide to Workbench 1.3 Page 5 Guide to Amiga DOS commands Page 18 Amiga BASIC Command List Page 30 Beyond Workbench 1.3 Page 35 Adding a Hard Disk to A500 Page 36 Installing Workbench onto a Hard Disk Page 36 Adding more Memory to the A500 Page 37 Upgrading the Processor Page 38 Upgrading the Kickstart and Workbench Page 29 Backward Compatibility Page 40 2 Introduction Welcome to the Commodore Amiga A500, one of the most popular Amiga models of its time. It was affordable, easy to use and good software in particular games which Jay Minor, the creator of the Amiga, had designed it for. The Amiga A500 is based on the Motorola 68000 7MHz Processor with 512K (or more) RAM, a single 880K floppy drive with support for 3 more floppy drives, a Custom Chipset that provides the Sound and Graphics. The Amiga runs the Operating System called AmigaOS which consists of the Kickstart ROM which contains some essential libraries and devices needed to load Workbench which is the desktop: Figure 1 You can a while menu bar at the top and all the disks mounted on the right hand of the screen. The Ram Disk is a special one which is a disk in memory basically. More on Workbench will be explained later. 3 Setting up the Amiga for First Time Before setting up the Amiga make sure you have the following items ready: Amiga A500 Monitor or TV Set Mouse Power Supply Joystick (optional) Speakers (optional) External Disk drives (optional) Withe Amiga facing you, first plug the square end of the Power Supply cable to the Power socket on the top left hand at the back of the Amiga. -

Komputer Amiga Współcześnie Spis Treści

Amiga.org.pl komputer Amiga współcześnie Spis treści AMIGA legenda informatyki 2 Retro 4 Emulacja 6 Współczesna Amiga nowej generacji 12 MorphOS 18 AROS 25 Amiga dzisiaj Zainteresowanie komputerem Amiga jest nieprzemijające. Niezależnie od tych, którzy mają Amigę “od zawsze”, biegnie współcześnie jej nieprzerwany rozwój, i to wielotorowo. Oprócz tego możemy cieszyć się różnymi hobbystycznymi rozwinięciami, pozwalającymi w sposób bardziej wygodny korzystać z rozrywki w formie retro. Amiga dzisiaj to “amigowanie”, wielka różnorodność i wiele smaków 1 Amiga retro AMIGA legenda informatyki AMIGA - pierwszy na świecie komputer multimedialny. Premiera w 1985 r. Wcześniej były inne innowacyjne konstrukcje (np. firmy Xerox czy Lisa firmy Apple) ale to Amiga wnosiła fenomenalną na ówczesne czasy grafikę, animację i dźwięk. Architektura komputera to specjalizowane układy odciążające procesor. artyści Andy Warhole i Debby Harry przy pierwszej Amidze Rewelacją był też wielozadaniowy system operacyjny. Prasa branżowa potraktowała wtedy Amigę jako zabawkę, nie wiadomo było co z tym robić. Ten pierwszy model nazywał się po prostu Amiga, potem nazywano go Amiga 1000. Projekt wraz z zespołem który go stworzył, z genialnym Jayem Minerem na czele, trafił pod skrzydła CBM (Commodore Business Machines), giganta w tamtym okresie jeśli chodzi o produkcję komputerów na świecie. Kolejne modele pojawiły się 2 lata później – dopiero one odniosły sukces. Amiga 2000 i Amiga 500, oparte na podobnych podzespołach, okienkowy graficzny interfejs – Workbench jednocześnie rozdzieliły pierwotną koncepcję na dwie linie komputerów – “duże” i “małe” Amigi. 2 Amiga retro “Duże” Amigi przypominały PC, były to desktopy, umożliwiające rozbudowę za pomocą kart rozszerzeń. Za sprawą rozszerzenia Video Toaster stały się na jakiś czas standardem w edycji wideo. -

ACA500 Short Manual CF Card Interface and Accelerator for the Amiga 500 Or 500+

ACA500 short manual CF card interface and accelerator for the Amiga 500 or 500+ Dear customer, thank you for purchasing a product from Individual Computers. We're sure that your new accelerator will satisfy all your needs. The ACA500 is easy to install and simply plugs into the side expansion slot of your Amiga and can be used right away. Package contents, unpacking In addition to this manual, you will find the accelerator in a plastic bag in the box and an instructional sticker on the inside of the box. The card comes with jumpers set for normal operation. The ACA500 is delicate equipment, please handle it with extreme caution. If something is not clear after reading this manual, please get help from a technician. If you have further questions, don't hesitate to ask your reseller! Preparing the computer Remove any expansion that you may have installed on the side-connector (=Zorro connector) of your A500. Also, any accelerator that is installed inside of your A500 must be removed. If you've just taken an Amiga 500 out of storage to be used for the first time with the ACA500, you may want to check that the Amiga is in good condition and works properly before installing the ACA500. Refer to on-line Amiga resources for common problems and fixes such as battery leaks and re-seating the custom chips. Installation The card is for the Zorro slot on the left side of your Amiga. Please turn your Amiga off, then refer to the picture on the inside of the box showing how to insert it. -

Download Issue 11

Issue 11, Summer 2002 £4.00 8.00Euro Also in this issue: News OS 4 Update AmigaOne News Reviews Charon News Coaster Cordless Mouse Tutorials Scala MM400 PerfectPaint DOpus 5 Three x86 Amiga Emulators Reviewed Plus... PageStream 4.1MIDI on the Amiga Amiga Writer Contents Contents Issue 11 Editorial Amiga One and their plans for Summer 2002 elcome to another issue future versions. We also know Wof Total Amiga. This issue the developers are hard at work is really packed, not only are we readying MorphOS and the Alt.WoA Show Report back to 48 pages thanks to a bit Pegasos for release but they’re since WoA ‘99 we had Amigas systems up and running with Down on the main show floor more advertising but we also keeping pretty quiet about it so fter last year’s successful running on the SEAL stand as TV cards and other interesting many of the UK’s key Amiga Contents have more pages of tutorials maybe we’ll see something on 2002 Alt. WoA show (which was opposed to our machines being add-ons. Once again Matt dealers were represented. than ever before. In fact things that front soon too. A the first in the North of England used in the games arena. Mick Morris and the Blackpool Eyetech had the biggest stand got so tight that we had to drop News Another interesting development for a long time) SEAL were ran Freespace on his A1200 Amiga Group came up trumps and seemed to be doing good our regular Top Tips and PD Alt.WoA Show Report ...