SW-VHDL Co-Verification Environment Using Open Source

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Federation Toolflow

Federation: Open Source SoC Design Methodology Jack Koenig, Staff Engineer Aug 3, 2019 Hardware Trends: Compute Needs are Changing e.g., machine learning But, CPUs are not getting faster! Source: Medium, Entering the world of Machine Learning 2 Hardware Trends: Custom Hardware to the Rescue! Custom Chips But, custom chip development GPUs (e.g., Google TPU) costs are too high! 3 How did turn into a $1B acquisition with only 13 employees?* 4 * https://www.sigarch.org/open-source-hardware-stone-soups-and-not-stone-statues-please Why do silicon projects need experts from at least 14+ disciplines just to get started? 6 <Your Name Here> Tech Stack Tech Stack Readily-Available Reusable Technology from techstacks.io Federation Tools Infrastructure Cloud Services 7 We Should Copy “Innovations” from the Software Industry open-source standards abstraction and code reuse composability and APIs productivity tooling commodity infrastructure 8 npm Enables Modular Web Development with Reusable Packages 9 Source: https://go.tiny.cloud/blog/a-guide-to-npm-the-node-js-package-manager/ npm Enables Javascript as Most Popular Programming Language • 830.000 of packages • 10 million users • 30 billion packages downloads per month • 90% of Web built of NPM packages • NPM used everywhere: client, server, mobile, IoT • Open source libraries availability is the major driving force for Language adoption [Leo2013] proven by NPM • 70+ programming languages can be transpiled into JS, WebAssembly and published on NPM 10 Federation: the action of forming states or organizations into a single group with centralized control, within which smaller divisions have some degree of internal autonomy 11 Federation: a suite of open-source tools that SiFive is using to orchestrate modular SoC design workflows 12 Federation Tools Enable a Modular SoC Design Methodology Federation Tools IP Package 1 IP Package 2 IP Package 3 1. -

Co-Simulation Between Cλash and Traditional Hdls

MASTER THESIS CO-SIMULATION BETWEEN CλASH AND TRADITIONAL HDLS Author: John Verheij Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Architecture for Embedded Systems (CAES) Exam committee: Dr. Ir. C.P.R. Baaij Dr. Ir. J. Kuper Dr. Ir. J.F. Broenink Ir. E. Molenkamp August 19, 2016 Abstract CλaSH is a functional hardware description language (HDL) developed at the CAES group of the University of Twente. CλaSH borrows both the syntax and semantics from the general-purpose functional programming language Haskell, meaning that circuit de- signers can define their circuits with regular Haskell syntax. CλaSH contains a compiler for compiling circuits to traditional hardware description languages, like VHDL, Verilog, and SystemVerilog. Currently, compiling to traditional HDLs is one-way, meaning that CλaSH has no simulation options with the traditional HDLs. Co-simulation could be used to simulate designs which are defined in multiple lan- guages. With co-simulation it should be possible to use CλaSH as a verification language (test-bench) for traditional HDLs. Furthermore, circuits defined in traditional HDLs, can be used and simulated within CλaSH. In this thesis, research is done on the co-simulation of CλaSH and traditional HDLs. Traditional hardware description languages are standardized and include an interface to communicate with foreign languages. This interface can be used to include foreign func- tions, or to make verification and co-simulation possible. Because CλaSH also has possibilities to communicate with foreign languages, through Haskell foreign function interface (FFI), it is possible to set up co-simulation. The Verilog Procedural Interface (VPI), as defined in the IEEE 1364 standard, is used to set-up the communication and to control a Verilog simulator. -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Pyvsc: Systemverilog-Style Constraints and Coverage in Python

PyVSC: SystemVerilog-Style Constraints, and Coverage in Python M. Ballance Milwaukie, OR, USA [email protected] Abstract—Constrained-randomization and functional Coverage is captured as a set of individual coverpoint coverage are key elements in the widely-used SystemVerilog-based instances, and is not organized into covergroup types and verification flow. The use of Python in functional verification is instances in the same way that SystemVerilog does. growing in popularity, but Python has historically lacked support for the constraint and coverage features provided by B. SystemC SystemVerilog. This paper describes PyVSC, a library that SystemC has been one of the longer-lasting languages used provides these features. for modeling and verifying hardware that is built as an embedded domain-specific language within a general-purpose Keywords—functional verification, Python, constrained programming language (C++). While libraries for constraints random, functional coverage and coverage targeting SystemC are not directly applicable in I. INTRODUCTION Python, it’s worthwhile considering approaches taken. Verification flows based on constrained-random stimulus The SystemC Verification Library (SCV) provides basic generation and functional coverage collection have become randomizations and constraints, using a Binary Decision dominant where SystemVerilog is used for the testbench Diagram (BDD) solver. BDD-based constraint solvers are environment. Consequently, verification engineers have known to have performance and capacity challenges, especially significant experience with the constructs and patterns provided with sizable constraint spaces. No support for capturing by SystemVerilog. functional coverage is provided. There is growing interest in making use of Python in The CRAVE [4] library sought to bring higher performance verification environments – either as a complete verification and capacity to randomization in SystemC using Satifiability environment or as an adjunct to a SystemVerilog verification Modulo Theories (SMT) constraint solvers. -

PGAS Communication for Heterogeneous Clusters with Fpgas

PGAS Communication for Heterogeneous Clusters with FPGAs by Varun Sharma A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto © Copyright 2020 by Varun Sharma Abstract PGAS Communication for Heterogeneous Clusters with FPGAs Varun Sharma Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto 2020 This work presents a heterogeneous communication library for generic clusters of processors and FPGAs. This library, Shoal, supports the partitioned global address space (PGAS) memory model for applications. PGAS is a shared memory model for clusters that creates a distinction between local and remote memory accesses. Through Shoal and its common application programming interface for hardware and software, applications can be more freely migrated to the optimal platform and deployed onto dynamic cluster topologies. The library is tested using a thorough suite of microbenchmarks to establish latency and throughput performance. We also show an implementation of the Jacobi method that demonstrates the ease with which applications can be moved between platforms to yield faster run times. ii Acknowledgements It takes a village to raise a child and about as many people to raise a thesis as well. Foremost, I would like to thank my supervisor, Paul Chow, for all that he’s done for me over the course of the four years that I’ve known him thus far. Thank you for accepting me as your student for my undergraduate thesis and not immediately rejecting me when I asked to pursue a Masters under your supervision as well. -

Hardware Architecture

Hardware Architecture Components Computing Infrastructure Components Servers Clients LAN & WLAN Internet Connectivity Computation Software Storage Backup Integration is the Key ! Security Data Network Management Computer Today’s Computer Computer Model: Von Neumann Architecture Computer Model Input: keyboard, mouse, scanner, punch cards Processing: CPU executes the computer program Output: monitor, printer, fax machine Storage: hard drive, optical media, diskettes, magnetic tape Von Neumann architecture - Wiki Article (15 min YouTube Video) Components Computer Components Components Computer Components CPU Memory Hard Disk Mother Board CD/DVD Drives Adaptors Power Supply Display Keyboard Mouse Network Interface I/O ports CPU CPU CPU – Central Processing Unit (Microprocessor) consists of three parts: Control Unit • Execute programs/instructions: the machine language • Move data from one memory location to another • Communicate between other parts of a PC Arithmetic Logic Unit • Arithmetic operations: add, subtract, multiply, divide • Logic operations: and, or, xor • Floating point operations: real number manipulation Registers CPU Processor Architecture See How the CPU Works In One Lesson (20 min YouTube Video) CPU CPU CPU speed is influenced by several factors: Chip Manufacturing Technology: nm (2002: 130 nm, 2004: 90nm, 2006: 65 nm, 2008: 45nm, 2010:32nm, Latest is 22nm) Clock speed: Gigahertz (Typical : 2 – 3 GHz, Maximum 5.5 GHz) Front Side Bus: MHz (Typical: 1333MHz , 1666MHz) Word size : 32-bit or 64-bit word sizes Cache: Level 1 (64 KB per core), Level 2 (256 KB per core) caches on die. Now Level 3 (2 MB to 8 MB shared) cache also on die Instruction set size: X86 (CISC), RISC Microarchitecture: CPU Internal Architecture (Ivy Bridge, Haswell) Single Core/Multi Core Multi Threading Hyper Threading vs. -

Linuxvilag-66.Pdf 8791KB 11 2012-05-28 10:27:18

Magazin Hírek Java telefon másképp Huszonegyedik századi autótolvajok Samsung okostelefon Linuxszal Magyarországon még nem jellemzõ, Kínában már kapható de tõlünk nyugatabbra már nem tol- a Samsung SCH-i819 mo- vajkulccsal vagy feszítõvassal, hanem biltelefonja, amely Prizm laptoppal járnak az autótolvajok. 2.5-ös Linuxot futtat. Ot- Mindezt azt teszi lehetõvé, hogy tani nyaralás esetén nyu- a gyújtás, a riasztó és az ajtózárak is godtan vásárolhatunk távirányíthatóak, így egy megfelelõen belõle, hiszen a CDMA felszerelt laptoppal is irányíthatóak 800 MHz-e mellett az ezek a rendszerek. európai 900/1800 MHz-et http://www.leftlanenews.com/2006/ is támogatja. A kommunikációt egy 05/03/gone-in-20-minutes-using- Qualcomm MSM6300-as áramkör bo- laptops-to-steal-cars/ nyolítja, míg az alkalmazások egy 416 MHz-es Intel PXA270-es processzoron A Lucent Technologies és a SUN Elephants Dream futnak. A készülék Class 10-es GPRS elkészítette a Jasper S20-at, ami adatátvitelre képes, illetve tartalmaz alapvetõen más koncepcióval GPS (globális helymeghatározó) vevõt © Kiskapu Kft. Minden jog fenntartva használja a Java-t, mint a mostani is. Az eszköz 64 megabájt SDRAM-ot és telefonok. Joggal kérdezheti a kedves 128 megabájt nem felejtõ flash memóri- Olvasó, hogy megéri-e, van-e hely át kapott, de micro-SD memóriakártyá- a jelenlegi Symbian, Windows Mobile val ezt tovább bõvíthetjük. A kijelzõje és Linux trió mellett. A jelenlegi 2.4 hüvelykes, felbontása pedig „csak” telefonoknál kétféleképpen futhat 240x320 képpont 65 ezer színnel. egy program: natív vagy Java mód- Május 19-én elérhetõvé tette az Orange Természetesen a trendeknek megfele- ban. A Java mód ott szükségessé Open Movie Project elsõ rövidfilmjét lõen nem maradt ki a 2 megapixeles tesz pár olyan szintet, amely Creative Commons jogállással. -

Efficient Processing of Deep Neural Networks

Efficient Processing of Deep Neural Networks Vivienne Sze, Yu-Hsin Chen, Tien-Ju Yang, Joel Emer Massachusetts Institute of Technology Reference: V. Sze, Y.-H.Chen, T.-J. Yang, J. S. Emer, ”Efficient Processing of Deep Neural Networks,” Synthesis Lectures on Computer Architecture, Morgan & Claypool Publishers, 2020 For book updates, sign up for mailing list at http://mailman.mit.edu/mailman/listinfo/eems-news June 15, 2020 Abstract This book provides a structured treatment of the key principles and techniques for enabling efficient process- ing of deep neural networks (DNNs). DNNs are currently widely used for many artificial intelligence (AI) applications, including computer vision, speech recognition, and robotics. While DNNs deliver state-of-the- art accuracy on many AI tasks, it comes at the cost of high computational complexity. Therefore, techniques that enable efficient processing of deep neural networks to improve key metrics—such as energy-efficiency, throughput, and latency—without sacrificing accuracy or increasing hardware costs are critical to enabling the wide deployment of DNNs in AI systems. The book includes background on DNN processing; a description and taxonomy of hardware architectural approaches for designing DNN accelerators; key metrics for evaluating and comparing different designs; features of DNN processing that are amenable to hardware/algorithm co-design to improve energy efficiency and throughput; and opportunities for applying new technologies. Readers will find a structured introduction to the field as well as formalization and organization of key concepts from contemporary work that provide insights that may spark new ideas. 1 Contents Preface 9 I Understanding Deep Neural Networks 13 1 Introduction 14 1.1 Background on Deep Neural Networks . -

Lewis University Dr. James Girard Summer Undergraduate Research Program 2021 Faculty Mentor - Project Application

Lewis University Dr. James Girard Summer Undergraduate Research Program 2021 Faculty Mentor - Project Application Exploring the Use of High-level Parallel Abstractions and Parallel Computing for Functional and Gate-Level Simulation Acceleration Dr. Lucien Ngalamou Department of Engineering, Computing and Mathematical Sciences Abstract System-on-Chip (SoC) complexity growth has multiplied non-stop, and time-to- market pressure has driven demand for innovation in simulation performance. Logic simulation is the primary method to verify the correctness of such systems. Logic simulation is used heavily to verify the functional correctness of a design for a broad range of abstraction levels. In mainstream industry verification methodologies, typical setups coordinate the validation e↵ort of a complex digital system by distributing logic simulation tasks among vast server farms for months at a time. Yet, the performance of logic simulation is not sufficient to satisfy the demand, leading to incomplete validation processes, escaped functional bugs, and continuous pressure on the EDA1 industry to develop faster simulation solutions. In this research, we will explore a solution that uses high-level parallel abstractions and parallel computing to boost the performance of logic simulation. 1Electronic Design Automation 1 1 Project Description 1.1 Introduction and Background SoC complexity is increasing rapidly, driven by demands in the mobile market, and in- creasingly by the fast-growth of assisted- and autonomous-driving applications. SoC teams utilize many verification technologies to address their complexity and time-to-market chal- lenges; however, logic simulation continues to be the foundation for all verification flows, and continues to account for more than 90% [10] of all verification workloads. -

Comparación Y Análisis De Desempeño De Unidades De Procesamiento Gráfico Como Alternativa De Computación Paralela Para Procesos De Simulación En Ingeniería

Comparación y análisis de desempeño de unidades de procesamiento gráfico como alternativa de computación paralela para procesos de simulación en ingeniería. Yerman Jahir Avila Garzón Universidad Nacional de Colombia Facultad de Ingeniería, Departamento de Ingeniería Eléctrica y Electrónica Bogotá DC, Colombia 2015 Comparación y análisis de desempeño de unidades de procesamiento gráfico como alternativa de computación paralela para procesos de simulación en ingeniería. Yerman Jahir Avila Garzón Tesis presentada como requisito parcial para optar al título de: Magister en Ingeniería – Automatización Industrial Director: Ph.D., M.Sc. Ing. Electricista Johan Sebastián Eslava Garzón Línea de Investigación: Arquitectura de Computadores y Computación Paralela, Electrónica Digital, Optimización Grupo de Investigación: GMUN: Grupo de Microelectrónica Universidad Nacional Universidad Nacional de Colombia Facultad de Ingeniería, Departamento de Ingeniería Eléctrica y Electrónica Bogotá DC, Colombia 2015 El que ama la educación ama el saber; el que odia la educación es un tonto. Proverbios 12, 1 A mi esposa Jazmín y mi pequeño hijo Diego José quien está por nacer. A mis padres Ismael y María Antonia, y a mi hermano Arley. A mis abuelas Erminda y Nohemy. A mis abuelos Parmenio† y Celestino†. Resumen y Abstract VII Resumen La computación de propósito general en las unidades de procesamiento gráfico GPU es una área de en continuo crecimiento. Las arquitecturas actuales de las GPU permiten la optimización, a través de diferentes lenguajes de programación (p. ej. CUDA C, CUDA Fortran, OpenCL, entre otros) aplicaciones existentes o crear nuevas aplicaciones que permitan aprovechar el paralelismo natural de GPU. Se busca mejorar el tiempo de ejecución algoritmos complejos, un mejor uso de los recursos computacionales y mayor acceso a plataformas de computación de alto rendimiento. -

Review of FPD's Languages, Compilers, Interpreters and Tools

ISSN 2394-7314 International Journal of Novel Research in Computer Science and Software Engineering Vol. 3, Issue 1, pp: (140-158), Month: January-April 2016, Available at: www.noveltyjournals.com Review of FPD'S Languages, Compilers, Interpreters and Tools 1Amr Rashed, 2Bedir Yousif, 3Ahmed Shaban Samra 1Higher studies Deanship, Taif university, Taif, Saudi Arabia 2Communication and Electronics Department, Faculty of engineering, Kafrelsheikh University, Egypt 3Communication and Electronics Department, Faculty of engineering, Mansoura University, Egypt Abstract: FPGAs have achieved quick acceptance, spread and growth over the past years because they can be applied to a variety of applications. Some of these applications includes: random logic, bioinformatics, video and image processing, device controllers, communication encoding, modulation, and filtering, limited size systems with RAM blocks, and many more. For example, for video and image processing application it is very difficult and time consuming to use traditional HDL languages, so it’s obligatory to search for other efficient, synthesis tools to implement your design. The question is what is the best comparable language or tool to implement desired application. Also this research is very helpful for language developers to know strength points, weakness points, ease of use and efficiency of each tool or language. This research faced many challenges one of them is that there is no complete reference of all FPGA languages and tools, also available references and guides are few and almost not good. Searching for a simple example to learn some of these tools or languages would be a time consuming. This paper represents a review study or guide of almost all PLD's languages, interpreters and tools that can be used for programming, simulating and synthesizing PLD's for analog, digital & mixed signals and systems supported with simple examples. -

Lastlayer:Towards Hardware and Software Continuous Integration

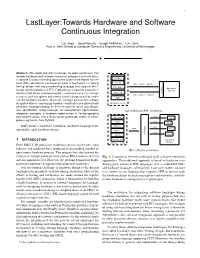

1 LastLayer:Towards Hardware and Software Continuous Integration Luis Vega, Jared Roesch, Joseph McMahan, Luis Ceze. Paul G. Allen School of Computer Science & Engineering, University of Washington F Abstract—This paper presents LastLayer, an open-source tool1 that enables hardware and software continuous integration and simulation. Python Compared to traditional testing approaches based on the register transfer Scala level (RTL) abstraction, LastLayer provides a mechanism for testing RTL input signals Python Verilog designs with any programming language that supports the C RTL DSLs hardware foreign function interface (CFFI). Furthermore, it supports a generic C Scala RTL input signals design Verilog ports interface that allows external programs convenient access to storage RTL DSLs RTL output signals hardware resources such as registers and memories in the design as well as control design VHDL ports over the hardware simulation. Moreover, LastLayer achieves this software Verilog RTL output signals hardware tests integration without requiring any hardware modification and automatically VHDL generates language bindings for these storage resources according to user specification. Using LastLayer, we evaluated two representative hardware tests Python (a) Traditional RTL simulationDPI integration examples: a hardware adder written in Verilog operating reg_a Java DPIDPI over NumPy arrays, and a ReLu vector-accelerator written in Chisel Python reg_amem_a processing tensors from PyTorch. Racket Java DPIDPI CFFI mem_a mem_b Index terms— hardware simulation, hardware language inter- HaskellRacket DPI CFFI DPI mem_b LastLayer reg_b operability, agile hardware design HaskellRust DPI LastLayer reg_b JavaScriptRust hardware design 1 INTRODUCTION softwareJavaScript tests hardware design software tests From RISC-V [9] processors to domain-specific accelerators, both industry and academia have produced an outstanding number of (b) LastLayer simulation open-source hardware projects.