Personal Systems Reference Intel PC Processors - Withdrawn

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Design and Implementation of Pentium-M Based Floswitch for Intracluster Communication Veerappa Chikkagoudar, Dr

Design and Implementation of Pentium-M Based Floswitch for Intracluster Communication Veerappa chikkagoudar, Dr. U. N. Sinha, Prof. B. L. Desai. [email protected], [email protected], [email protected] Department of Electronics and Communication B. V. Bhoomaraddi college of Engg. And Tech. Hubli-580031 Abstract: aero dynamical problems, [1].Since 1986, six Flosolver MK6 is a Parallel processing system, generations of Flosolver machine have evolved based on distributed memory concept and built namely Flosolver MK-1, MK-2, MK-3, MK-4, MK-5 around Pentium-III processors, which acts as and MK-6. processing elements (PEs). Communication Flosolver MK-6 is the latest of the parallel between processing elements is very important, computer based on 128 Pentium III processors which is done through hardware switch called (which act as processing elements, PEs) in 64 dual Floswitch. Floswitch supports both message processor boards each with 1GB RAM and 80 GB passing as well as message processing. Message HDD. It is essentially a distributed memory system. processing is a unique feature of Floswitch. A group of four Dual processor boards with a Floswitch and an optical module is a natural cluster. In existing MK-6 system, communication 16 such clusters form the system. Processing between PEs is done through the Intel 486-based elements (PEs) communicate through Floswitch (a Floswitch, which operates at 32MHz and has 32- communication switch) using PCI-DPM interface bit wide data path. The data transfer rate and card. Clusters communicate through Optical module. floating point computation of existing switch need to be increased. -

Inside Intel® Core™ Microarchitecture Setting New Standards for Energy-Efficient Performance

White Paper Inside Intel® Core™ Microarchitecture Setting New Standards for Energy-Efficient Performance Ofri Wechsler Intel Fellow, Mobility Group Director, Mobility Microprocessor Architecture Intel Corporation White Paper Inside Intel®Core™ Microarchitecture Introduction Introduction 2 The Intel® Core™ microarchitecture is a new foundation for Intel®Core™ Microarchitecture Design Goals 3 Intel® architecture-based desktop, mobile, and mainstream server multi-core processors. This state-of-the-art multi-core optimized Delivering Energy-Efficient Performance 4 and power-efficient microarchitecture is designed to deliver Intel®Core™ Microarchitecture Innovations 5 increased performance and performance-per-watt—thus increasing Intel® Wide Dynamic Execution 6 overall energy efficiency. This new microarchitecture extends the energy efficient philosophy first delivered in Intel's mobile Intel® Intelligent Power Capability 8 microarchitecture found in the Intel® Pentium® M processor, and Intel® Advanced Smart Cache 8 greatly enhances it with many new and leading edge microar- Intel® Smart Memory Access 9 chitectural innovations as well as existing Intel NetBurst® microarchitecture features. What’s more, it incorporates many Intel® Advanced Digital Media Boost 10 new and significant innovations designed to optimize the Intel®Core™ Microarchitecture and Software 11 power, performance, and scalability of multi-core processors. Summary 12 The Intel Core microarchitecture shows Intel’s continued Learn More 12 innovation by delivering both greater energy efficiency Author Biographies 12 and compute capability required for the new workloads and usage models now making their way across computing. With its higher performance and low power, the new Intel Core microarchitecture will be the basis for many new solutions and form factors. In the home, these include higher performing, ultra-quiet, sleek and low-power computer designs, and new advances in more sophisticated, user-friendly entertainment systems. -

Pentium II Processor Performance Brief

PentiumÒ II Processor Performance Brief January 1998 Order Number: 243336-004 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Pentium® II processor may contain design defects or errors known as errata. Current characterized errata are available on request. MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from by calling 1-800-548-4725 or by visiting Intel’s website at http://www.intel.com. -

Fujitsu Siemens Computers

SPEC CINT2006 Result spec Copyright 2006-2014 Standard Performance Evaluation Corporation Fujitsu Siemens Computers SPECint_rate2006 = 21.4 PRIMERGY TX150 S5, Intel Pentium D processor 945, 3.40 GHz SPECint_rate_base2006 = 20.5 CPU2006 license: 22 Test date: May-2007 Test sponsor: Fujitsu Siemens Computers Hardware Availability: Sep-2006 Tested by: Fujitsu Siemens Computers Software Availability: Mar-2007 Copies 0 2.00 4.00 6.00 8.00 10.0 12.0 14.0 16.0 18.0 20.0 22.0 24.0 26.0 28.0 30.0 32.0 34.0 36.0 38.0 40.0 25.5 400.perlbench 2 2 24.1 17.8 401.bzip2 2 2 16.7 22.4 403.gcc 2 22.5 429.mcf 2 2 23.2 19.8 445.gobmk 2 2 18.7 19.5 456.hmmer 2 2 17.1 18.5 458.sjeng 2 2 17.4 19.4 462.libquantum 2 2 18.8 39.9 464.h264ref 2 2 38.3 16.7 471.omnetpp 2 2 15.7 15.5 473.astar 2 2 14.9 28.2 483.xalancbmk 2 SPECint_rate_base2006 = 20.5 SPECint_rate2006 = 21.4 Hardware Software CPU Name: Intel Pentium D 945 Operating System: 64-Bit SUSE LINUX Enterprise Server 10, Kernel CPU Characteristics: 800 MHz system bus 2.6.16.21-0.8-smp on an x86_64 CPU MHz: 3400 Compiler: Intel C++ Compiler for IA32/EM64T application, Version 9.1 - Build 20070215, Package-ID: FPU: Integrated l_cc_p_9.1.047 CPU(s) enabled: 2 cores, 1 chip, 2 cores/chip Auto Parallel: No CPU(s) orderable: 1 chip File System: ReiserFS Primary Cache: 12 K micro-ops I + 16 KB D on chip per core System State: Multiuser, Runlevel 3 Secondary Cache: 2 MB I+D on chip per core Base Pointers: 32-bit L3 Cache: None Peak Pointers: 32/64-bit Other Cache: None Other Software: Smart Heap Library, Version -

Using the Intel® LXT973 Ethernet Transceiver Application Note

Intel® IXP42X Product Line and IXC1100 Control Plane Processor: Using the Intel® LXT973 Ethernet Transceiver Application Note July 2004 Document Number: 253429-002 Intel® IXP42X Product Line and IXC1100 Control Plane Processor: Using the Intel® LXT973 Ethernet Transceiver INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. -

50X50x41mm Socket 7/370 CPU Cooler Fan W/ Heatsink and TX3 and LP4 Startech ID: FANP1003LD

50x50x41mm Socket 7/370 CPU Cooler Fan w/ Heatsink and TX3 and LP4 StarTech ID: FANP1003LD StarTech.com's Socket 7/Socket 730 CPU cooler fan optimizes heat dissipation and removal by combining a large aluminum heatsink and 5cm brushless ball-bearing fan, helping to ensure ideal operating conditions for your hard working CPU. A broadly compatible CPU cooling solution, the Socket 7/Socket 730 CPU cooler fan provides quiet cooling for Socket 370(PPGA) Celerons, Socket 7 Pentiums, AMD K6, K6-2 and Cyrix chips and is powered using a TX3 (3-lead) connection to either the computer power supply or the motherboard (direct). When powered directly from the motherboard, the fan speed and operating status can be monitored for ideal performance. Capable of moving up to 8.84 CFM of air away from the CPU, the Socket 7/Socket 730 CPU cooler fan features a high-efficiency fan blade design and is backed by StarTech.com's 2-year warranty and free lifetime technical support. Applications Socket Type: Socket 7 & Socket 370 VIA : C3, Cyrix III & Cyrix MII up to 500 MHz Intel : Celeron up to 500 MHz AMD : K-6 series up to 500 MHz Replace the stock OEM cooler or a failed Socket 7/370 heatsink fan assembly www.startech.com 1 800 265 1844 Features Aluminum heatsink 50mm ball bearing fan Solid metal retention clip Technical Specifications Warranty 2 Years Fan Bearing Type Ball Bearing Fan Dimensions 50 x 50 x 12.7mm 2 x 2 x 0.5in Heatsink Dimensions 50 x 50 x 22mm 2 x 2 x 0.85in Heatsink Type Aluminum Air Flow Rate 8.84 CFM Fan RPM 4500 Noise Level 28 dBA Connector Type(s) 1 - Molex Fan (3 pin; TX3) Female Color Black Product Height 1.9 in [49 mm] Product Length 1.9 in [49 mm] Product Weight 2.9 oz [81 g] Product Width 1.6 in [40 mm] Input Voltage 12 DC Shipping (Package) Weight 0.3 lb [0.1 kg] Included in Package 1 - Pentium/K6/Celeron 3-Lead CPU Fan Included in Package 1 - 3-pin to dual LP4 Molex Adapter Cable Included in Package 1 - Packet of Thermal Compound Certifications, Reports and Compatibility www.startech.com 1 800 265 1844. -

IBM Thinkpad Notebooks 1992 to 2001 - Withdrawn January 2001 - Version 214 IBM Thinkpad 240 - Withdrawn

IBM PC Institute IBM Personal Systems Reference IBM ThinkPad Notebooks 1992 to 2001 - withdrawn January 2001 - Version 214 IBM ThinkPad 240 - withdrawn IBM ThinkPad Processor Intel Mobile Celeron 300, 366, or 400MHz1 / 66MHz system bus Processor features No upgrade / processor on Ball Grid Array (H-PBGA) L2 cache 128KB / onboard (full speed) / synchronous pipelined burst / ECC / write-back Diskette drive External 3.5" 1.44MB / connects to left side with FDD port / includes case and cable CD-ROM Option: External CD-ROM / via Portable Drive Bay and 24X-10X5 CD-ROM UltraslimBay Drive DVD-ROM Option: External DVD-ROM / via Portable Drive Bay and DVD-ROM UltraslimBay Drive Type-model ✂ 2609-21U ✂ 2609-31U ✂ 2609-41U Processor Celeron 300MHz Celeron 366MHz Celeron 400MHz Disk - size / ms 6.4GB4 / 13ms read / Ultra DMA/33 or PIO Mode 4 12.0GB / 12ms read / ATA-66 or PIO4 Preload (see side) Windows 987 Windows 987 SE Windows 987 SE Avail / withdrawn date June 1999 / February 2000 November 1999 / February 2000 February 2000 / February 2001 Display - size and type 10.4" TFT color (264.16mm) / Active Matrix Display - technology SVGA / 800x600 / 15ms refresh (typical) / 50 to 110 nits 16.7 million simultaneous colors / 250 to 1 contrast (typical) Graphics - controller NeoMagic MagicMedia128XD (NM2160C) / 128-bit accelerator / DDC2B / 2MB / SGRAM (embedded) / color space conversion Graphics - features Simultaneous LCD and CRT26 / 180 degree tilt / no multiple-monitor support / ext SVGA to 1024x768 with 65,536 colors Memory - std / max 64MB / 192MB33 -

Intel® Server Board S3420GP

Intel® Server Board S3420GP Technical Product Specification Intel order number E65697-010 Revision 2.4 January, 2011 Enterprise Platforms and Services Division - Marketing Revision History Intel® Server Board S3420GP TPS Revision History Date Revision Modifications Number Feb. 2009 0.3 Initial release. May 2009 0.5 Update block diagram. July. 2009 0.9 Updated POST error code and diagram. Aug. 2009 1.0 Updated MTBF. Nov. 2009 1.1 Additional details for memory configuration. Dec. 2009 1.2 Added Intel® Server Board S3420GPV details. Dec. 2009 2.0 Updated processor name. Jan. 2010 2.1 Corrected the typo. Apr. 2010 2.2 Corrected the typo, updated processor name and remove CCC certification marking information. July. 2010 2.3 Corrected the typo. Jan.2011 2.4 Corrected the typo. Added RDIMM support on S3420GPV. Updated Table 45. Add USB device readiness beep code information. ii Revision 2.4 Intel order number E65697-010 Intel® Server Board S3420GP TPS Disclaimers Disclaimers Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. -

Focus on Your Core Competency the COM Express Standard

Computer-On-Modules Focus on your Core Competency The COM Express Standard – A Computer-On-Module (COM) provides a convenient solution for Adaptable to Your Specific Needs OEMs that need computing functionality but are not interested in COM Express was developed and is maintained by PICMG investing the time and resources into designing a single board (PCI Industrial Computer Manufacturers Group). COM computer. There are several COM standards, one of the more Express was released in the summer of 2005 and is the popular being COM Express (also referred to as COM.0). COM most widely used COM standard. The standard defines the Express modules contain the CPU, memory, common peripherals physical size, interconnect, and thermal interface for a COM. (USB, SATA) and an I/O interface (PCI and PCI Express). OEMs that The original COM Express specification was written to use COM Express modules design a carrier board that contains any support peripherals that were available at the time of release required I/O interfaces not found on the COM Express module as – including USB 2.0, SATA, PATA, Ethernet, VGA, LVDS, well as connectors for external I/O. A COM based solution allows SDVO, PCI, and PCI Express Gen 1. Several pinout types an OEM to focus on their core competency and not the design and were defined by PICMG with each one having a specific maintenance of a single board computer. combination of peripherals, expansion interfaces and connector layout. The most widely used COM Express A COM Express based solution with a custom carrier board offers module is a type 2, followed by type 1. -

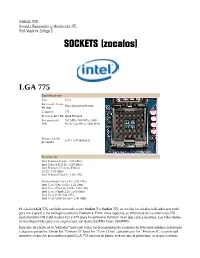

SOCKETS (Zocalos)

Instituto ITES Armado, Reparación y Mantención PC. Prof: Vladimir Zúñiga C. SOCKETS (zocalos) LGA 775 Especificaciones Tipo LGA Factores de forma Flip-chip land grid array del chip Contactos 775 Protocolo del FSB Quad-Pumped Frecuencia del 533 MT/s, 800 MT/s, 1066 FSB MT/s, 1333 MT/s, 1600 MT/s Dimesiones del 1.47 × 1.47 inches[1] procesador Procesadores Intel Pentium 4 (2.66 - 3.80 GHz) Intel Celeron D (2.53 - 3.60 GHz ) Intel Pentium 4 Extreme Edition (3.20 - 3.73 GHz) Intel Pentium D (2.66 - 3.60 GHz) Pentium Dual-Core (1.40 - 2.80 GHz) Intel Core 2 Duo (1.60 - 3.33 GHz) Intel Core 2 Extreme (2.66 - 3.20 GHz) Intel Core 2 Quad (2.33 - 3.00 GHz) Intel Xeon (1.86-3.40 GHz) Intel 'Core' Celeron (1.60 - 2.40 GHz) El zócalo LGA 775, también conocido como Socket T o Socket 775, es uno de los zócalos utilizados por Intel para dar soporte a los microprocesadores Pentium 4. Entre otros aspectos, se diferencia de los anteriores 370 (para Pentium III) y del Socket 423 y 478 (para los primeros Pentium 4) en que carece de pines. Las velocidades de bus disponibles para esta arquitectura van desde 533Mhz hasta 1600MHz. Este tipo de zócalo es el "estándar" para casi todos los procesadores de consumo de Intel para equipos sobremesa y algunos portátiles. Desde los "Celeron D" hasta los "Core 2 Duo", pasando por los "Pentium D", su principal atractivo es que los procesadores para LGA 775 carecen de pines; es decir que la placa base es la que contiene los contactos para comunicarse con el procesador. -

Class-Action Lawsuit

Case 3:20-cv-00863-SI Document 1 Filed 05/29/20 Page 1 of 279 Steve D. Larson, OSB No. 863540 Email: [email protected] Jennifer S. Wagner, OSB No. 024470 Email: [email protected] STOLL STOLL BERNE LOKTING & SHLACHTER P.C. 209 SW Oak Street, Suite 500 Portland, Oregon 97204 Telephone: (503) 227-1600 Attorneys for Plaintiffs [Additional Counsel Listed on Signature Page.] UNITED STATES DISTRICT COURT DISTRICT OF OREGON PORTLAND DIVISION BLUE PEAK HOSTING, LLC, PAMELA Case No. GREEN, TITI RICAFORT, MARGARITE SIMPSON, and MICHAEL NELSON, on behalf of CLASS ACTION ALLEGATION themselves and all others similarly situated, COMPLAINT Plaintiffs, DEMAND FOR JURY TRIAL v. INTEL CORPORATION, a Delaware corporation, Defendant. CLASS ACTION ALLEGATION COMPLAINT Case 3:20-cv-00863-SI Document 1 Filed 05/29/20 Page 2 of 279 Plaintiffs Blue Peak Hosting, LLC, Pamela Green, Titi Ricafort, Margarite Sampson, and Michael Nelson, individually and on behalf of the members of the Class defined below, allege the following against Defendant Intel Corporation (“Intel” or “the Company”), based upon personal knowledge with respect to themselves and on information and belief derived from, among other things, the investigation of counsel and review of public documents as to all other matters. INTRODUCTION 1. Despite Intel’s intentional concealment of specific design choices that it long knew rendered its central processing units (“CPUs” or “processors”) unsecure, it was only in January 2018 that it was first revealed to the public that Intel’s CPUs have significant security vulnerabilities that gave unauthorized program instructions access to protected data. 2. A CPU is the “brain” in every computer and mobile device and processes all of the essential applications, including the handling of confidential information such as passwords and encryption keys. -

System Management BIOS (SMBIOS) Reference 6 Specification

1 2 Document Number: DSP0134 3 Date: 2011-01-26 4 Version: 2.7.1 5 System Management BIOS (SMBIOS) Reference 6 Specification 7 Document Type: Specification 8 Document Status: DMTF Standard 9 Document Language: en-US 10 System Management BIOS (SMBIOS) Reference Specification DSP0134 11 Copyright Notice 12 Copyright © 2000, 2002, 2004–2011 Distributed Management Task Force, Inc. (DMTF). All rights 13 reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 23 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 24 disclose, or identify any such third party patent rights, or for such party’s reliance on the standard or 25 incorporation