An Initial Implementation of a Direct Digital Synthesizer Module for Radar Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Developments 70'S

Digital Developments 70’s - 80’s Hybrid Synthesis “GROOVE” • In 1967, Max Mathews and Richard Moore at Bell Labs began to develop Groove (Generated Realtime Operations on Voltage- Controlled Equipment) • In 1970, the Groove system was unveiled at a “Music and Technology” conference in Stockholm. • Groove was a hybrid system which used a Honeywell DDP224 computer to store manual actions (such as twisting knobs, playing a keyboard, etc.) These actions were stored and used to control analog synthesis components in realtime. • Composers Emmanuel Gent and Laurie Spiegel worked with GROOVE Details of GROOVE GROOVE System included: - 2 large disk storage units - a tape drive - an interface for the analog devices (12 8-bit and 2 12-bit converters) - A cathode ray display unit to show the composer a visual representation of the control instructions - Large array of analog components including 12 voltage-controlled oscillators, seven voltage-controlled amplifiers, and two voltage-controlled filters Programming language used: FORTRAN Benefits of the GROOVE System: - 1st digitally controlled realtime system - Musical parameters could be controlled over time (not note-oriented) - Was used to control images too: In 1974, Spiegel used the GROOVE system to implement the program VAMPIRE (Video and Music Program for Interactive, Realtime Exploration) • Laurie Spiegel at the GROOVE Console at Bell Labs (mid 70s) The 1st Digital Synthesizer “The Synclavier” • In 1972, composer Jon Appleton, the Founder and Director of the Bregman Electronic Music Studio at Dartmouth wanted to find a way to control a Moog synthesizer with a computer • He raised this idea to Sydney Alonso, a professor of Engineering at Dartmouth and Cameron Jones, a student in music and computer science at Dartmouth. -

Tracking of High-Speed, Non-Smooth and Microscale-Amplitude Wave Trajectories

Tracking of High-speed, Non-smooth and Microscale-amplitude Wave Trajectories Jiradech Kongthon Department of Mechatronics Engineering, Assumption University, Suvarnabhumi Campus, Samuthprakarn, Thailand Keywords: High-speed Tracking, Inversion-based Control, Microscale Positioning, Reduced-order Inverse, Tracking. Abstract: In this article, an inversion-based control approach is proposed and presented for tracking desired trajectories with high-speed (100Hz), non-smooth (triangle and sawtooth waves), and microscale-amplitude (10 micron) wave forms. The interesting challenge is that the tracking involves the trajectories that possess a high frequency, a microscale amplitude, sharp turnarounds at the corners. Two different types of wave trajectories, which are triangle and sawtooth waves, are investigated. The model, or the transfer function of a piezoactuator is obtained experimentally from the frequency response by using a dynamic signal analyzer. Under the inversion-based control scheme and the model obtained, the tracking is simulated in MATLAB. The main contributions of this work are to show that (1) the model and the controller achieve a good tracking performance measured by the root mean square error (RMSE) and the maximum error (Emax), (2) the maximum error occurs at the sharp corner of the trajectories, (3) tracking the sawtooth wave yields larger RMSE and Emax values,compared to tracking the triangle wave, and (4) in terms of robustness to modeling error or unmodeled dynamics, Emax is still less than 10% of the peak to peak amplitude of 20 micron if the increases in the natural frequency and the damping ratio are less than 5% for the triangle trajectory and Emax is still less than 10% of the peak to peak amplitude of 20 micron if the increases in the natural frequency and the damping ratio are less than 3.2 % for the sawtooth trajectory. -

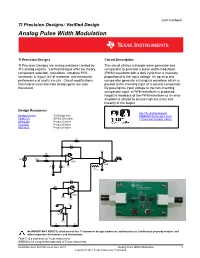

Verified Design Analog Pulse Width Modulation

John Caldwell TI Precision Designs: Verified Design Analog Pulse Width Modulation TI Precision Designs Circuit Description TI Precision Designs are analog solutions created by This circuit utilizes a triangle wave generator and TI’s analog experts. Verified Designs offer the theory, comparator to generate a pulse-width-modulated component selection, simulation, complete PCB (PWM) waveform with a duty cycle that is inversely schematic & layout, bill of materials, and measured proportional to the input voltage. An op amp and performance of useful circuits. Circuit modifications comparator generate a triangular waveform which is that help to meet alternate design goals are also passed to the inverting input of a second comparator. discussed. By passing the input voltage to the non-inverting comparator input, a PWM waveform is produced. Negative feedback of the PWM waveform to an error amplifier is utilized to ensure high accuracy and linearity of the output Design Resources Ask The Analog Experts Design Archive All Design files WEBENCH® Design Center TINA-TI™ SPICE Simulator TI Precision Designs Library OPA2365 Product Folder TLV3502 Product Folder REF3325 Product Folder R4 C1 VCC R3 - VPWM + VIN VREF R1 + ++ + U1A - U2A V R2 C2 CC VTRI C3 R7 - ++ U1B VREF VCC VREF - ++ U2B VCC R6 R5 An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments SLAU508-June 2013-Revised June 2013 Analog Pulse Width Modulation 1 Copyright © 2013, Texas Instruments Incorporated www.ti.com 1 Design Summary The design requirements are as follows: Supply voltage: 5 Vdc Input voltage: -2 V to +2 V, dc coupled Output: 5 V, 500 kHz PWM Ideal transfer function: V The design goals and performance are summarized in Table 1. -

The Oscilloscope and the Function Generator: Some Introductory Exercises for Students in the Advanced Labs

The Oscilloscope and the Function Generator: Some introductory exercises for students in the advanced labs Introduction So many of the experiments in the advanced labs make use of oscilloscopes and function generators that it is useful to learn their general operation. Function generators are signal sources which provide a specifiable voltage applied over a specifiable time, such as a \sine wave" or \triangle wave" signal. These signals are used to control other apparatus to, for example, vary a magnetic field (superconductivity and NMR experiments) send a radioactive source back and forth (M¨ossbauer effect experiment), or act as a timing signal, i.e., \clock" (phase-sensitive detection experiment). Oscilloscopes are a type of signal analyzer|they show the experimenter a picture of the signal, usually in the form of a voltage versus time graph. The user can then study this picture to learn the amplitude, frequency, and overall shape of the signal which may depend on the physics being explored in the experiment. Both function generators and oscilloscopes are highly sophisticated and technologically mature devices. The oldest forms of them date back to the beginnings of electronic engineering, and their modern descendants are often digitally based, multifunction devices costing thousands of dollars. This collection of exercises is intended to get you started on some of the basics of operating 'scopes and generators, but it takes a good deal of experience to learn how to operate them well and take full advantage of their capabilities. Function generator basics Function generators, whether the old analog type or the newer digital type, have a few common features: A way to select a waveform type: sine, square, and triangle are most common, but some will • give ramps, pulses, \noise", or allow you to program a particular arbitrary shape. -

The Differential Pair As a Triangle-Sine Wave Converter V - ROBERT G

418 IEEE JOURNAL OF SOLID-STATE CIRCUITS, JUNE 1976 Correspondence The Differential Pair as a Triangle-Sine Wave Converter v - ROBERT G. MEYER, WILLY M. C. SANSEN, SIK LUI, AND STEFAN PEETERS R~ R~ 1 / Abstract–The performance of a differential pair with emitter degen- eration as a triangle-sine wave converter is analyzed. Equations describ- ing the circuit operation are derived and solved both analytically and by computer. This allows selection of operating conditions for optimum performance such that total harmonic distortion as low as 0.2 percent “- has been measured. -vEE (a) I. INTRODUCTION The conversion of ttiangle waves to sine waves is a function I ---- I- often required in waveshaping circuits. For example, the oscil- lators used in function generators usually generate triangular output waveforms [ 1] because of the ease with which such oscillators can operate over a wide frequency range including very low frequencies. This situation is also common in mono- r v, Zr t lithic oscillators [2] . Sinusoidal outputs are commonly de- sired in such oscillators and can be achieved by use of a non- linear circuit which produces an output sine wave from an input triangle wave. — — — — The above circuit function has been realized in the past by -I -I ----- means of a piecewise linear approximation using diode shaping J ‘“b ‘M VI networks [ 1] . However, a simpler approach and one well M suited to monolithic realization has been suggested by Grebene [3] . This is shown in Fig. 1 and consists simply of a differen- 77 tial pair with an appropriate value of emitter resistance R. -

CD-Synth: a Rotating, Untethered, Digital Synthesizer

CD-Synth: a Rotating, Untethered, Digital Synthesizer Patrick Chwalek Joseph A. Paradiso Responsive Environments Group Responsive Environments Group MIT Media Lab MIT Media Lab 75 Amherst Street 75 Amherst Street Cambridge, MA 02139, USA Cambridge, MA 02139, USA [email protected] [email protected] ABSTRACT sounds out of a combination of oscillators, filters, and ef- We describe the design of an untethered digital synthesizer fects. For light-based synthesizer systems, transmitted light that can be held and manipulated while broadcasting au- can be modulated in specific patterns to change virtually dio data to a receiving off-the-shelf Bluetooth receiver. The any characteristic of a sound that is produced by photodi- synthesizer allows the user to freely rotate and reorient the ode exposure. An example is Jacques Dudon's photosonic instrument while exploiting non-contact light sensing for a instrument [7, 4] from the 1980s, which was composed of truly expressive performance. The system consists of a suite a photodiode, light source, semi-transparent rotating disk, of sensors that convert rotation, orientation, touch, and user and an optical filter. The disk was patterned in such a way proximity into various audio filters and effects operated on that when rotated, the intensity of light passing through it preset wave tables, while offering a persistence of vision dis- changes at audio frequencies (like an optical sound track on play for input visualization. This paper discusses the design a film, or vintage optical samplers like the Optigan), and of the system, including the circuit, mechanics, and software was further operated on by the handheld filter or manu- layout, as well as how this device may be incorporated into ally moving the lightsource and/or photodetector, so that a performance. -

User Manual Synclavier V

USER MANUAL ARTURIA – Synclavier V – USER MANUAL 1 Direction Frédéric Brun Kevin Molcard Development Cameron Jones (lead) Valentin Lepetit Baptiste Le Goff (project manager) Samuel Limier Stefano D’Angelo Germain Marzin Baptiste Aubry Mathieu Nocenti Corentin Comte Pierre Pfister Pierre-Lin Laneyrie Benjamin Renard Design Glen Darcey Sebastien Rochard Shaun Ellwood Greg Vezon Morgan Perrier Sound Design Drew Anderson Victor Morello Jean-Baptiste Arthus Dave Polich Wally Badarou Stéphane Schott Jean-Michel Blanchet Paul Shilling Marion Demeulemeester Edware Ten Eyck Richard Devine Nori Ubukata Thomas Koot Manual Kevin E. Maloney Jason Valax Corentin Comte ARTURIA – Synclavier V – USER MANUAL 2 Special Thanks Brandon Amison Steve Lipson Matt Bassett Terence Marsden François Best Bruce Mariage Alejandro Cajica Sergio Martinez Chuck Capsis Shaba Martinez Dwight Davies Jay Marvalous Kosh Dukai Miguel Moreno Ben Eggehorn Ken Flux Pierce Simon Franglen Fernando Manuel Rodrigues Boele Gerkes Daniel Saban Jeff Haler Carlos Tejeda Neil Hester James Wadell Chris Jasper Chad Wagner Laurent Lemaire Chuck Zwick © ARTURIA S.A. – 1999-2016 – All rights reserved. 11 Chemin de la Dhuy 38240 Meylan FRANCE http://www.arturia.com ARTURIA – Synclavier V – USER MANUAL 3 Table of contents 1 INTRODUCTION ........................................................................................... 11 1.1 What is Synclavier V? ................................................................................................... 11 1.2 1.2 History of the Original Instrument -

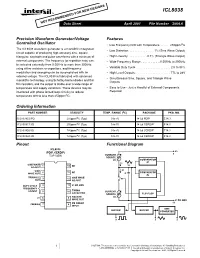

ICL8038 TM D FO NDE MME ECO OT R N Data Sheet April 2001 File Number 2864.4

NS ESIG W D R NE ICL8038 TM D FO NDE MME ECO OT R N Data Sheet April 2001 File Number 2864.4 Precision Waveform Generator/Voltage Features Controlled Oscillator • Low Frequency Drift with Temperature...... 250ppm/oC The ICL8038 waveform generator is a monolithic integrated • LowDistortion...............1%(SineWaveOutput) tle circuit capable of producing high accuracy sine, square, 80 triangular, sawtooth and pulse waveforms with a minimum of • HighLinearity ...........0.1%(Triangle Wave Output) external components. The frequency (or repetition rate) can • Wide Frequency Range ............0.001Hzto300kHz - be selected externally from 0.001Hz to more than 300kHz using either resistors or capacitors, and frequency • VariableDutyCycle.....................2%to98% modulation and sweeping can be accomplished with an • HighLevelOutputs......................TTLto28V ci- external voltage. The ICL8038 is fabricated with advanced • Simultaneous Sine, Square, and Triangle Wave monolithic technology, using Schottky barrier diodes and thin Outputs e- film resistors, and the output is stable over a wide range of temperature and supply variations. These devices may be • Easy to Use - Just a Handful of External Components er- interfaced with phase locked loop circuitry to reduce Required o /Vo temperature drift to less than 250ppm/ C. e - Ordering Information ed PART NUMBER STABILITY TEMP. RANGE (oC) PACKAGE PKG. NO. il- o r) ICL8038CCPD 250ppm/ C(Typ) 0to70 14LdPDIP E14.3 tho ICL8038CCJD 250ppm/oC(Typ) 0to70 14LdCERDIP F14.3 ICL8038BCJD 180ppm/oC(Typ) -

Chapter 9. Fourier Series A. the Fourier Sine Series

Vector Spaces in Physics 8/6/2015 Chapter 9. Fourier Series A. The Fourier Sine Series The general solution. In Chapter 8 we found solutions to the wave equation for a string fixed at both ends, of length L, and with wave velocity v, yn x, t A n sin k n x cos n t k n n L 1 n 2L , n = 1, 2, 3, . (9-1) n v n n L v fn n 2L We are now going to proceed to describe an arbitrary motion of the string with both ends fixed in terms of a linear superposition of normal modes: nx general solution, string , (9-2) y x, t Ann sin cos t n1 L fixed at both ends nv where and the coefficients An are to be determined. Here are some things to be noted: n L (1) We are assuming for the moment that this equation is true - that is, in the limit where we include an infinite number of terms, that the infinite series is an arbitrarily good approximation to the solution y x, t . (2) Each term in the series is separately a solution to the wave equation satisfying the boundary conditions, and so the series sum itself is such a solution. (3) This series is sort of like an expansion of a vector in terms of a set of basis vectors. In this picture the coefficients An are the coordinates of the function . (4) We still have to specify initial conditions and find a method to ensure that they are satisfied. -

Music Synthesizer Senior Project: Danalog

Music Synthesizer Senior Project: Danalog Report by: Vikrant Marathe Other Group Members: Bryan Bellin, Evan Lew, Jordan Wong Advisor: Dr. Wayne Pilkington Spring 2017 Cal Poly Electrical Engineering Table of Contents I. Introduction II. Product Design Engineering Requirements III. Background IV. System Design - Functional Decomposition (Level 1) V. Physical Construction and Integration VI. Integrated System Tests and Results VII. Bibliography List of Tables and Figures Abstract The Danalog is a 25 key portable digital music synthesizer that uses multiple synthesis methods and effects to generate sounds. Sound varieties included three synthesis methods including FM, subtractive, and sample-based, with up to eight adjustable parameters, at least four effects, including reverb, chorus, and flange, with five adjustable parameters, and at least two note polyphony, and a five band equalizer. The user would be able to adjust these effects using digital encoders and potentiometers and view the settings on two LCD screens. The finals project was unable to meet the original design requirements. The FM synthesis method was primarily working in the end product. The synthesizer was built to produce two note polyphony. The LCD screens displayed the information about the synthesis method as the user plays. I. Introduction The purpose of this project was to create a portable, inexpensive digital music synthesizer for amateur musicians. The intended customer base consists of young, amateur musicians who don’t have a big budget for a more expensive music synthesizer. The market requirements for this product are as follows: - The Danalog Synthesizer will be inexpensive at less than $200 - The design will be sleek and lightweight to promote portability - Up to eight adjustable synthesis parameters - Up to five adjustable effects parameters - Five band equalizer Our intended customer is an amateur musician seeking an inexpensive digital synthesizer to create a wide array of user-defined sounds. -

THE SOCIAL CONSTRUCTION of the EARLY ELECTRONIC MUSIC SYNTHESIZER Author(S): Trevor Pinch and Frank Trocco Source: Icon, Vol

International Committee for the History of Technology (ICOHTEC) THE SOCIAL CONSTRUCTION OF THE EARLY ELECTRONIC MUSIC SYNTHESIZER Author(s): Trevor Pinch and Frank Trocco Source: Icon, Vol. 4 (1998), pp. 9-31 Published by: International Committee for the History of Technology (ICOHTEC) Stable URL: http://www.jstor.org/stable/23785956 Accessed: 27-01-2018 00:41 UTC JSTOR is a not-for-profit service that helps scholars, researchers, and students discover, use, and build upon a wide range of content in a trusted digital archive. We use information technology and tools to increase productivity and facilitate new forms of scholarship. For more information about JSTOR, please contact [email protected]. Your use of the JSTOR archive indicates your acceptance of the Terms & Conditions of Use, available at http://about.jstor.org/terms International Committee for the History of Technology (ICOHTEC) is collaborating with JSTOR to digitize, preserve and extend access to Icon This content downloaded from 70.67.225.215 on Sat, 27 Jan 2018 00:41:54 UTC All use subject to http://about.jstor.org/terms THE SOCIAL CONSTRUCTION OF THE EARLY ELECTRONIC MUSIC SYNTHESIZER Trevor Pinch and Frank Troceo In this paper we examine the sociological history of the Moog and Buchla music synthesizers. These electronic instruments were developed in the mid-1960s. We demonstrate how relevant social groups exerted influence on the configuration of synthesizer construction. In the beginning, the synthesizer was a piece of technology that could be designed in a variety of ways. Despite this interpretative flexibility in its design, it stabilised as a keyboard instrument. -

PWM Techniques: a Pure Sine Wave Inverter

2010-2011 Worcester Polytechnic Institute Major Qualifying Project PWM Techniques: A Pure Sine Wave Inverter Advisor: Professor Stephen J. Bitar, ECE Student Authors: Ian F. Crowley Ho Fong Leung 4/27/2011 Contents Figures ........................................................................................................................................................... 3 Abstract ......................................................................................................................................................... 6 Introduction .................................................................................................................................................. 7 Problem Statement ....................................................................................................................................... 8 Background Research.................................................................................................................................. 10 Prior Art ................................................................................................................................................... 10 Comparison of Commercially Available Inverters ............................................................................... 11 Examination of an Existing Design ...................................................................................................... 15 DC to AC Inversion .................................................................................................................................