LPC Microcontrollers Discover the Difference

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Vcf Pnw 2019

VCF PNW 2019 http://vcfed.org/vcf-pnw/ Schedule Saturday 10:00 AM Museum opens and VCF PNW 2019 starts 11:00 AM Erik Klein, opening comments from VCFed.org Stephen M. Jones, opening comments from Living Computers:Museum+Labs 1:00 PM Joe Decuir, IEEE Fellow, Three generations of animation machines: Atari and Amiga 2:30 PM Geoff Pool, From Minix to GNU/Linux - A Retrospective 4:00 PM Chris Rutkowski, The birth of the Business PC - How volatile markets evolve 5:00 PM Museum closes - come back tomorrow! Sunday 10:00 AM Day two of VCF PNW 2019 begins 11:00 AM John Durno, The Lost Art of Telidon 1:00 PM Lars Brinkhoff, ITS: Incompatible Timesharing System 2:30 PM Steve Jamieson, A Brief History of British Computing 4:00 PM Presentation of show awards and wrap-up Exhibitors One of the defining attributes of a Vintage Computer Festival is that exhibits are interactive; VCF exhibitors put in an amazing amount of effort to not only bring their favorite pieces of computing history, but to make them come alive. Be sure to visit all of them, ask questions, play, learn, take pictures, etc. And consider coming back one day as an exhibitor yourself! Rick Bensene, Wang Laboratories’ Electronic Calculators, An exhibit of Wang Labs electronic calculators from their first mass-market calculator, the Wang LOCI-2, through the last of their calculators, the C-Series. The exhibit includes examples of nearly every series of electronic calculator that Wang Laboratories sold, unusual and rare peripheral devices, documentation, and ephemera relating to Wang Labs calculator business. -

NXP Powerpoint Template Confidential 16:9 Widescreen

NXP MCU PRODUCT UPDATE & ROADMAP Q4 2016 NXP’S MCU POWERHOUSE PORTFOLIO 1 PUBLIC USE NXP Microcontrollers Business Line Why Customers Choose Us Applications • Comprehensive portfolio supporting the diverse IoT landscape Wearable / Healthcare • Fitness & Wireless Healthcare • Extensive software and development environment • Diabetes & Cardiac Care • Diagnostics & therapy • Industry leading customer support, quality, and longevity Home & Building Automation • Broad ecosystem of partners enabling system solutions • Smart meters & grid • Integrated wireless connectivity solutions • Ease of use solutions tailored for mass market • Home energy control Smart Accessories • Game controllers and consoles Example Customers • Wearable computing • eReaders, tablets, portable navigation Vehicle Networking & Information • Infotainment, software define radio • Navigation systems, E-call Home Appliances • Energy efficient refrigerators, dishwashers • Human-machine interface • Connected appliances Industrial Controls & Factory Automation • Machine-to-machine • Motor control Products • Industrial networking Kinetis & LPC 32-bit i.MX ARM® Applications 2 ARMPUBLIC® Microcontrollers USE Processors NXP MCUs - Powerhouse Portfolio ARM Expertise Broadest licensee of ARM cores in industry Most scalable portfolio with Expansive Portfolio optimized performance and capabilities Development Tools Best-in-class hardware platforms and software solutions Ecosystem Leadership Industry leading partnerships for innovation and differentiation Experienced global support team -

Schedule 14A Employee Slides Supertex Sunnyvale

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 SCHEDULE 14A Proxy Statement Pursuant to Section 14(a) of the Securities Exchange Act of 1934 Filed by the Registrant Filed by a Party other than the Registrant Check the appropriate box: Preliminary Proxy Statement Confidential, for Use of the Commission Only (as permitted by Rule 14a-6(e)(2)) Definitive Proxy Statement Definitive Additional Materials Soliciting Material Pursuant to §240.14a-12 Supertex, Inc. (Name of Registrant as Specified In Its Charter) Microchip Technology Incorporated (Name of Person(s) Filing Proxy Statement, if other than the Registrant) Payment of Filing Fee (Check the appropriate box): No fee required. Fee computed on table below per Exchange Act Rules 14a-6(i)(1) and 0-11. (1) Title of each class of securities to which transaction applies: (2) Aggregate number of securities to which transaction applies: (3) Per unit price or other underlying value of transaction computed pursuant to Exchange Act Rule 0-11 (set forth the amount on which the filing fee is calculated and state how it was determined): (4) Proposed maximum aggregate value of transaction: (5) Total fee paid: Fee paid previously with preliminary materials. Check box if any part of the fee is offset as provided by Exchange Act Rule 0-11(a)(2) and identify the filing for which the offsetting fee was paid previously. Identify the previous filing by registration statement number, or the Form or Schedule and the date of its filing. (1) Amount Previously Paid: (2) Form, Schedule or Registration Statement No.: (3) Filing Party: (4) Date Filed: Filed by Microchip Technology Incorporated Pursuant to Rule 14a-12 of the Securities Exchange Act of 1934 Subject Company: Supertex, Inc. -

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

SOMNIUM® DRT Benchmarks Whitepaper DRT 4.0 Release : March 2017

SOMNIUM® DRT Benchmarks Whitepaper DRT 4.0 release : March 2017 www.somniumtech.com SOMNIUM® DRT is a complete C/C++ embedded software Microchip SAM examples Atmel START was used to create an "empty" C program including Atmel Software Framework development environment which supports ARM® Cortex® M (ASF) routines to configure the on-chip PLL to highest devices from leading semiconductor vendors. possible frequency on a SAMD21 device (32KByte ROM, Vendor Family Cortex 4KByte RAM). IAR Embedded Workbench uses less memory than vanilla GNU tools from Atmel Studio, DRT Microchip SAM M0+, M3, M4 does even better and uses the smallest amount of ROM. Kinetis M0+, M4 NXP ROM RAM LPC M0, M0+, M3, M4 DRT is smaller DRT is smaller KBytes KBytes (% and bytes) (% and bytes) STMicroelectronics STM32 M0, M0+, M3, M4 DRT 1.5 n/a n/a 8.7 n/a n/a Other software vendors use adjectives. SOMNIUM use Atmel STUDIO 1.8 24.1% 360 8.7 0.0% 0 facts. This whitepaper compares benchmarking results for IAR 1.5 2.4% 36 8.6 -0.4% -32 SOMNIUM DRT against other toolchain products to demonstrate that DRT builds the smallest, fastest most energy efficient code with no source code changes required. NXP Kinetis examples We used NXP's Kinetis SDK v2 (now No defeat devices! Unlike many well known software renamed as MCUXpresso SDK) tools to create an "empty" C vendors, SOMNIUM play fair and do not put “benchmark program (including use of Kinetis SDK v2 routines to enable special” features in our products to change their behavior in the on-chip PLL) for a KL25Z device. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

Microprocessors in the 1970'S

Part II 1970's -- The Altair/Apple Era. 3/1 3/2 Part II 1970’s -- The Altair/Apple era Figure 3.1: A graphical history of personal computers in the 1970’s, the MITS Altair and Apple Computer era. Microprocessors in the 1970’s 3/3 Figure 3.2: Andrew S. Grove, Robert N. Noyce and Gordon E. Moore. Figure 3.3: Marcian E. “Ted” Hoff. Photographs are courtesy of Intel Corporation. 3/4 Part II 1970’s -- The Altair/Apple era Figure 3.4: The Intel MCS-4 (Micro Computer System 4) basic system. Figure 3.5: A photomicrograph of the Intel 4004 microprocessor. Photographs are courtesy of Intel Corporation. Chapter 3 Microprocessors in the 1970's The creation of the transistor in 1947 and the development of the integrated circuit in 1958/59, is the technology that formed the basis for the microprocessor. Initially the technology only enabled a restricted number of components on a single chip. However this changed significantly in the following years. The technology evolved from Small Scale Integration (SSI) in the early 1960's to Medium Scale Integration (MSI) with a few hundred components in the mid 1960's. By the late 1960's LSI (Large Scale Integration) chips with thousands of components had occurred. This rapid increase in the number of components in an integrated circuit led to what became known as Moore’s Law. The concept of this law was described by Gordon Moore in an article entitled “Cramming More Components Onto Integrated Circuits” in the April 1965 issue of Electronics magazine [338]. -

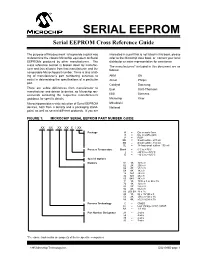

Serial EEPROM Cross Reference Guide

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

Lpc43s6x Product Data Sheet

LPC43S6x 32-bit ARM Cortex-M4/M0 MCU; up to 1 MB flash and 154 kB SRAM; Ethernet, two High-speed USB, LCD, EMC, AES engine Rev. 1.3 — 13 January 2020 Product data sheet 1. General description The LPC43S6x are ARM Cortex-M4 based microcontrollers for embedded applications which include an ARM Cortex-M0 coprocessor and an ARM Cortex-M0 subsystem for managing peripherals, up to 1 MB of flash and 154 kB of on-chip SRAM, 16 kB of EEPROM memory, a quad SPI Flash Interface (SPIFI), advanced configurable peripherals such as the SCTimer/PWM and the Serial General Purpose I/O (SGPIO) interface, security features with AES engine, two High-speed USB controllers, Ethernet, LCD, an external memory controller, and multiple digital and analog peripherals. The LPC43S6x operate at CPU frequencies of up to 204 MHz. The ARM Cortex-M4 is a 32-bit core that offers system enhancements such as low power consumption, enhanced debug features, and a high level of support block integration. The ARM Cortex-M4 CPU incorporates a 3-stage pipeline, uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals, and includes an internal prefetch unit that supports speculative branching. The ARM Cortex-M4 supports single-cycle digital signal processing and SIMD instructions. A hardware floating-point processor is integrated into the core. The LPC43S6x include an application ARM Cortex-M0 coprocessor and a second ARM Cortex-M0 subsystem for managing the SGPIO and SPI peripherals.The ARM Cortex-M0 coprocessor is an energy-efficient and easy-to-use 32-bit core which is upward code- and tool-compatible with the Cortex-M4 core.