NCQ) and ATA Tagged Command Queuing (TCQ

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

High Performance Solid State Storage Under Linux

High Performance Solid State Storage Under Linux Eric Seppanen, Matthew T. O’Keefe, David J. Lilja Department of Electrical and Computer Engineering University of Minnesota Minneapolis, MN 55455 fsepp0019, mokeefe, [email protected] Abstract—Solid state drives (SSDs) allow single-drive perfor- II. BACKGROUND mance that is far greater than disks can produce. Their low latency and potential for parallel operations mean that they are A. Solid State Drives able to read and write data at speeds that strain operating system In many ways, SSD performance is far superior to that of I/O interfaces. Additionally, their performance characteristics expose gaps in existing benchmarking methodologies. disk drives. With random read performance nearly identical We discuss the impact on Linux system design of a prototype to sequential read performance, seek-heavy workloads can PCI Express SSD that operates at least an order of magnitude perform orders of magnitude faster with an SSD compared to faster than most drives available today. We develop benchmark- a disk drive. SSDs have other benefits besides performance: ing strategies and focus on several areas where current Linux they consume less power and are more resistant to physical systems need improvement, and suggest methods of taking full advantage of such high-performance solid state storage. abuse than disk drives. We demonstrate that an SSD can perform with high through- But SSDs bear the burden of NAND flash management. put, high operation rates, and low latency under the most Large flash block erase sizes cause write amplification and difficult conditions. This suggests that high-performance SSDs delays, and drives must have large page-mapping tables to sup- can dramatically improve parallel I/O performance for future port small writes efficiently. -

SAS Enters the Mainstream Although Adoption of Serial Attached SCSI

SAS enters the mainstream By the InfoStor staff http://www.infostor.com/articles/article_display.cfm?Section=ARTCL&C=Newst&ARTICLE_ID=295373&KEYWORDS=Adaptec&p=23 Although adoption of Serial Attached SCSI (SAS) is still in the infancy stages, the next 12 months bode well for proponents of the relatively new disk drive/array interface. For example, in a recent InfoStor QuickVote reader poll, 27% of the respondents said SAS will account for the majority of their disk drive purchases over the next year, although Serial ATA (SATA) topped the list with 37% of the respondents, followed by Fibre Channel with 32%. Only 4% of the poll respondents cited the aging parallel SCSI interface (see figure). However, surveys of InfoStor’s readers are skewed by the fact that almost half of our readers are in the channel (primarily VARs and systems/storage integrators), and the channel moves faster than end users in terms of adopting (or at least kicking the tires on) new technologies such as serial interfaces. Click here to enlarge image To get a more accurate view of the pace of adoption of serial interfaces such as SAS, consider market research predictions from firms such as Gartner and International Data Corp. (IDC). Yet even in those firms’ predictions, SAS is coming on surprisingly strong, mostly at the expense of its parallel SCSI predecessor. For example, Gartner predicts SAS disk drives will account for 16.4% of all multi-user drive shipments this year and will garner almost 45% of the overall market in 2009 (see figure on p. 18). -

Engineering Specifications

DOC NO : Rev. Issued Date : 2020/10/08 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : ENGINEERING SPECIFICATIONS Product Name: CVB-CDXXX (WT) Model CVB-CD128 CVB-CD256 CVB-CD512 CVB-CD1024 Author: Ken Liao DOC NO : Rev. Issued Date : 2020/10/08 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Version History Date 0.1 Draft 2020/07/20 1.0 First release 2020/10/08 DOC NO : Rev. Issued Date : 2020/10/08 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Copyright 2020 SOLID STATE STORAGE TECHNOLOGY CORPORATION Disclaimer The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer. In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages. This document contains proprietary information protected by copyright. All rights are reserved. No part of this datasheet may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of SOLID STATE STORAGE Technology Corporation. DOC NO : Rev. Issued Date : 2020/10/08 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Table of Contents 1 Introduction ....................................................................... 5 1.1 Overview ............................................................................................. -

Dell EMC Poweredge RAID Controller S140 User’S Guide Notes, Cautions, and Warnings

Dell EMC PowerEdge RAID Controller S140 User’s Guide Notes, cautions, and warnings NOTE: A NOTE indicates important information that helps you make better use of your product. CAUTION: A CAUTION indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2018 - 2019 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. 2019 - 12 Rev. A09 Contents 1 Overview..................................................................................................................................... 6 PERC S140 specifications.....................................................................................................................................................6 Supported operating systems..............................................................................................................................................8 Supported PowerEdge systems.......................................................................................................................................... 9 Supported physical disks...................................................................................................................................................... 9 Management applications for the PERC S140................................................................................................................ -

Datasheet (PDF)

DOC NO : Rev. Issued Date : 2020/10/07 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : ENGINEERING SPECIFICATIONS Product Name: CVB-8DXXX-WT Model CVB-8D128- WT CVB-8D256 - WT CVB-8D512- WT CVB-8D1024 - WT Author: Ken Liao DOC NO : Rev. Issued Date : 2020/10/07 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Version History Date 0.1 Draft 2020/03/30 1.0 First release 2020/10/07 DOC NO : Rev. Issued Date : 2020/10/07 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Copyright 2020 SOLID STATE STORAGE TECHNOLOGY CORPORATION Disclaimer The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer. In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages. This document contains proprietary information protected by copyright. All rights are reserved. No part of this datasheet may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of SOLID STATE STORAGE Technology Corporation. DOC NO : Rev. Issued Date : 2020/10/07 V1.0 SOLID STATE STORAGE TECHNOLOGY CORPORATION 司 Revised Date : Table of Contents 1 Introduction ....................................................................... 5 1.1 Overview ............................................................................................. -

FWB's Guide to Storage

GtoS 2nd Ed. Book Page i Friday, March 27, 1998 12:05 PM FWB’s Guide to Storage Second Edition GtoS 2nd Ed. Book Page ii Friday, March 27, 1998 12:05 PM Copyright Notice This manual is copyrighted by FWB Software, LLC (FWB) with all rights reserved. Your rights with regard to this manual are subject to the restrictions and limitations imposed by the copyright laws of the United States of Amer- ica. Under the copyright laws, this manual may not be copied, reproduced, translated, transmitted or reduced to any printed or electronic medium or to any machine-readable form, in whole or in part, without the written consent of FWB. © 1991, 1996 By FWB Software, LLC December 1996 Part No.: 07-00841-201 GtoS 2nd Ed. Book Page iii Friday, March 27, 1998 12:05 PM Trademarks Hard Disk ToolKit, RAID ToolKit, SpaceMaker ToolKit, and CD-ROM Tool- Kit are trademarks of FWB Software, LLC. FWB is a registered trademark of FWB Software, LLC. All brand and product names are trademarks or registered trademarks of their respective holders. Credits This guide was written by Norman Fong with help from Joan Carter, Steve Dalton, Bruce Dundas, Eric Herzog, Al Pierce, Stuart Saraquse, and Fred Swan. It was designed, edited, and composed by Joan Carter with help from Allan Levite. Illustrations were produced by Deane Morris. The original version of this manual was written in 1991 by Leslie Feldman, Norman Fong, Kevin Kachadourian, Neil Strudwick, and Paul Worthington as part of FWB’s Hard Disk ToolKit 1.x manual. Dedication This book is dedicated to my family and friends who put up with the long hours put into this effort. -

3.5-Inch, SAS 15K Enterprise Hard Disk Drives MAX3036RC • MAX3073RC • MAX3147RC

Storage High performance and high capacity for your mission critical storage applications. 3.5-Inch, SAS 15K Enterprise Hard Disk Drives MAX3036RC • MAX3073RC • MAX3147RC State-of-the-art hard disk drives for your most demanding enterprise applications 3.5-inch RoHS compliant enterprise hard disk drives offer 15K RPM spindle speed and feature storage capacities up to 147GB1 Ideal for applications requiring high performance and high bandwidth Native Command Queuing (NCQ), providing faster execution of operation commands Uses smaller connectors and cables than U320, a benefit acknowledged by the SCSI Trade Association (STA) Point-to-point connection allows for improved input-output per second (IOPS) in proportion to the number of drives connected 1 One gigabyte (GB) = one billion bytes; accessible capacity will be less and actual capacity depends on the operating environment and formatting. 3.5-Inch, SAS 15K Enterprise Hard Disk Drives MAX3036RC • MAX3073RC • MAX3147RC 3.5-Inch, SAS 15K RPM Series Hard Disk Drive Specifications With more than 35 years of experience in hard disk Description MAX3036RC MAX3073RC MAX3147RC drive technology, Fujitsu can offer state-of-the-art Functional Specifications hard disk drives for your most demanding enterprise Storage capacity (formatted)1 36.7 GB 73.5 GB 147.0 GB applications. Our latest SAS offering is another Disks 1 2 4 Heads (read/write) 2 4 8 example, building on our market leadership in the Bytes/sector 512 Seek time Track to track Read: 0.2 ms (typ.) / Write: 0.4 ms (typ.) exploding SAS market. Average Read: 3.3 ms (typ) / Write: 3.8 ms (typ) The availability of this latest SAS offering Full track Read: 8.0 ms (typ) / Write: 9.0 ms (typ) Average latency time 2.00 ms solidifies Fujitsu as the SAS leader for all form factors Rotational speed (RPM) 15,000 in the enterprise market, reflecting a determination Areal density 59 Gbits/sq. -

Run-Time Detection of Protocol Bugs in Storage I/O Device Drivers Domenico Cotroneo, Luigi De Simone, Roberto Natella

1 Run-Time Detection of Protocol Bugs in Storage I/O Device Drivers Domenico Cotroneo, Luigi De Simone, Roberto Natella Abstract—Protocol violation bugs in storage device drivers are necessarily lead to such symptoms. The lack of detection can a critical threat for data integrity, since these bugs can silently lead to silent corruptions of users’ data, thus exacerbating the corrupt the commands and data flowing between the OS and cost of software failures. storage devices. Due to their nature, these bugs are notoriously difficult to find by traditional testing. In this paper, we propose In this paper, we propose a novel approach for detecting I/O a run-time monitoring approach for storage device drivers, in protocol violations in storage device drivers, by monitoring at order to detect I/O protocol violations that would otherwise run-time the interactions between the driver and the hardware silently escalate in corruptions of users’ data. The monitoring device controller. The purpose of the run-time monitor is to de- approach detects violations of I/O protocols by automatically learning a reference model from failure-free execution traces. The tect device driver failures in a timely manner. This solution is approach focuses on selected portions of the storage controller meant both to users and engineers of high-availability storage interface, in order to achieve a good trade-off in terms of low systems, including: administrators and end-users of the system, performance overhead and high coverage and accuracy of failure which need to get alarms about the onset of data corruptions in detection. -

PCI Express X4 Card > 2 X Internal M.2 Key B + 1 X Internal Nvme M.2

PCI Express x4 Card > 2 x internal M.2 Key B + 1 x internal NVMe M.2 Key M - Low Profile Form Factor Description This PCI Express card by Delock expands the PC by three M.2 slots. On the card can be connected up to two M.2 SATA modules in format 22110, 2280, 2260, 2242, 2230 and one M.2 PCIe module in format 22110, 2280, 2260, 2242, 2230. The SATA modules will be connected via SATA cables to the motherboard. Specification Item no. 89394 • Connectors: EAN: 4043619893942 internal: 2 x 67 pin M.2 key B slot Country of origin: Taiwan, Republic of 1 x 67 pin M.2 key M slot China 1 x PCI Express x4, V3.0 2 x SATA 6 Gb/s 7 pin receptacle Package: Box 1 x SATA 15 pin power plug • Interface: SATA + PCIe • Supports two M.2 modules in format 22110, 2280, 2260, 2242 and 2230 with key B or key B+M based on SATA and one M.2 module in format 22110, 2280, 2260, 2242 and 2230 with key M or key B+M based on PCIe • Maximum height of the components on the module: 1.5 mm, application of double-sided assembled modules supported • Data transfer rate up to 6 Gb/s • Power supply via PCI Express interface or via SATA 15 pin power connector • Supports Native Command Queuing (NCQ) • Supports NVM Express (NVMe) System requirements • Windows Vista/Vista-64/7/7-64/8.1/8.1-64/10/10-64, Linux Kernel 3.2.0 • PC with one free PCI Express x4 / x8 / x16 / x32 slot • One free SATA 7 pin interface for each connected M.2 module based on SATA Package content • PCI Express card • Low profile bracket • 3 x fixing screw © 2021 by Delock. -

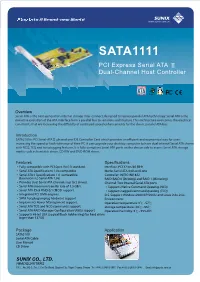

SATA1111 PCI Express Serial ATA Ⅱ Dual-Channel Host Controller

www.sunix.com.tw SATA1111 PCI Express Serial ATA Ⅱ Dual-Channel Host Controller Overview Serial ATA is the next-generation internal storage inter-connect, designed to replace parallel ATA technology. Serial ATA is the proactive evolution of the ATA interface from a parallel bus to serial bus architecture.This architecture overcomes the electrical constraints that are increasing the difficulty of continued speed enhancements for the classic parallel ATA bus. Introduction SATA2100 is PCI Serial-ATAⅡ phaesd one IDE Controller Card which provides an efficient and economical way for users increasing the speed or fault-tolerance of their PC. It can upgrade your desktop computer to have dual internal Serial ATA channels with NCQ,TCQ and hot plugging features. It is fully compliant Serial ATA ports on the device side to access Serial ATA storage media such as hard disk drives, CD-RW and DVD-ROM drives. Features Specifications ‧Fully compatible with PCI Spec.Ver2.3 standard. Interface: PCI 32 bit/66 MHz ‧Serial ATA Specifications 1.0a compatible. Mode: Serial ATA II phaesd one ‧Serial ATA II Specifications 1.0 compatible. Controller: INITIO INI1622 (Extensions to Serial ATA 1.0a) RAID: RAID 0 (Striping) and RAID 1 (Mirroring) ‧Provides dual Serial ATA channels (up to 2 drives). Channel:Two internal Serial ATA ports ‧Serial ATA maximum transfer rate of 1.5 GB/s. ‧Supports Native Command Queuing (NCQ) ‧Serial ATA Disk RAID 0/1/JBOD support. ‧Supports tagged command queuing (TCQ) ‧Integrated PCI DMA engines. O.S. Support:Windows2000/XP/2003/ and Linux 2.4x, 2.6x ‧SATA hot plug/unplug hardware support Environment : ‧Implements Power Management support. -

Delock PCI Express X16 Card to 1 X M.2 Key B + 1 X Nvme M.2 Key M + 1 X Msata - Low Profile Form Factor

Delock PCI Express x16 Card to 1 x M.2 Key B + 1 x NVMe M.2 Key M + 1 x mSATA - Low Profile Form Factor Description This PCI Express card by Delock expands the PC bytwo M.2 slots as well as an mSATA slot. One M.2 SATA module can be connected in format 2280, 2260, 2242, 2230 with this card and connected via SATA cable to the motherboard. Furthermore, oneM.2 NVMe / PCIe module in format 2280, 2260, 2242, 2230 can be connected. Additionally, one mSATA memory can be connected via SATA cable to the motherboard. All slots can be used separate or at the same time. Specification Item no. 90486 • Connectors: EAN: 4043619904860 1 x 67 pin M.2 key B slot 1 x 67 pin M.2 key M slot Country of origin: China 1 x mSATA slot (full size) 1 x PCI Express x16, V4.0 Package: • Retail Box 2 x SATA 6 Gb/s 7 pin plug • Interface: PCIe / SATA • Supports one M.2 module in format 2280, 2260, 2242 and 2230 with key B or key B+M based on SATA and one M.2 module in format 2280, 2260, 2242 and 2230 with key M or key B+M based on PCIe • Maximum height of the components on the module: 1.5 mm, application of double-sided assembled modules supported • 3 x LED indicator • Bootable • Supports NVM Express (NVMe) • Supports Native Command Queuing (NCQ) • Supports S.M.A.R.T. • Supports TRIM • Supports DevSleep • Hot Swap System requirements • Linux Kernel 4.6.4 or above • Windows 8.1/8.1-64/10/10-64 • PC with one free PCI Express x16 / x32 slot Package content • PCI Express card • Low profile bracket • 2 x SATA cable, length ca. -

SATA Multi Level Cell SSD for Use in Embedded Computing

Avnet Embedded. Support Around The Board™ Device Specification. DeLKIN DEVICES SSD-MLC www.avnet-embedded.eu SATA SSD Overview Features The Delkin Palladium™ SATA SSDs provide large capacity ▪ Drop-in replacement for 2.5 & 1.8 inch SATA HDD and high speed performance while improving system ▪ Boot from Windows 98/2000/XP/Vista/7 and Linux responsiveness in the standard 2.5 and 1.8 inch form ▪ Serial ATA Interface: SATA 3.0Gb/s factors. Product dependability is guaranteed using leading ▪ Fully compatible with ATA-7; Standard PIO 0-4 edge flash controller designs, MLC NAND Flash, premium ▪ SMART, TRIM & Secure Erase Support components and enhanced feature sets. The Palladium SSD ▪ NSA 9-12 Compliant product platform is targeted for SATA based client PCs, ▪ Low power consumption rugged mobile devices, medical devices, military, aerospace ▪ Supports Native Command Queuing (NCQ) and a variety of embedded system OEM applications. MLC NAND flash has the benefit of being a more cost effective solution compared to SLC due to the denser Specifications storage method used. Compared to HDDs, SSDs have much faster random access, silent operation and lower Capacity 8GB to 256GB* power consumption. With no moving parts, SATA SSDs Form Factor 2.5” Type (100.0 x 70.0 x 9.5 min)1.8” allow for faster start up, lower latency, consistent read Type (78.0 x 54.0 x 5 min) performance, and a higher reliability by eliminating the Host Interface Serial ATA interface of 3.0Gb/s risk of mechanical failures. Fully complies with ATA-7 Specification NOTICES: Product information, pricing and availability are subject to change at any time without notice.