Analytical Approaches to Load Modulation Power Amplifier Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Signal Issue 35

Signal Issue 35 Tricks of the Trade Dave Porter G4OYX and Alan Beech G1BXG We continue to celebrate the 50th anniversary of the start of offshore commercial radio in the UK and are now in June 1965. By this time, the number of stations on the air was increasing steadily, taking advantage of the (lack of) laws at the time with regard to operations in International Waters. The first two stations, Caroline and Atlanta, had used 10 kW AM transmitters by Continental Electronics employing their patented version of screen grid modulation but, just prior to Christmas 1964, the US-inspired and -built station of Radio London on the former US minesweeper USS Density renamed M/V Galaxy was on the air with test transmissions on 266 m, 1124 kHz, running, at first, 17 kW. This 50 kW transmitter was an RCA BTA-50H and was the first of many in the offshore fleet to employ the ‘Ampliphase’ approach. From ‘outphasing’ to ‘Ampliphase’ Amplitude from phase The theory of what became known as ‘Ampliphase’ was The principle of ‘Ampliphase’ is to take a single frequency proposed and developed in France by Henry Chireix in drive source, split it into two feeds, phase modulate each 1935 who called the technique ‘outphasing’. feed, amplify as required and add the two signals in a combining network. Amplitude modulation is achieved by ‘Outphasing’ was not taken up initially by RCA but by the degree of addition or subtraction due to the phase McClatchy Broadcasting in the late 1940s, first at KFBK, difference between the two signals. -

Hans Knot International Radio Report April 2016 Welcome to Another

Hans Knot International Radio Report April 2016 Welcome to another edition of the International Radio Report. Thanks all for your e mails, memories, photos, questions and more. Part of the report is what was left after the March edition was totally filled and so let’s go with this edition in which first there’s space for a story I wrote last months after again doing some research: ‘Ronan O’Rahilly, Georgie Fame and the Blue Fames. Where it really went wrong!’ On this subject I’ve written before but let’s go back in time and also add some new facts to it: ‘Was Ronan O’Rahilly the manager of Georgie Fame?’ I can tell you there was a problem with an important instrument. When in April 1964 Granada Television came with an edition of the ‘World in action’ series, which was a production from Michael Hodges, they informed the television public about a new form of Piracy, the watery pirates. Two radio ships bringing music and entertainment under the names of Radio Caroline and Radio Atlanta. Radio Caroline was the first 20th century Pirate off the British coast with programs, at that stage, for 12 hours a day. Interviews with the Caroline people were made in the offices of Queen Magazine in the city of London and included – among others – Jocelyn Stevens and the then 23-year old Irish Ronan O’Rahilly. During this documentary it became known, which we would also read in several newspapers in the then following weeks, that Ronan O’Rahilly had started his radiostation Caroline as he couldn’t get his artists played on stations like Radio Luxembourg. -

Broadcasting Equipment Photographs, Ca

http://oac.cdlib.org/findaid/ark:/13030/c8b85b80 No online items Broadcasting Equipment photographs, ca. 1940s-1970s Processed by Sue Hwang with assistance from Julie Graham, 2012; machine-readable finding aid created by Caroline Cubé. UCLA Library Special Collections Room A1713, Charles E. Young Research Library Box 951575 Los Angeles, CA, 90095-1575 (310) 825-4988 [email protected] ©2014 The Regents of the University of California. All rights reserved. Broadcasting Equipment 1903 1 photographs, ca. 1940s-1970s Descriptive Summary Title: Broadcasting Equipment photographs Collection number: 1903 Contributing Institution: UCLA Library Special Collections Language of Material: English Physical Description: 38.5 linear ft.(77 boxes) Date (inclusive): ca. 1940s-1970s Abstract: The collection consists of photographs of various types of indoor and outdoor equipment related to mid-twentieth century radio and television broadcasting. Physical location: Stored off-site at SRLF. Advance notice is required for access to the collection. Please contact UCLA Library Special Collections for paging information. Restrictions on Access Open for research. STORED OFF-SITE AT SRLF. Advance notice is required for access to the collection. Please contact UCLA Library Special Collections for paging information. Restrictions on Use and Reproduction Property rights to the physical object belong to the UC Regents. Literary rights, including copyright, are retained by the creators and their heirs. It is the responsibility of the researcher to determine who holds the copyright and pursue the copyright owner or his or her heir for permission to publish where The UC Regents do not hold the copyright. Preferred Citation [Identification of item], Broadcasting Equipment photographs (Collection 1903). -

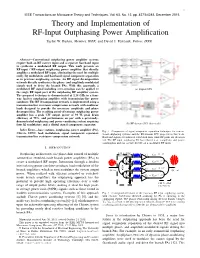

Theory and Implementation of RF-Input Outphasing Power Amplification Taylor W

1 Theory and Implementation of RF-Input Outphasing Power Amplification Taylor W. Barton, Member, IEEE, and David J. Perreault, Fellow, IEEE Abstract—Conventional outphasing power amplifier systems require both an RF carrier input and a separate baseband input to synthesize a modulated RF output. This work presents an RF-input / RF-output outphasing power amplifier that directly amplifies a modulated RF input, eliminating the need for multiple costly IQ modulators and baseband signal component separation as in previous outphasing systems. An RF signal decomposition network directly synthesizes the phase- and amplitude-modulated signals used to drive the branch PAs. With this approach, a modulated RF signal including zero-crossings can be applied to (a) Digital SCS the single RF input port of the outphasing RF amplifier system. The proposed technique is demonstrated at 2.14 GHz in a four- way lossless outphasing amplifier with transmission-line power combiner. The RF decomposition network is implemented using a transmission-line resistance compression network with nonlinear loads designed to provide the necessary amplitude and phase decomposition. The resulting proof-of-concept outphasing power amplifier has a peak CW output power of 93 W, peak drain efficiency of 70%, and performance on par with a previously- demonstrated outphasing and power combining system requiring four IQ modulators and a digital signal component separator. (b) RF-domain SCS (this work) Index Terms—base stations, outphasing, power amplifier (PA), Fig. 1. Comparison of signal component separation techniques for conven- Chireix, LINC, load modulation, signal component separator, tional outphasing systems and the RF-domain SCS proposed in this work. -

Escuela De Ingeniería Estudio

ESCUELA DE INGENIERÍA ESTUDIO, PLANIFICACIÓN Y DISEÑO DE UNA RADIODIFUSORA EN AM PROYECTO PREVIO A LA OBTENCIÓN DEL TITULO DE INGENIERO EN ELECTRÓNICA Y TELECOMUNICACIONES JOSÉ LUIS SUÁREZ MONTALVO DIRECTOR: Ing. RAÚL ANTONIO CALDERÓN EGAS Quito, Noviembre 2001 DECLARACIÓN Yo, José Luis Suárez Mpntalvo, declaro bajo juramento que el trabajo aquí descrito es de mi autoría; que no ha sido previamente presentada para ningún grado o calificación profesional; y, que he consultado las referencias bibliográficas que se incluyen en este documento. A través de la presente declaración cedo mis derechos de propiedad intelectual correspondientes a este trabajo, a la Escuela Politécnica Nacional, según lo establecido por la Ley de Propiedad Intelectual, por su Reglamento y por la normatividad institucional vigente. José Luis Suárez Montaívo CERTIFICACIÓN Certifico que ei presente trabajo fue desarrollado por José Luis Suarez Montalvo, bajo mi supervisión. Ing. Antonio Calderón E. DIRECTOR DE PROYECTO AGRADECIMIENTOS Primeramente a Dios, por haberme permitido llegar a la culminación de mis estudios de ingeniería. A los miembros de mi familia, y en especial a mi queridísima madre por haberme dado la vida, sus consejos y su apoyo siempre, animándome a seguir adelante. A mi amada esposa, por su ayuda incondicional durante mis estudios y en la preparación de este trabajo. Al ingeniero Antonio Calderón E. por sus valiosas orientaciones y guía en la elaboración de este proyecto. A la Escuela Politécnica Nacional, a mis profesores y compañeros por haberme dado la formación que me permite ahora ser mejor ciudadano. A los miembros de la familia Iglesias García por toda la colaboración prestada, y en particular a José Luis Iglesias. -

Cambridge University Press 978-1-107-06828-5 — Radio Systems Engineering Steven W

Cambridge University Press 978-1-107-06828-5 — Radio Systems Engineering Steven W. Ellingson Index More Information INDEX 1/f noise, see noise beam, 53 antenna temperature, see antenna ABCD parameters, 229 beam antenna, 49–51 APCO P25, see land mobile radio FS/4 frequency conversion, 564–568 cell phone, 382 aperture efficiency, 52 π 4 -QPSK, see modulation current distribution, 35 aperture uncertainty, see analog-to-digital μ-law, see companding dipole, 35–43, 221, 255, 381, 391 converter dipole, 5/8-λ,39 application-specific integrated circuit A-law, see companding dipole, batwing, 43 (ASIC), 576 absorption dipole, bowtie, 42 arcing, 109 atmospheric, 93–94, 590 dipole, electrically-short (ESD), 20 array (antenna), see antenna ionospheric, 96 dipole, folded, 42, 55 array factor, 54 acquisition, of phase, 124 dipole, full-wave (FWD), 39 ASK, see modulation active mixer, see mixer dipole, half-wave (HWD), 20, 37, 49 atmospheric absorption, see absorption, adaptive differential PCM (ADPCM), dipole, off-center-fed, 39, 40 atmospheric 142 dipole, planar, 41 atmospheric noise, see noise adjacent channel power ratio (ACPR), dipole, sleeve, 41 ATSC, see television 541 discone, 382 attenuation constant, 93, 234 admittance (Y) parameters, 229 electrically-small (ESA), 382–390 attenuation rate, see path loss advanced wireless services (AWS), 587 equivalent circuit, 40 attenuator, digital step, 481 alias (aliasing), see analog-to-digital feed, 51, 56, 224 audio processing, 137–138 converter helix, axial-mode, 57 autocorrelation, 85 AM broadcasting, -

(12) United States Patent (10) Patent No.: US 9,608,677 B2 Rawlins Et Al

US009608677B2 (12) United States Patent (10) Patent No.: US 9,608,677 B2 Rawlins et al. (45) Date of Patent: Mar. 28, 2017 (54) SYSTEMS AND METHODS OF RF POWER (58) Field of Classification Search TRANSMISSION, MODULATION, AND CPC. H04B 1/04; HO3F 1/0266; HO3F 1/56; H03F AMPLIFICATION 3/24: HO3F 3/19 (Continued) (71) Applicant: ParkerVision, Inc., Jacksonville, FL (US) (56) References Cited (72) Inventors: Gregory S. Rawlins, Chuluota, FL U.S. PATENT DOCUMENTS (US); David F. Sorrells, Middleburg, 1,882,119 A 10, 1932 Chireix FL (US) 1946,308 A 2f1934 Chireix (73) Assignee: PARKER VISION, INC, Jacksonville, (Continued) FL (US) FOREIGN PATENT DOCUMENTS (*) Notice: Subject to any disclaimer, the term of this EP O 011 464 A2 5, 1980 patent is extended or adjusted under 35 EP O 471 346 A1 8, 1990 U.S.C. 154(b) by 0 days. (Continued) (21) Appl. No.: 14/797,232 OTHER PUBLICATIONS (22) Filed: Jul. 13, 2015 “Ampliphase AM transmission system.” ABU Technical Review, No. 33, p. 10-18 (Jul 1974). (65) Prior Publication Data (Continued) US 2016/O173144 A1 Jun. 16, 2016 Primary Examiner — Pablo Tran Related U.S. Application Data (74) Attorney, Agent, or Firm — Thomas F. Presson (63) Continuation of application No. 14/541.201 filed on (57) ABSTRACT Nov. 14, 2014, now abandoned, which is a An apparatus, System, and method are provided for energy (Continued) conversion. For example, the apparatus can include a trans impedance node, a reactive element, and a trans-impedance (51) Int. Cl. circuit. The reactive element can be configured to transfer H04B I/04 (2006.01) energy to the trans-impedance node. -

(12) United States Patent (10) Patent No.: US 8,334,722 B2 Sorrells Et Al

USOO8334,722B2 (12) United States Patent (10) Patent No.: US 8,334,722 B2 Sorrells et al. (45) Date of Patent: *Dec. 18, 2012 (54) SYSTEMS AND METHODS OF RF POWER (56) References Cited TRANSMISSION, MODULATION AND AMPLIFICATION U.S. PATENT DOCUMENTS 1,882,119 A 10, 1932 Chireix 1946,308 A 2f1934 Chireix (75) Inventors: David F. Sorrells, Middleburg, FL (US); 2,116,667 A 5, 1938 Chireix Gregory S. Rawlins, Heathrow, FL 2,210,028 A 8/1940 Doherty (US); Michael W. Rawlins, Lake Mary, 2,220,201 A 11/1940 Bliss FL (US) 2,269,518 A 1/1942 Chireix et al. 2,282,706 A 5, 1942 Chireix et al. 2,282,714 A 5/1942 Fagot (73) Assignee: ParkerVision, Inc., Jacksonville, FL 2,294,800 A 9, 1942 Price (US) 2,508,524 A 5/1950 Lang (Continued) (*) Notice: Subject to any disclaimer, the term of this FOREIGN PATENT DOCUMENTS patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. EP O O11 464 A2 5, 1980 (Continued) This patent is Subject to a terminal dis claimer. OTHER PUBLICATIONS "Ampliphase AM transmission system.” ABU Technical Review, No. (21) Appl. No.: 12/216,163 33, p. 10-18 (Jul 1974). (Continued) (22) Filed: Jun. 30, 2008 Primary Examiner — Robert Pascal Assistant Examiner — Khiem Nguyen (65) Prior Publication Data (74) Attorney, Agent, or Firm — Sterne, Kessler, Goldstein & FOX PLLC US 2009/009 1384 A1 Apr. 9, 2009 (57) ABSTRACT Methods and systems for vector combining power amplifica Related U.S. Application Data tion are disclosed herein. -

RCA Ampliphase Transmitter Brochure

Broadcast Ren Systems ROIi Ampliphase what it is how it works why it's better c::::r::::J I I I I I I I I DD • • D D • . ...... ,------4 : : : : : . : : : . www.SteamPoweredRadio.Com Radio Station Equipment Management RCA Broadcast Systems Camden, N.J. 08102 www.SteamPoweredRadio.Com The purpose ot this booklet is to help you understand RCA 's: Ampliphase - what it is, how it works, and why it sounds so much better than ordinary radio broadcast transmitters. We introduced! the first Ampliphase broadcast transmitter in 1957. The Ampliphase system has been in use ever since, first in our 250·, 100- and 50-kW transmitters, and later, in 10- and 5-kW models. T hen, recently, we announced a far reaching simplification-, a completely solid state Ampliphase exciter - heart of all RCA Ampli1Phase transmitters and a new key to broadcast economy. How we combined the many important benefits of Ampliphase in am AM transmitter that is easier to operate, lasts lonl)er, and costs far less to run, 1s the subject of discussion in the next few pages. For your convenience, our material is presented in two sections: Section I An Introduction to Ampliphase .... ...... 4 Section II A Technical Description of T he Ampliphase System ... • ....... 11 www.SteamPoweredRadio.Com SECTION I AN INTRODUCTION TO AMPLIPHASE WHAT IS AMPLIPHASE? Ampliphase is unlike any other method of amplitude modulation. Yet it is quite simple and extremely efficient. It gives us the true high fidelity sound of FM, while retaining the super modulation capabilities of our AM transmitters. Ampliphase uses no audio transformer& of any kind. -

Development of the BBC A.M. Transmitter Network. Rev 6A

Rev 6a (28/5/2007) Development of the BBC A.M. Transmitter Network (compiled by Clive McCarthy) Introduction The British Broadcasting Company, under the chairmanship of Lord Gainford, was formed in October 1922 to set up a broadcasting system as outlined in a plan sanctioned by the Postmaster General in May 1922. This allowed for eight areas of Britain to have a local transmitter, of power 1.5 kW. From this original scheme, the BBC developed the network of high power stations that became so familiar. 1922 to 1929 Eight stations established, having an aerial power of about 1 kW, in main cities. Each city provided programmes from its own studio. Music quality land lines didn’t exist at first, but simultaneous broadcasting started in May 1923 over trunk telephone circuits, with regular London news bulletins to other stations from August 1923. Main stations Tues. November 14th 1922 2LO LONDON (Marconi House) on 369* metres. Wed. November 15th 1922 5IT BIRMINGHAM (Witton) on 420* metres. Wed. November 15th 1922 2ZY MANCHESTER (Trafford Park) on 385* metres. Sun. December 24th 1922 5NO NEWCASTLE-upon-TYNE Tues. February 13th 1923 5WA CARDIFF Tues. March 6th 1923 5SC GLASGOW Wed. October 10th 1923 2BD ABERDEEN Wed. October 17th 1923 6BM BOURNEMOUTH (originally Plymouth) The Radio Times wasn’t published until September 1923, so the wavelengths of the initial services aren’t known. The wavelengths shown thus * are as given in Wireless World November 1972, page 509. (Another source gives 2ZY initially on 375 metres.) Several areas of large population were unable to receive a satisfactory signal on a crystal set, and additional stations were needed. -

Radio Free Europe's Broadcast Operation 8

Vol. No. 94 April, 1957 BROADCAST NEWS published by RADIO CORPORATION OF AMERICA BROADCAST & TELEVISION EQUIPMENT DEPARTMENT CAMDEN. NEW JERSEY In U.S.A. - - - - $4.00 fur 12 issues PRICE In Canada - - - $5.00 for 12 issues C O N T E N T S Page RADIO FREE EUROPE'S BROADCAST OPERATION 8 WHER - MEMPHIS' NEWEST RADIO STATION 20 KSTP INSTALLS RCA 50 -KW AM AMPLIPHASE TRANSMITTER . 26 UNIVERSITY OF GEORGIA TO INSTALL EDUCATIONAL TV . 29 WISH AND WISH -TV, INDIANAPOLIS, INDIANA 30 TRAVELING WAVE ANTENNA 44 NARTB'S ENGINEERING DEPARTMENT 52 NARTB CONVENTION PREVIEW 54 RCA REPRESENTATIVES AND TERRITORIES 56 AGC AUDIO PROGRAM AMPLIFIER 60 A NEW 2 x 2 SLIDE PROJECTOR FOR TELEVISION 64 HOW TO GET TOP PERFORMANCE FROM THE TK -21 ViDICON FILM CHAIN 74 Copyright 1957. Radio Corporation of America. Broadcast & Telerision Equipment Department, Camden, N. J. s *Ty Y. r. Rpt010REE EUROPE'S l'his article, we believe, will be of interest to broadcasters not only because Radio Free IO Europe has been in the headlines recently but also because American personnel super- the operation of this king -size radio system. Broadcasters who have toured the RFE installations in EuropeEur p have found Broadcast them just as interesting as we did on our trip some months ago. At that time we met Part One quite a few broadcast engineers from the U. S. A. who are in key supervisory posi- by PAUL A. GREENMEYER, RFE Installations in Portugal and Germany. in Germany tions for the RFE Managing Editor. BROADCAST NEIVS These engineers and their families were quite enthusiastic about their experiences outside the States. -

A Fully-Integrated Four-Way Outphasing Architecture in Heterogeneously Integrated CMOS/Gan Process Technologies

A Fully-Integrated Four-way Outphasing Architecture in Heterogeneously Integrated CMOS/GaN Process Technologies Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University By Matthew LaRue, B.S.E.E., M.S. Graduate Program in Electrical and Computer Engineering The Ohio State University 2018 Dissertation Committee: Dr. Waleed Khalil, Advisor Dr. Ayman Fayed Dr. Steven Bibyk c Copyright by Matthew LaRue 2018 Abstract The growth of cellular and wireless communications over the last two decades has led to unprecedented congestion of the radio frequency (RF) spectrum. New frequency bands and bandwidth allocations are constantly being opened up to allevi- ate this congestion, but the demand for wireless data is increasing faster than spec- trum availability. Despite fundamental hardware limitations, the complex and rapidly changing wireless environment necessitates three key requirements for RF transmit- ter: frequency-agility, capability of transmitting complex modulation schemes, and power efficiency. In this work, a four-way outphasing architecture is developed for the generation of complex modulated waveforms across a wide RF frequency range. This proposed architecture offers an ACLR improvement equivalent to a 2-bit phase resolution in- crease compared to traditional two-way outphasing architectures. In addition, this architecture is more resilient to PA amplitude and timing mismatch. This architecture is implemented in DARPA's Diverse Accessible Heterogeneous Integration (DAHI) process technology, featuring the heterogeneous integration of 45nm CMOS SOI and 0.2 µm GaN process technologies. The fabricated transmitter achieves greater than 33 dBm output power and a peak transmitter efficiency of greater than 41%.