Programmable Solid State 12AX7 Triode Gain Stage

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Valve Biasing

VALVE AMP BIASING Biased information How have valve amps survived over 30 years of change? Derek Rocco explains why they are still a vital ingredient in music making, and talks you through the mysteries of biasing N THE LAST DECADE WE HAVE a signal to the grid it causes a water as an electrical current, you alter the negative grid voltage by seen huge advances in current to flow from the cathode to will never be confused again. When replacing the resistor I technology which have the plate. The grid is also known as your tap is turned off you get no to gain the current draw required. profoundly changed the way we the control grid, as by varying the water flowing through. With your Cathode bias amplifiers have work. Despite the rise in voltage on the grid you can control amp if you have too much negative become very sought after. They solid-state and digital modelling how much current is passed from voltage on the grid you will stop have a sweet organic sound that technology, virtually every high- the cathode to the plate. This is the electrical current from flowing. has a rich harmonic sustain and profile guitarist and even recording known as the grid bias of your amp This is known as they produce a powerful studios still rely on good ol’ – the correct bias level is vital to the ’over-biased’ soundstage. Examples of these fashioned valves. operation and tone of the amplifier. and the amp are most of the original 1950’s By varying the negative grid will produce Fender tweed amps such as the What is a valve? bias the technician can correctly an unbearable Deluxe and, of course, the Hopefully, a brief explanation will set up your amp for maximum distortion at all legendary Vox AC30. -

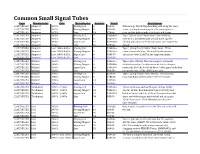

Common Small Signal Tubes

Common Small Signal Tubes Type Manufacturer Date Microphonics Quantity $ Each Descriptions 12AX7/ECC83 Amperex 1970’s Moving-Coil 4 $94.00+ With orange World-Map branding, still using the same 12AX7/ECC83 Amperex 1970’s Moving-Magnet 8 $84.00+ classic tooling & machinery but it’s running faster 12AX7/ECC83 Amperex 1970’s Line 14 $74.00+ now and the tube sounds a bit faster and hotter. 12AX7/ECC83 Amperex 1960’s Moving-Coil 5 $140.00+ Type 2 (The Classic "Bugle Boy" of the 1960’s). 12AX7/ECC83 Amperex 1960’s Moving-Magnet 8 $120.00+ Very nice, a bit lighter with a touch more sparkle 12AX7/ECC83 Amperex 1960’s Super-Line 21 $118.00+ and liquidity than the Telefunken, but still completely 12AX7/ECC83 Amperex 1960’s Line 10 $88.00+ sweet! 12AX7/ECC83 Amperex Late 1940's & 50's Moving Coil 2 $198.00+ Type 1 (Long Plate) 1950’s "Bugle-boys". These 12AX7/ECC83 Amperex Late 1940's & 50's Moving-Magnet 4 $168.00+ came in several styles. The most liquid, sweetest, 12AX7/ECC83 Amperex Late 1940's & 50's Super-Line 4 $148.00 and rarest of the 12AX7 in the Amperex family. 12AX7/ECC83 Amperex Late 1940's & 50's Line 6 $118.00 12AX7/ECC83 Mullard 1960’s Moving-Coil 7 $150.00+ Type 2 (Short Plate) The same magical, warm but 12AX7/ECC83 Mullard 1960’s Moving-Magnet 6 $130.00+ detailed sound as it’s older sister with a touch more 12AX7/ECC83 Mullard 1960’s Super-Line 18 $108.00+ neutrality. -

Silver Luna PRESTIGE

Silver Luna PRESTIGE USER’S MANUAL SAFETY TIPS ______________________________ In order to obtain the highest possible sound reproduction quality and for the sake of your own safety, please kindly refer to the following safety guidelines and please adhere to them: • Never place the Fezz Audio Silver Luna PRESTIGE amplifier near heat sources, such as radiators, heaters or direct sunlight. Ensure adequate ventilation and airflow. • We also warn against exposure of the amplifier to conditions such as very low temperatures and/or high humidity. • During normal operation, the vacuum tubes radiate significant amounts of heat - there is a risk of burns • The amplifier should be plugged directly into a wall socket. If you must use an extension cord, please make sure that it has load parameters sufficient to ensure proper handling of current delivery to the device. • When cleaning, always disconnect the Silver Luna from the power source. Use a dry, soft cloth. Do not use water or cleaning agents. • If your amplifier starts to misbehave or to work incorrectly, if it’s temperature gets too high or you start feeling smoke - immediately disconnect the device from the mains. • Due to the risk of exposure to high voltages – please do not open the lid of the amplifier. ATTENTION: This warning remains in force also in a situation where the device is already disconnected from the wall outlet. • Always replace fuses in accordance with the original, intended specification. • Do not make repairs on your own, or adjustments beyond those as described in this manual. Execution of any unauthorized repairs or modifications of the device result in a loss of warranty. -

Operational Amplifiers: Basic Concepts

Operational Amplifiers: Basic Concepts Prof. Greg Kovacs Department of Electrical Engineering Stanford University Design Note: The Design Process • Definition of function - what you want. • Block diagram - translate into circuit functions. • First Design Review. • Circuit design - the details of how functions are accomplished. – Component selection – Schematic – Simulation – Prototyping of critical sections • Second Design Review. • Fabrication and Testing. EE122, Stanford University, Prof. Greg Kovacs 2 EE122 Parts Kit EE122, Stanford University, Prof. Greg Kovacs 3 Parts Kit Guide LT1175 LT1011 Adjustable Comparator Negative Voltage AD654 V-F Regulator LT1167 Converter Instrum. Sockets Amp 7805 +5V Regulator Yellow LEDs MJE3055 NPN Power Transistor Bright Red LEDs 555 Timer IRLZ34 Logic-Level Power LM334 Temp. Sensor MOSFET (N-Chan) CdS Cell LT1036 Voltage Regulator +12/+5 SFH300-3B LT1033 Voltage Phototransistor Regulator 3A Negative, LT1056 Op- LTC1064-2 Adjustable Amps Switched Capacitor Filter EE122, Stanford University, Prof. Greg Kovacs 4 Each set of five pins are shorted together internally so you can make multiple connections to one i.c. pin or component lead... Each of the long rows of pins is shorted together so you can use them as power supply and ground lines... Protoboards... EE122, Stanford University, Prof. Greg Kovacs 5 USE decoupling capacitors (typically 0.1 µF) from each power supply rail to ground. This is essential to prevent unwanted oscillations. The capacitors locally source and sink currents from the supply rails of the chips, preventing them from “talking” to each other and their own inputs! EE122, Stanford University, Prof. Greg Kovacs 6 Point-To-Point Soldering On A Ground-Planed Board EE122, Stanford University, Prof. -

Silhouette Reference Preamplifier

Silhouette Reference Preamplifier User Guide MADE IN USA © 2014 Raven Audio. All Rights Reserved. Congratulations on your purchase of the 16-tube Silhouette PRODUCT DETAIL Reference Preamplifier with Phono Stage. Locate the preamp with air circulation in mind. It features a Tokyo Ko-on 50k ohm Specifications motorized volume control. The preamplifier is tube-rectified and Inputs: 1/pr balanced XLR, 4/pr single-ended RCA tube controlled, and matches well with a wide variety of Input impedance phono: 47k ohms amplifiers. The phono stage is loaded at 47k ohms for Output impedance line-stage: < 200 ohms high-output MC (moving-coil) or MM (moving-magnet) cartridges. Output gain: +3dB The standard Silhouette Reference Preamplifier gain is 3dB but Dimensions: W 19.4" x D 11.5" x H 8.5" can be modified upon request. Weight: 47lbs Tube Complement 1 x 5Y3/5AR4 – Rectifies tube power supply 1 x 6B4G – Voltage regulator VACUUM TUBE ASSEMBLY DIAGRAM 1 x 6SN7 – Voltage adjuster 1 x OA3 – Reference voltage 2 x 12AT7 – First-stage amplifier 2 x 12AU7 – Current supply for first-stage amplifier 2 x 6DJ8/6922 – Output stage cathode follower 6 x 12AX7 – Phono preamplifier section IMPORTANT: USING YOUR VACUUM TUBE PREAMPLIFIER 6DJ8/ 6DJ8/ 12A X7 12A X7 • Do not unplug an interconnect while the preamplifier is on 5Y3/ 6922 6922 5AR4 6B4G • Do not plug your preamplifier into an ungrounded power socket • Be sure to turn on source components and preamplifier first 12AU7 12AU7 12A X7 12A X7 • Allow them to warm up before turning on your amplifier 0A3 6SN7 • Turn down the volume on the preamp and turn the amp on last 12AT7 12AT7 12A X7 12A X7 • Turn down the volume on the preamp and turn the amp off first • Always use the correct tube types available from Raven - 1 - - 2 - PLEASE READ AND FOLLOW THESE WARNING: Liquid – Avoiding Electrical Shocks Do not operate your Raven Audio device if liquid of any kind is IMPORTANT SAFETY PRECAUTIONS spilled onto or inside the unit. -

The Most Important Tube in Your Amp? the Phase Inverter!

The most important tube in your amp? The Phase inverter! Many people think that V1 (the first gain stage) is the most important tube in an amp. This is true in some cases but not in all cases. V1 (usually the preamp tube closest to the input jack) has the largest impact on your tone and gain but has less impact on your output distortion touch dynamics and output stage distortion than the phase inverter. The phase inverter is generally the preamp tube that is the most close to your output tubes in most amps. Let’s think about this for a moment. Today’s amps come in many “flavors”. There are three basic amp topologies looking at things from one viewpoint. • Non Master volume amplifiers • Master volume amplifiers • Channel switching amplifiers In master volume amps we have pre and post phase inverter master volume controls. These work differently but for this piece of writing I will put them in the same master volume category. Rolling down the master does what? It allows the front end to be driven harder and thus we hear our front end distort. At some point we can drive some amps so hard in the front end that the tone becomes so compressed and distorted that even I can sound like a decent player! Your mistakes are covered up in the mush and distortion of ti all. This distortion is passed down the signal chain where it is reproduced and amplified by the output stage of the amp. This has nothing to do with output stage distortion. -

An Article on Hum in Valve Amplifiers

Page 1 of 28 Valve Amplifier Hum 6 July 2021 Summary Contents Hum sources ............................................................. 1 This article collates information relating to hum and how it is caused within a valve amplifier. Valve Heater Powering ............................................. 2 Directly heated cathodes ............................................ 2 Hum is the addition of any AC mains power related signal to the output signal of the Indirectly heated cathodes ......................................... 2 amplifier. The main hum ingress mechanisms Hum ingress in an input triode stage .......................... 6 relate to valve heater powering, DC power supply ripple and noise, and Neutralisation .............................................................. 7 electrostatic/magnetic coupling. AC used for Powering ............................................... 9 Most commercial valve amplifiers exhibit AC to DC Rectification ................................................ 9 negligible levels of hum, due to careful design Filtering AC from DC ................................................ 11 and manufacture. A faulty or failing part is the usual reason for objectionable hum appearing in Power Distribution .................................................... 13 a commercial amp. Mains side ingress .................................................... 14 Vintage and DIY amps, and amps modified for B+ ripple transfer to speaker output ......................... 14 higher gain, may have noticeable hum, leading Powering -

Driver of Choice: The-ÓÈN7

Published Quarterly , Price $9.00 Driver of Choice: The-ÓÈN7 Mid Priced M r' Octal Licse -Sta e A MA A-4 Kit Review www.vacuumtube.com ISSUE 11 E D I T O R ' S P A G E A N D I N D U S T R Y N E W S New tubes from Sovtek VT V Issue # 11 New Sensor Corporation, New York, Table of Contents: New York has recently introduced a number of tubes for the guitar amplifier and hi-fi applications. Their new KT66 6SN7 Driver of Choice 3 and KT88 have the famous"coke bottle" shape reminiscent of the classic Tung-Sol Listening to 6SN7s 9 6550. According to New Sensor's press release, improve Octal Line Stage Project 10 ments have been made in grid and Richardson Electronics 11 plate materials used in their out- New 300B from Svetlana Mid-Priced Vintage Hi-Fi 14 put tubes. Svetlana Electron Devices, Huntsville, Computing with Tubes 20 The new Sovtek Alabama, has announced the availability 6550 comes in of their high-quality new SV300B power Tube Dumpster: 6688 21 two versions, the triode and its beautiful new packaging. 6550WD with a Russian engineers at Svetlana have worked ASUSA A-4 Kit Review 22 plastic base and hard to bring the quality construction, the 6550WE with materials, processing, aging and classic OTL Headphone Amp 24 the familiar metal sound to their 300B type. The plate is ring base. A new, carbonized, high-purity nickel and the fil- VTV Listens to Capacitors 26 octal based, ament oxide coating duplicates the origi- directly heated tri- nal mixture. -

BF/SF Deluxe Reverb

271962950 BF/SF Deluxe Reverb Production years: 1964 -1967 “blackface” circuits AA763, AB763, AB868 (CBS) 1967 -1977 “silverface” circuits AB763, A1172 and A1270 1977-1979 “silverface” circuit with Push-pull volume boost. Tube layout AA763/AB763 Tube layout (Seen from behind, V1 is to the right side) V1 12ax7 = Preamp normal channel V2 12ax7 = Preamp vibrato channel V3 12at7 = Reverb send V4 12ax7 = 1/2 Reverb recovery and 1/2 gain stage for vibrato channel V5 12ax7 = Vibrato V6 12at7 = Phase inverter V7 6V6 = Power tube #1 V8 6V6 = Power tube #2 V9 GZ34 = Rectifier tube Summary The Deluxe Reverb 1×12″ has for decades been one of the most popular amps among all Fender amps, and its popularity is still growing as the demand for low wattage tube amps increases. The combination of size, weight and performance makes the Deluxe Reverb a true road warrior on gigs and practise. Since the year 2002 we have observed, by monitoring the amp market on US ebay, that low wattage amps have increased dramatically in popularity. Nowadays (2012) you can score a big 6L6 vintage Fender amp for the same price as a Deluxe Reverb or Princeton Reverb. We find it irrational. The PA was invented long time before that and guitar tones containing fuzz and distortion have been around since the sixties- seventies. Why has the desire for low wattage amps with 20-25 watts of tube power come up so late? Both the Deluxe Reverb (DR) and Princeton Reverb (PR) “survived” the CBS silverface periods with minor changes. Many people consider the silverface amps just as sonically good as the blackface models. -

NEW! NEW! BLACKSTAR HT VENUE SERIES TUBE AMPLIFIERS This Series Has a Tube Amp to Suit Every Performance FENDER G-DEC JUNIOR CARBON GUITAR Situation

GUITAR AMPLIFIERS 429 NEW! NEW! BLACKSTAR HT VENUE SERIES TUBE AMPLIFIERS This series has a tube amp to suit every performance FENDER G-DEC JUNIOR CARBON GUITAR situation. Authentic ‘boutique’ cleans and super high gain AMPLIFIER This mini version of the original G-DEC has overdrives are combined in this line. Speaker cabinets are built-in backing tracks in styles including rock, blues, jazz, all equipped with Celestion drivers and have been voiced metal, country, Latin, hip hop and others, and a variety of to work with the HT Venue amplifiers, as well as a wide HTCLUB40C amp and effects types can be mixed and matched for a range of other products. All the cabs have finger-locked (comb) joints, heavy-duty complete musical experience. wiring and a cool vintage styling. ITEM DESCRIPTION PRICE ITEM DESCRIPTION PRICE G-DEC-JR-CARBON.... Guitar combo amp, 15W, 1x8", AUX input, Headphone jack, MIDI out, Carbon Tweed Textured Vinyl covering .........................159.99 HT Venue Series Amplifiers HT100H ..................... 100W tube head ..........................................................................849.99 CHAMPION 600 HTSTUD20H ...............20W tube head ............................................................................499.99 HTSTAGE60C ............. 2x12" 60W tube combo ............................................................... 899.99 HTSOLO60C ...............1x12" 60W tube combo ............................................................... 799.99 HTCLUB40C ...............1x12" 40W tube combo .............................................................. -

Section H: Op Amp History

OP AMP HISTORY H Op Amp History 1 Introduction 2 Vacuum Tube Op Amps 3 Solid-State Modular and Hybrid Op Amps 4 IC Op Amps 1 Op Amp Basics 2 Specialty Amplifiers 3 Using Op Amps with Data Converters 4 Sensor Signal Conditioning 5 Analog Filters 6 Signal Amplifiers 7 Hardware and Housekeeping Techniques OP AMP APPLICATIONS OP AMP HISTORY INTRODUCTION CHAPTER H: OP AMP HISTORY Walt Jung The theme of this chapter is to provide the reader with a more comprehensive historical background of the operational amplifier (op amp for short— see below). This story begins back in the vacuum tube era and continues until today (2002). While most of today's op amp users are probably somewhat familiar with integrated circuit (IC) op amp history, considerably fewer are familiar with the non-IC solid-state op amp. And, even more likely, very few are familiar with the origins of the op amp in vacuum tube form, even if they are old enough to have used some of those devices in the 50's or 60's. This chapter of the book addresses these issues, with a narrative of not only how op amps originated and evolved, but also what key factors gave rise to the op amp's origin in the first place. 1 A developmental background of the op amp begins early in the 20th century, starting with certain fundamental beginnings. Of these, there were two key inventions very early in the century. The first was not an amplifier, but a two-element vacuum tube-based rectifier, the "Fleming diode," by J. -

A Low-Drift Integrating Amplifier

Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 1954 A low-drift integrating amplifier. Porter, W. R. Massachusetts Institute of Technology http://hdl.handle.net/10945/14382 YO Copy No. 58 Servomechanisms Laboratory Electrical Engineering Department Massachusetts Institute of Technology DoI.C. 6897 A LOW-DRIFT INTEGRATING AMPLIFIER Technical Memorandum 6897-TM-18 Contract NOrd 11799 September 9, 195^ ABSTRACT The need occasionally arises for a device performing an integration; situations may arise where limited size is a design objective,, The integrating feedback amplifier presents attractive possibilities. It is critically assessed. A first model was constructed to focus more clearly the problems of drift and miniaturization possibilities. Exper- ience enabled construction of a superior model with an output drift of less than 100 millivolts during hour-long trials as an integrator with a gain of 1 volt / sec /volt , Operation with 4^00 cycle filament supply was satisfactory. Power supply fluctuations produced equivalent spurious signals decreased in a ratio of 1 ,000 : 1. To combat zero-drift, the advanced technique of auto- matic stabilization (Goldberg Circuit) is employed, requiring consideration of miniature synchronous converters. To miniatur ize the computing condenser without sacrifice of drift or quality of integration, grid current is controlled. The power supply requirements are considered simple for a -100 volt output range. This was accomplished without sacrifice of gain by the use of gas-discharge tube coupling at low currents. All stages are stabilized to minimize effects of supply variation. The resulting high-gain low-drift integrating ampli- fier built in terms of miniature components is recommended as a prototype for further development in subminiature form.