Silicon Glen 1 Silicon Glen

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Certain Erasable Programmable Read-Only Memories, Components

In the Matter of CERTAIN ERASABLE PROGRAM- MABLE READ-ONLY MEM- ORIES, COMPONENTS THEREOF, PRODUCTS CONTAINING SUCH MEM- ORIES, AND PROCESSES FOR MAKING SUCH MEMORIES Investigation No, 337-TA-276 USITC PUBLICATION 21 96 MAY 1989 United States International Trade Commission Washington, DC 20436 UNITED STATES INTERNATIONAL TRADE COMMISSION COMMISSIONERS Anne E. Brunsdale, Chairman Ronald A. Cass, Vice Chairman Alfred E. Eckes Seeley G. Lodwick David Be Rohr ? Don E. Newquist Address all communications to Kenneth R. Mason, Secretary to the Commission United States International Trade Commission Washington, DC 20436 h -.. UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C. 20436 -. -r -_ J -. In the Matter of 1 4 1 CERTAIN ERASABLE PROGRAMMABLE 1 Investigation No. 337-TA-27g READ ONLY MEMORIES, COMPONENTS THEREOF, PRODUCTS CONTAINING SUCH 1 MEMORIES, AND PROCESSES FOR MAKING 1 SUCH MEMORIES 1 NOTICE OF ISSUANCE OF LIMITED EXCLUSION ORDER AND CEASE AND DESIST ORDERS AGENCY: U.S. International Trade Commission. ACTION: Notice, SUMMARY: Notice is hereby given that the Commission has issued a limited exclusion order in the above-captioned investigation prohibiting the unlicensed importation of certain erasable programable read only memories (EPROMs) manufactured abroad by Hyundai Electronics Industries Co., Ltd. as a contractor for General Instrument Corporation and/or Microchip Technology, Inc., whether in the form of single-unit packages, incorporated into a carrier of any form, mounted on a circuit board of any configuration, or contained in certain products, except for EPROMs which are the subject of a consent order issued by the Commission on August 25, 1988. In addition, the order prohibits the unlicensed importation of certain EPROMs manufactured abroad for Atmel Corporation, whether in the form of single-unit packages, incorporated into a carrier of any form, mounted on a circuit board of any configuration. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

MARKINCH Conservation Area Appraisal and Management Plan

MARKINCH Conservation Area Appraisal and Management Plan DEVELOPMENT SERVICESS MARKINCH CONSERVATION AREA APPRAISAL AND MANAGEMENT PLAN CONTENTS 1. Introduction and Purpose 1.1 Conservation Areas 1.2 The Purpose of this Document 2. Historic Development 2.1 Origins of Settlement 2.2 Settlement Development 2.3 Archaeological and Historical Significance of the Area 3. Townscape Analysis 3.1 Location and Setting 3.2 Topography and Street Pattern 3.3 Building Styles and Materials 3.4 Listed Buildings 3.5 Trees and Landscape 3.6 Activity and Movement 3.7 Public Realm 3.8 Negative Features 4. Conservation Management Strategy 4.1 Management Plan 4.2 Planning Policy 4.3 Supplementary Planning Guidance 4.4 Article 4 Directions 4.5 Monitoring and Review 4.6 Further Advice Appendix 1: Markinch Article 4 Directions Appendix 2: Table of Listed Buildings in the Conservation Area 2 3 1. Introduction and Purpose 1.1 Conservation Areas In accordance with the provisions contained in the Planning (Listed Buildings and Conservation Areas) (Scotland) Act 1997 all planning authorities are obliged to consider the designation of conservation areas from time to time. Markinch Conservation Area is 1 of 48 Conservation Areas located in Fife. These are all areas of particular architectural or historic value, the character or appearance of which it is desirable to preserve or enhance. Fife Council is keen to ensure that the quality of these areas is maintained for the benefit of present and future generations. Conservation area designation is not a means to preserve an area without change, but there is a joint responsibility between residents and the council to ensure that change is not indiscriminate or damaging, and that the unique character of each area is respected. -

Silicon Cities Silicon Cities Supporting the Development of Tech Clusters Outside London and the South East of England

Policy Exchange Policy Silicon Cities Cities Silicon Supporting the development of tech clusters outside London and the South East of England Eddie Copeland and Cameron Scott Silicon Cities Supporting the development of tech clusters outside London and the South East of England Eddie Copeland and Cameron Scott Policy Exchange is the UK’s leading think tank. We are an educational charity whose mission is to develop and promote new policy ideas that will deliver better public services, a stronger society and a more dynamic economy. Registered charity no: 1096300. Policy Exchange is committed to an evidence-based approach to policy development. We work in partnership with academics and other experts and commission major studies involving thorough empirical research of alternative policy outcomes. We believe that the policy experience of other countries offers important lessons for government in the UK. We also believe that government has much to learn from business and the voluntary sector. Trustees Daniel Finkelstein (Chairman of the Board), David Meller (Deputy Chair), Theodore Agnew, Richard Briance, Simon Brocklebank-Fowler, Robin Edwards, Richard Ehrman, Virginia Fraser, David Frum, Edward Heathcoat Amory, Krishna Rao, George Robinson, Robert Rosenkranz, Charles Stewart-Smith and Simon Wolfson. About the Authors Eddie Copeland – Head of Unit @EddieACopeland Eddie joined Policy Exchange as Head of the Technology Policy Unit in October 2013. Previously he has worked as Parliamentary Researcher to Sir Alan Haselhurst, MP; Congressional intern to Congressman Tom Petri and the Office of the Parliamentarians; Project Manager of global IT infrastructure projects at Accenture and Shell; Development Director of The Perse School, Cambridge; and founder of web startup, Orier Digital. -

131A South Street, St Andrews, KY16 9UN Offers Over £300,000 131A South Street St Andrews KY16 9UN

OFFICES THROUGHOUT FIFE Cupar | St Andrews | Auchtermuchty | Glenrothes 131a South Street, St Andrews, KY16 9UN Offers over £300,000 131a South Street St Andrews KY16 9UN OFFERS OVER £300,000 131A South Street is an '18th century fully renovated first floor, two-bedroom, apartment in central St Andrews. This light and sunny apartment occupies the first floor of a C-listed property in a conservation area. The pantile-roof property which dates from the 18th century. It has been fully renovated and comes to the market in walk-in condition. It is extremely well positioned for all local amenities. Access to the property is via a shared entrance and pend on South Street. Intercom door- bell. The private front-door leads to a modern, open-plan kitchen/ dining/ living room with original solid wood flooring. The main room has a large sash and case window with a view over South Street. Roof area with space for window boxes. Fully fitted kitchen with white high-gloss units, solid oak worktop, built-in electric oven and hob and integrated fridge with freezer compartment. Two bedrooms with large, sash and case windows and original solid wood flooring. Modern bathroom with electric shower, basin, WC and contemporary vinyl flooring. Utility cupboard with plumbing for washing machine. Modern electric heating with thermostatic control throughout. • Town Centre Apartment INCLUDED Integrated appliances included in marketing price • C- Listed and Conservation Area SERVICES • Lounge/Kitchen/Diner Water • 2 Bedrooms Electricity Drainage • Shower Room • Double -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

St Andrews Hospital

) 3 1 0 2 r e b m e v o N ( 5 e u s s I k u . v o g . e f i f @ s e c i v r e s . n o i t a t r o p s n a r t : l i a m - e ☎ ) 5 0 9 2 4 4 . t x e ( 5 5 5 5 5 5 1 5 4 3 0 o f n i . s u b s u l p . w w w . r o t c o d s u B s u l P y b s l a r r e f e R r u o y k s a e s a e l p n o i t a m r o f n i r e h t r u f r o F . y l n o r o t c o d T L 5 7 Y K , s e h t o r n e l G h s i t t o c S e h T . e c i v r e S y c n e g r e m E - n o N e c i v r e S e c n a l u b m A , t e e r t S h t r o N , e s u o H e f i F , l i c n u o C e f i F , n o i t a t r o p s n a r T f o d a e H e h T o l s y h r : l i a m - e k u . -

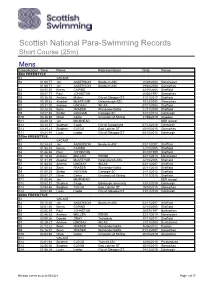

Para Swimming Records Short Course As At

Scottish National Para-Swimming Records Short Course (25m) Mens Classification Time Name Representation Date Venue 50m FREESTYLE S1 VACANT S2 01:08.77 Jim ANDERSON Broxburn ASC 26/08/2004 Manchester 01:08.77 Jim ANDERSON Broxburn ASC 19/04/2008 Glenrothes S3 00:55.55 Kenny CAIRNS 23/10/2005 Sheffield S4 00:47.77 Paul JOHNSTON 26/04/1997 Glenrothes S5 00:36.06 Andrew Mullen City of Glasgow ST 11/11/2017 Sheffield S6 00:39.82 Alasdair McARTHUR Helensburgh ASC 10/12/2005 Glenrothes S7 00:31.20 Andrew LINDSAY INCAS 07/11/2004 Sheffield S8 00:28.08 Sean FRASER Warrender Baths 22/11/2009 Sheffield S9 00:27.58 Stefan HOGGAN Carnegie SC 13/12/2013 Edinburgh S10 00:26.59 Oliver Carter University of Stirling 21/09/2019 Glasgow S11 00:29.74 Jim MUIRHEAD BBS record S12 00:24.37 Stephen Clegg City of Sunderland 07/12/2018 Edinburgh S13 00:25.23 Stephen CLEGG East Lothian ST 25/10/2015 Glenrothes S14 00:24.94 Louis Lawlor City of Glasgow ST 08/12/2018 Edinburgh 100m FREESTYLE S1 VACANT S2 02:24.63 Jim ANDERSON Broxburn ASC 03/11/2007 Sheffield S3 01:58.05 Kenny CAIRNS 22/10/2005 Sheffield S4 01:46.86 Paul JOHNSTON 30/10/1999 Sheffield S5 01:18.26 Andrew MULLEN REN96 22/11/2014 Manchester S6 01:31.89 Alasdair McARTHUR Helensburgh ASC 22/10/2005 Sheffield S7 01:08.00 Andrew LINDSAY INCAS 03/11/2007 Sheffield S8 01:00.64 Sean FRASER Warrender Baths 20/11/2010 Sheffield S9 01:00.35 Stefan HOGGAN Carnegie SC 24/11/2012 Sheffield S10 00:57.27 Oliver Carter University of Stirling 11/11/2018 Sheffield S11 01:05.46 Jim MUIRHEAD BBS record S12 00:52.31 Stephen -

GRI-Rapport 2016:2 Bank Management

Gothenburg Research Institute GRI-rapport 2016:2 Bank Management Banks and their world view contexts Sten Jönsson © Gothenburg Research Institute All rights reserved. No part of this report may be repro- duced without the written permission from the publisher. Gothenburg Research Institute School of Business, Economics and Law at University of Gothenburg P.O. Box 600 SE-405 30 Göteborg Tel: +46 (0)31 - 786 54 13 Fax: +46 (0)31 - 786 56 19 E-post: [email protected] ISSN 1400-4801 Layout: Henric Karlsson Banks and their world view contexts By Sten Jönsson Gothenburg Research Institute (GRI) School of Business, Economics and Law University of Gothenburg Contents Introduction 8 1. Preliminaries 13 1.1. Theoretical orientation 13 1.2. What is a bank anyway? 15 1.3. The changing nature of arbitrage 16 1.4. A quick tour of the world views that set the stage for banking 18 2. Greed, arbitrage, and decency in action 22 2.1. Greed – the original sin! 22 2.2. An overview of wealth and the afterlife during the first centuries AD 24 3. Scholasticism – guiding individuals to proper use of their free will 26 4. The most prominent banks – watched by the scholastics 32 4.1. Medici 32 4.2. Fugger 37 5. Mercantilism – the origins of political economy and, consequently, of economic policy 42 5.1. The glory and decline of merchant banks 45 6. Neoliberalim started with the Austrian School 59 6.1. Modernism and crumbling empires 59 6.2. The context in which the Austrian school developed 61 6.3.