Synchronizing Mechatronic Systems in Real-Time Using Fpgas And

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Introduction to Real-Time Ethernet II

the EXTENSION JULY–AUGUST A Technical Supplement to Control Network Volume 5 Issue 4 © 2004 Contemporary Control Systems, Inc. Introduction to Real-Time Ethernet II By Paula Doyle, a doctoral researcher with the Circuits and Systems Research Centre at the University of Limerick in Ireland INTRODUCTION IEEE 1588 defines two separate types of clocks: In “Real-Time Ethernet I”, we introduced the basic ordinary and boundary. Boundary clocks (BC) are concepts of Ethernet’s capacity to deliver a real-time employed in devices such as hubs or switches—where (RT) communication system. “Real-Time Ethernet II” more than one PTP communication path (port) exists. introduces some of the RT solutions available to Ordinary clocks exist in devices having a single port— e.g., normal network devices. Each BC port can act as industry today*: PROFInet, EtherCAT and ETHERNET Powerlink. It also provides an introduction to a single a master or ordinary clock in its own segment. standard, IEEE 1588 that is growing in popularity PTP is for networks that support multicasting but amongst RT Ethernet developers to provide sub- keep multicasts within a subnet and where each local microsecond synchronization accuracy of distributed clock fulfills exacting requirements. The grandmaster clocks over Ethernet. clock (GMC) is the best clock in the system—with the best inherent stability, accuracy, resolution, etc. * EtherNet/IP is included in the full article available at defined by the standard [2]. The Best Master Clock http://www.ccontrols.com/pdf/volume5n4.pdf Algorithm (BMC), run by every live node, determines IEEE 1588 clock quality. Within each subnet, the BMC determines the master clock; in a single-subnet system the master IEEE 1588 [1] specifies “A protocol to synchronize is the GMC. -

Xilinx Ethernet POWERLINK Solution Sell Sheet

Xilinx Ethernet POWERLINK Xilinx Ethernet POWERLINK Solution: Synchronizing High-Performance Control Systems The Challenges to Industrial Ethernet POWERLINK is an open, software-based Real Time Communication Network Design protocol compatible with standard Ethernet hardware. Both the Controlled Nodes (slaves) and the Managing Nodes (masters) can be built on standard Ethernet • Provide high performance, cost- components for 100 Mbits/s Ethernet. effective Ethernet-based communication technology for control applications Designed For Ultimate Flexibility POWERLINK's flexibility results is standardization, ease of service and maintenance • Integrate design changes to meet and reduced implementation and operating costs. POWERLINK is ideal for future specifications synchronization of high performance motion control systems. The POWERLINK IP developed by port GmbH adheres to Ethernet POWERLINK protocol. Its four variants • Bridge between multiple interface are designed for ultimate flexibility on Xilinx FPGAs. protocols and support various protocol technologies with a common hardware Integrates with All Standard Ethernet Protocols design POWERLINK can be implemented using any standard Ethernet hardware. While supporting all topologies, it offers complete operational conformance between systems that adhere to Ethernet communication systems. The Xilinx Ethernet POWERLINK Solution Performance Now and in the Long-Term POWERLINK meets the highest requirements of hard Real Time performance • Provide hardware necessary to achieve and determinism. POWERLINK is poised to support transmission rates 10x higher best Real Time behavior, short delays (1000 Mbits/s) than today with Gigabit Ethernet ported to FPGAs. and fast response times POWERLINKsafety and Security • Implement multiple design variants in POWERLINKsafety is an open real time safety protocol developed by Ethernet the FPGA POWERLINK Standardization Group (EPSG). -

The Future of CAN / Canopen and the Industrial Ethernet Challenge by Wilfried Voss, President Esd Electronics, Inc USA

The Future of CAN / CANopen and the Industrial Ethernet Challenge by Wilfried Voss, President esd electronics, Inc USA Industrial Ethernet technologies are a formidable challenge to CANopen as the low-cost industrial networking technology of choice. Ethernet technologies will eventually replace the majority of CANopen applications, at least in regards to new developments. For many years, Controller Area Network (CAN) and CANopen, a higher-layer protocol based on CAN, represented the best choice for low-cost industrial embedded networking. However, since the official introduction of CAN in 1986, there has been a quest to replace CAN and CANopen to overcome the most obvious shortcomings such as limited baud rate and limited network length. Industrial Ethernet technologies are currently the most formidable challenge to CANopen as the low-cost industrial networking technology of choice. Ethernet technologies will eventually replace the majority of CANopen applications, at least in regards to new developments, starting at this very moment in certain areas such as industrial control including motion control and, especially, robotics. Ironically, CAN - the underlying hardware layer of CANopen - has a far greater lifetime expectancy in the North American market than CANopen as a higher layer protocol. However, there can be too much of a good thing, and that is definitely the case when it comes to Ethernet-based fieldbus technologies. There are currently more than 20 different industrial Ethernet solutions available, all with their distinctive advantages and disadvantages, making a pro/contra decision difficult. The major question, besides the technical aspect, is which of these technologies will survive in the market, and how do they support the current need for control components. -

Study on Real‑Time Industrial Control Networks

This document is downloaded from DR‑NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore. Study on real‑time industrial control networks Wu, Xuepei 2019 Wu, X. (2019). Study on real‑time industrial control networks. Doctoral thesis, Nanyang Technological University, Singapore. https://hdl.handle.net/10356/90139 https://doi.org/10.32657/10220/48429 Downloaded on 11 Oct 2021 09:28:10 SGT Acknowledgments Undertaking doctoral study has been a truly life-changing experience for me and it would never have been possible to take this work to completion without the guidance and support that I received from many people. Firstly, I would like to express my sincere appreciation and respect to my supervisor, Professor Xie Lihua, for his professional guidance and valuable suggestions throughout my time as his student. I could not imagine having had a better advisor and mentor for my research work. I owe the deepest gratitude to my family for their encouragement and love. My wife and my parents have been extremely supportive of me throughout the entire study and have made countless sacrifices to help me get to this point. I also thank the staff and students in the Internet of Things Laboratory of Nanyang Technological University for their help. Lastly, I gratefully acknowledge the funding received from the Industrial Postgraduate Programme of the Singapore Economic Development Board (grant number S11-1669- IPP). i Abstract Boosted by business trends such as Industry 4.0, Industrial Internet of Things (IIoT) solutions such as real-time Ethernet and wireless technologies have been increasingly de- ployed in the industrial automation sector. -

Sercos III Slave for Am437x — Communication Development Platform

TI Designs Sercos III Slave For AM437x — Communication Development Platform TI Designs Design Features Industrial Ethernet for Industrial Automation exists in • Sercos III Slave Firmware for PRU-ICSS With more than 20 industrial standards. Some of the well- Sercos MAC-Compliant Register Interface established real-time Ethernet protocols like EtherCAT, • Board Support Package and Industrial Software EtherNet/IP, PROFINET, Sercos III, and PowerLink Development Kit Available From TI and Third-Party require dedicated MAC hardware support in terms of Stack Provider FPGA or ASICs. The Programmable Real-Time Unit inside the Industrial Communication Subsystem (PRU- • Development Platform Includes Schematics, BOM, ICSS), which exists as a hardware block inside the User’s Guide, Application Notes, White Paper, Sitara processors family, replaces FPGA or ASICS Software, Demo, and More with a single chip solution. This TI design describes • PRU-ICSS Supports Other Industrial the Sercos III slave solution firmware for PRU-ICSS. Communication Standards (For Example, EtherCAT, PROFINET, EtherNet/IP, Ethernet Design Resources POWERLINK, Profibus) • PRU-ICSS Firmware is Sercos III Conformance TIDEP0039 Design Folder Tested TMDXIDK437X Tools Folder AM4379 Product Folder Featured Applications TIDEP0001 Tools Folder • Factory Automation and Process Control TIDEP0003 Tools Folder • Motor Drives TIDEP0008 Tools Folder TIDEP0010 Tools Folder • Digital and Analog I/O Modules TIDEP0028 Tools Folder • Industrial Communication Gateways • Sensors, Actuators, and Field Transmitters ASK Our E2E Experts WEBENCH® Calculator Tools Sitara AM437x ARM Cortex-A9 PRU-ICSS processor PHY Sercos III application/profile/ Slave MAC stack PHY An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. -

Industrial Ethernet Technologies Page 1 © Ethercat Technology Group, January 2011

Industrial Ethernet Technologies Page 1 © EtherCAT Technology Group, January 2011 Industrial Ethernet Technologies: Overview Approaches Modbus/TCP Ethernet/IP Powerlink PROFINET SERCOS III EtherCAT Summary © EtherCAT Technology Group Industrial Ethernet Technologies Editorial Preface: This presentation intends to provide an overview over the most important Industrial Ethernet Technologies. Based on published material it shows the technical principles of the various approaches and tries to put these into perspective. The content given represents my best knowledge of the systems introduced. Since the company I work for is member of all relevant fieldbus organizations and supports all important open fieldbus and Ethernet standards, you can assume a certain level of background information, too. The slides were shown on ETG Industrial Ethernet Seminar Series in Europe, Asia and North America as well as on several other occasions, altogether attended by several thousand people. Among those were project engineers and developers that have implemented and/or applied Industrial Ethernet technologies as well as key representatives of some of the supporting vendor organizations. All of them have been encouraged and invited to provide feedback in case they disagree with statements given or have better, newer or more precise information about the systems introduced. All the feedback received so far was included in the slides. You are invited to do the same: provide feedback and – if necessary – correction. Please help to serve the purpose of this slide set: a fair and technology driven comparison of Industrial Ethernet Technologies. Nuremberg, January 2011 Martin Rostan, [email protected] Industrial Ethernet Technologies Page 2 © EtherCAT Technology Group, January 2011 Industrial Ethernet Technologies: Overview Approaches Modbus/TCP Ethernet/IP Powerlink PROFINET SERCOS III EtherCAT Summary © EtherCAT Technology Group Industrial Ethernet Technologies All Industrial Ethernet Technologies introduced in this presentation are supported by user and vendor organizations. -

ETHERNET Powerlink Real-Time Industrial ETHERNET Servo Drives & Controllers

aerospace climate control electromechanical filtration fluid & gas handling hydraulics pneumatics process control sealing & shielding ETHERNET Powerlink Real-Time Industrial ETHERNET Servo Drives & Controllers Parker Hannifin Corporation • Electromechanical Automation Division • 800-358-9070 • www.parkermotion.com 1 ETHERNET Powerlink MotionBus Systems from the Global Leader in Motion Control Parker understands the challenges facing OEMs in high- tech industries. To help meet their challenges, Parker’s team of highly experienced motion system designers use a systematic project management process to deliver the most advanced linear motion technologies available. For all industrial automation solutions, Parker Automation combines speed, accuracy and high-load capability to give machine builders and OEMs a competitive edge. Medical device manufacturers Parker is the only supplier that utilize Parker’s integrated can provide complete technical automation solutions specifically and engineered solutions designed to reduce time-to- to OEMs for any packaging market and engineering costs requirement. Parker’s innovative while improving compliance with engineering, breadth of line, today’s stringent government worldwide distribution, and regulations. outstanding customer service set the standard for the industrial For semiconductor manufacturers, motion market in all these areas: our extensive expertise in vacuum preparation, cleanroom • Application analysis facilities and large-format • Engineering assistance systems enable us to design and • -

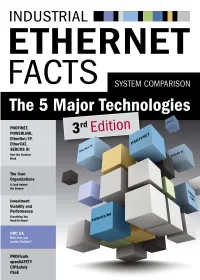

Industrial Ethernet Facts Compares PROFINET (RT, IRT), POWERLINK, Ethernet/IP, Ethercat, and SERCOS III, I.E

Luca Lachello Wratil Peter Anton Meindl Stefan Schönegger Singh Karunakaran Bhagath Huazhen Song Stéphane Potier Preface Outsiders are not alone in finding the world of Industrial Ethernet somewhat confusing. Experts who examine the matter are similarly puzzled by a broad and intransparent line-up of competing systems. Most manufacturers provide very little information of that rare sort that captures techni- cal characteristics and specific functionalities of a certain standard in a way that is both com- prehensive and easy to comprehend. Users will find themselves even more out of luck if they are seeking material that clearly compares major systems to facilitate an objective assessment. We too have seen repeated inquiries asking for a general overview of the major systems and wondering “where the differences actually lie”. We have therefore decided to dedicate an issue of the Industrial Ethernet Facts to this very topic. In creating this, we have tried to remain as objective as a player in this market can be. Our roundup focuses on technical and economic as well as on strategic criteria, all of which are relevant for a consideration of the long-term via- bility of investments in Industrial Ethernet equipment. The arguments made in this publication were advanced and substantiated in numerous conversations and discussions with developers and decision-makers in this field. We have made every attempt to verify claims whenever practically possible. This document must not be modified Despite all our efforts, though, we were unable to ascertain exact, verifiable information on without prior consent of its publisher. some aspects, which prompts us to ask for your help: if you would like to propose any Passing on the document in its entirety amendments or corrections, please send us an e-mail or simply give us a call. -

Basics Why Industrial Ethernet ?

System Overview POWERLINK Basics Why Industrial Ethernet ? Over the course of the last two decades, it has combination with an Internet protocol like TCP/IP is become hard to keep track of the numerous fi eld- unsuitable for data transmission in hard real-time. bus systems that have been developed in the auto- Data traffi c can be delayed in unforeseeable ways mation industry specifi cally for purposes of process due to the CSMA/CD mechanism (Carrier Sense and factory production control. Yet there remain Multiple Access/Collision Detection). An integral various restraints that are impeding their perfor- part of the Ethernet standard IEEE 802.3, that mance. Demand has therefore become more mechanism helps prevent data collisions on the pressing for a reliable communication system that bus that can occur in Ethernet environments due would offer high fl exibility and across-the-board to the particular nature of Ethernet transmissions. compatibility. A new solution in this vein was also In order to develop Ethernet-based, but real-time expected to allow for ongoing improvements and capable fi eldbuses, manufacturers have pursued future upgrades. Ethernet fi rst rose to that chal- various approaches in their efforts to eliminate such lenge: it was a tried and tested technology that delays. These solutions are commonly referred to as was free of patents and was widely standardized. “Industrial Ethernet” technologies. This booklet will Moreover, it had great potential to serve as a introduce you to POWERLINK, which has become consistent, integrated communication solution, i.e. one of the most successful Industrial Ethernet allow for an interconnection of the control, process, systems in the world today. -

Powerlink Facts 2 07 E.Pdf

ETHERNET November 2007 / POWERLINK Issue 2 The Magazine for the Standard in Industrial Ethernet Volume 2, Volume FACTS Central control? Decentral control? In control in any way. Just give it a try POWERLINK starter kits from IXXAT, port and SYS TEC Innovative and tailor- made Encoder solutions from POSITAL Intuitive approach Lenze's L-force Engineer features great usability POWERLINK application performance 2 PRODUCT NEWS 2/2007 POSITAL: Perfectly prepared for POWERLINK – innovative encoder solutions tailored to your needs ■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■ A highly specialized manufacturer these devices due to an innovative, of absolute rotary encoders and incli- patented technology based on a nometers, POSITAL GmbH provides Wiegand wire around which an electric customers and end users with en- coil is wound. This component draws coder solutions that can be integrated on energy from the turning motion to into almost any widely used bus measure turns. Neither continual system. Highlights among the product turns nor a minimal rotation speed line-up include the extremely com- are required for this feature. MCD pact, cost-efficient MAGNETOCODE encoders are available as hollow (MCD) multi-turn encoders, which shaft and solid shaft versions. They POSITAL's extremely operate without an external source of provide IP64 protection and are compact MCD rotary encoders current. These encoders determine only 36.5 mm wide. position values by means of an inte- grated Hall effect sensor that samples Other key product lines include the magnetic field of a permanent POSITAL's OPTOCODE optoelectronic magnet fixed to the shaft. This single- rotary encoders, which are also avail- All types are equipped with standard can be configured with TCP/IP control turn sensor system achieves 12 bit able with automatic protocol switching M12 plugs. -

Industrial Ethernet Communication Protocols

WHITE PAPER Industrial Ethernet Communication Protocols Contents Executive Summary . 1 Industrial Slave Equipment �������������������������������������������������������������������������������������������������������������������������1 Industrial Automation Components . 2 Legacy Industrial Communication Protocols. 2 PROFIBUS �������������������������������������������������������������������������������������������������������������������������������������������������������3 CAN- ����������������������������������������������������������������������������������������������������������������������������������������������������������������3 Modbus . 3 CC-Link . 3 Descriptions of Industrial Ethernet Communication Protocols. 3 Ethernet/IP ����������������������������������������������������������������������������������������������������������������������������������������������������6 PROFINET . 6 EtherCAT. 6 SERCOS III �������������������������������������������������������������������������������������������������������������������������������������������������������7 CC-Link IE �������������������������������������������������������������������������������������������������������������������������������������������������������7 Powerlink �������������������������������������������������������������������������������������������������������������������������������������������������������7 Modbus /TCP . 8 Future Trends �������������������������������������������������������������������������������������������������������������������������������������������������8 -

Rexroth Indramotion MLC/MLP Indralogic XLC 11VRS Field Busses

Electric Drives Linear Motion and and Controls Hydraulics Assembly Technologies Pneumatics Service Bosch Rexroth AG DOK-IM*ML*-FB******V11-AP01-EN-P Rexroth IndraMotion MLC/MLP IndraLogic XLC 11VRS Field Busses Title Rexroth IndraMotion MLC/MLP IndraLogic XLC 11VRS Field Busses Type of Documentation Application Manual Document Typecode DOK-IM*ML*-FB******V11-AP01-EN-P Internal File Reference RS-f7acbd514ebfbbb90a6846a0006e7c2d-1-en-US-5 Purpose of Documentation This documentation describes the field busses and their diagnostic function blocks for the IndraLogic XLC L25/ L45/ L65/ VEP systems and IndraMotion MLC/MLP L25/ L45/ L65/ VEP systems. It constitutes the basis for the online help. Record of Revision Edition Release Date Notes 120-3300-B317/EN -01 11.2010 First edition Copyright © Bosch Rexroth AG 2010 Copying this document, giving it to others and the use or communication of the contents thereof without express authority, are forbidden. Offenders are liable for the payment of damages. All rights are reserved in the event of the grant of a patent or the registration of a utility model or design (DIN 34-1). Validity The specified data is for product description purposes only and may not be deemed to be guaranteed unless expressly confirmed in the contract. All rights are reserved with respect to the content of this documentation and the availa‐ bility of the product. Published by Bosch Rexroth AG Bgm.-Dr.-Nebel-Str. 2 • 97816 Lohr a. Main, Germany Phone +49 (0)93 52/40-0 • Fax +49 (0)93 52/40-48 85 http://www.boschrexroth.com/ System IndraLogic & Basis Motion Logic GLo / HBu / vha / PiGe Note This document has been printed on chlorine-free bleached paper.