High-Level Synthesis Philippe Coussy • Adam Morawiec Editors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wowza Media Server® - Overview

Wowza Media Server® - Overview Wowza® Media Systems, LLC. June 2013, Wowza Media Server version 3.6 Copyright © 2006 – 2013 Wowza Media Systems, LLC. All rights reserved. Wowza Media Server version 3.6 Overview Copyright © 2006 - 2013 Wowza Media Systems, LLC. All rights reserved. This document is for informational purposes only and in no way shall be interpreted or construed to create any warranties of any kind, either express or implied, regarding the information contained herein. Third-Party Information This document contains links to third party websites that are not under the control of Wowza Media Systems, LLC ("Wowza") and Wowza is not responsible for the content on any linked site. If you access a third party website mentioned in this document, then you do so at your own risk. Wowza provides these links only as a convenience, and the inclusion of any link does not imply that Wowza endorses or accepts any responsibility for the content on third party sites. Trademarks Wowza, Wowza Media Systems, Wowza Media Server and related logos are either registered trademarks or trademarks of Wowza Media Systems, LLC in the United States and/or other countries. Adobe and Flash are either registered trademarks or trademarks of Adobe Systems Incorporated in the United States and/or other countries. Microsoft and Silverlight are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. QuickTime, iPhone, iPad and iPod touch are either registered trademarks or trademarks of Apple, Inc. in the United States and/or other countries. Other product names, logos, designs, titles, words or phrases mentioned may be third party registered trademarks or trademarks in the United States and/or other countries. -

Ellsworth American : August 17, 1876

Cbf £llsiP0rty Kates of Advertisi^f. Li ^nrriran lwk. Swltn. 3 mos. Omoi. I TV. 1 $160 00 $«00 $10 00 IB PCBLISBBD *T inch, $100 $4 3 inches. 3 CO 4 60 ON 15 00 25 0$ 0$ U T 4 column, 8 03 13 00 80 00 48 00 85 i: I.LSWO H, M E, 1 column. 14 0$ 22 00 50 00 86 0$ 100 00 BT TH* Special Notices. One square 3 weeks, $2.00 Each additional week, 50 cents iaacock County Publishing Co moan j Administrator’s and Kxeeutor’s Notices, 1 50 Citation from Probate Court, 8 uO Commissioner’s Notices, 2 8$ T«m« at Messenger’s and Assignee’s Notioti, t-00 SaburiylioB. Editorial Notices, per Tine, -1® Notices, *1® n« copy, n paid within three month*.•'^tK Obituary per line, No charge less than •*w i>»: within three month*,.. if st the end ©t the One inch space will constitute a square. paid year.2 j< Advertisements to be in advaoco. r*ill be discontinued nntil all Transient paid arrear No advertisements reconed less than a *re paid, except at the square. publisher** option— and Deaths inserted free. » person wishing his Marriages sad paper stopped, must to loti'-e thereof at the 1 early advertisers pay quarterly. ( expimtion of the tern • ictner previous notice has been given or not ME., THURSDAY, A.TTCHJST 17, 1870. ELLSWORTH, Tol. MlIdUM-No. 33. Imsiness It was not long after Hus I « (him; which Miss Moggaridge did with her •Aud when It Is all gone/ coutinued Miss expostulation through these Luke Moggaridge* that’1 her willing hands; by the calls of Master i|arbs. -

Website Specifications 20130106

Wowza Media Server® 3.6 Technical Specifications Wowza Media Server® software delivers market-leading functionality, reliability, and flexibility for streaming to any screen across a wide range of industries. Streaming Delivery Adobe Flash® RTMP Flash Player Multi-Protocol, Multi (RTMPE, RTMPT, RTMPTE, RTMPS) Adobe® AIR® Client Adobe Flash HTTP Dynamic Streaming (HDS) RTMP-compatible players HDS-compatible players Apple® HTTP Live Streaming (HLS) iPhone®, iPod®, iPad® (iOS 3.0 or later) QuickTime® Player (10.0 or later) Safari® (4.0 or later on Mac OS X version 10.6) Roku® streaming devices and other HLS-compatible players MPEG DASH DASH-264 Compatible Players Microsoft® Smooth Streaming Silverlight® 3 or later RTSP/RTP Quicktime Player VideoLAN VLC media player 3GPP-compatible mobile devices Other RTSP/RTP-compliant players MPEG2 Transport Protocol (MPEG-TS) IPTV set-top boxes Live Streaming RTMP Video: H.264, VP6, Sorenson Spark®, Screen Video v1 & v2 Compatible Encoding Audio: AAC, AAC-LC, HE-AAC, MP3, Speex, NellyMoser ASAO Inputs RTSP/RTP Video: H.264, H.263 Audio: AAC, AAC-LC, HE-AAC, MP3, Speex MPEG-TS Video: H.264 Audio: AAC, AAC-LC, HE-AAC, E-AC-3, AC-3, MP3 ICY (SHOUTcast/Icecast) Audio: AAC, AAC-LC, HE-AAC (aacPlus), v1 & v2, MP3 Support File Formats Video and Audio FLV (Flash Video - .flv) MP4 (QuickTime container - .mp4, .f4v, .mov, .m4v, .mp4a, .3gp, and .3g2) MP3 (.mp3) PIFF (.ism, .ismc, .ismv, .isma) Protocols and Payloads RTSP IETF RFC2326 RTP:H.264 IETF RFC3984, QuickTime Generic RTP Payload Format RTP:AAC IETF RFC3640, -

A Single-Chip MPEG-2 Codec Based on Customizable Media Embedded Processor

530 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, MARCH 2003 A Single-Chip MPEG-2 Codec Based on Customizable Media Embedded Processor Shunichi Ishiwata, Tomoo Yamakage, Yoshiro Tsuboi, Takayoshi Shimazawa, Tomoko Kitazawa, Shuji Michinaka, Kunihiko Yahagi, Hideki Takeda, Akihiro Oue, Tomoya Kodama, Nobu Matsumoto, Takayuki Kamei, Mitsuo Saito, Takashi Miyamori, Goichi Ootomo, and Masataka Matsui, Member, IEEE Abstract—A single-chip MPEG-2 MP@ML codec, integrating microprocessors, such as out-of-order speculative execution, P 3.8M gates on a 72-mm die, is described. The codec employs a branch prediction, and circuit technologies to achieve high heterogeneous multiprocessor architecture in which six micropro- clock frequency, are unsuitable for these application-specific cessors with the same instruction set but different customization execute specific tasks such as video and audio concurrently. processors. On the other hand, the addition of application-spe- The microprocessor, developed for digital media processing, cific instructions and/or hardware engines to accelerate heavy provides various extensions such as a very-long-instruction-word iteration of relatively simple tasks often results in a large gain coprocessor, digital signal processor instructions, and hardware in performance at little additional cost, especially in DSP ap- engines. Making full use of the extensions and optimizing the plications. A heterogeneous multiprocessor architecture using architecture of each microprocessor based upon the nature of specific tasks, the chip can execute not only MPEG-2 MP@ML simple and small microprocessors achieves a better cost–per- video/audio/system encoding and decoding concurrently, but also formance tradeoff than a single high-end general-purpose MPEG-2 MP@HL decoding in real time. -

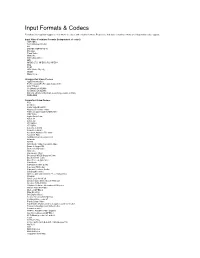

Input Formats & Codecs

Input Formats & Codecs Pivotshare offers upload support to over 99.9% of codecs and container formats. Please note that video container formats are independent codec support. Input Video Container Formats (Independent of codec) 3GP/3GP2 ASF (Windows Media) AVI DNxHD (SMPTE VC-3) DV video Flash Video Matroska MOV (Quicktime) MP4 MPEG-2 TS, MPEG-2 PS, MPEG-1 Ogg PCM VOB (Video Object) WebM Many more... Unsupported Video Codecs Apple Intermediate ProRes 4444 (ProRes 422 Supported) HDV 720p60 Go2Meeting3 (G2M3) Go2Meeting4 (G2M4) ER AAC LD (Error Resiliant, Low-Delay variant of AAC) REDCODE Supported Video Codecs 3ivx 4X Movie Alaris VideoGramPiX Alparysoft lossless codec American Laser Games MM Video AMV Video Apple QuickDraw ASUS V1 ASUS V2 ATI VCR-2 ATI VCR1 Auravision AURA Auravision Aura 2 Autodesk Animator Flic video Autodesk RLE Avid Meridien Uncompressed AVImszh AVIzlib AVS (Audio Video Standard) video Beam Software VB Bethesda VID video Bink video Blackmagic 10-bit Broadway MPEG Capture Codec Brooktree 411 codec Brute Force & Ignorance CamStudio Camtasia Screen Codec Canopus HQ Codec Canopus Lossless Codec CD Graphics video Chinese AVS video (AVS1-P2, JiZhun profile) Cinepak Cirrus Logic AccuPak Creative Labs Video Blaster Webcam Creative YUV (CYUV) Delphine Software International CIN video Deluxe Paint Animation DivX ;-) (MPEG-4) DNxHD (VC3) DV (Digital Video) Feeble Files/ScummVM DXA FFmpeg video codec #1 Flash Screen Video Flash Video (FLV) / Sorenson Spark / Sorenson H.263 Forward Uncompressed Video Codec fox motion video FRAPS: -

Wowza Media Server® 3

® Wowza Media Server 3 User’s Guide Copyright © 2006 - 2012 Wowza Media Systems, LLC All rights reserved. Wowza Media Server 3: User’s Guide Version: 3.1 Copyright 2006 – 2012 Wowza Media Systems, LLC http://www.wowza.com Copyright © 2006 - 2012 Wowza Media Systems, LLC All rights reserved. This document is for informational purposes only and in no way shall be interpreted or construed to create any warranties of any kind, either express or implied, regarding the information contained herein. Third Party Information This document contains links to third party websites that are not under the control of Wowza Media Systems, LLC (“Wowza”) and Wowza is not responsible for the content on any linked site. If you access a third party website mentioned in this document, then you do so at your own risk. Wowza provides these links only as a convenience, and the inclusion of any link does not imply that Wowza endorses or accepts any responsibility for the content on third party sites. This document refers to third party software that is not licensed, sold, distributed or otherwise endorsed by Wowza. Please ensure that any and all use of Wowza® software and third party software is properly licensed. Trademarks Wowza, Wowza Media Systems, Wowza Media Server and related logos are either registered trademarks or trademarks of Wowza Media System, LLC in the United States and/or other countries. Adobe and Flash are either registered trademarks or trademarks of Adobe Systems Incorporated in the United States and/or other countries. Microsoft and Silverlight are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. -

Scape D10.1 Keeps V1.0

Identification and selection of large‐scale migration tools and services Authors Rui Castro, Luís Faria (KEEP Solutions), Christoph Becker, Markus Hamm (Vienna University of Technology) June 2011 This work was partially supported by the SCAPE Project. The SCAPE project is co-funded by the European Union under FP7 ICT-2009.4.1 (Grant Agreement number 270137). This work is licensed under a CC-BY-SA International License Table of Contents 1 Introduction 1 1.1 Scope of this document 1 2 Related work 2 2.1 Preservation action tools 3 2.1.1 PLANETS 3 2.1.2 RODA 5 2.1.3 CRiB 6 2.2 Software quality models 6 2.2.1 ISO standard 25010 7 2.2.2 Decision criteria in digital preservation 7 3 Criteria for evaluating action tools 9 3.1 Functional suitability 10 3.2 Performance efficiency 11 3.3 Compatibility 11 3.4 Usability 11 3.5 Reliability 12 3.6 Security 12 3.7 Maintainability 13 3.8 Portability 13 4 Methodology 14 4.1 Analysis of requirements 14 4.2 Definition of the evaluation framework 14 4.3 Identification, evaluation and selection of action tools 14 5 Analysis of requirements 15 5.1 Requirements for the SCAPE platform 16 5.2 Requirements of the testbed scenarios 16 5.2.1 Scenario 1: Normalize document formats contained in the web archive 16 5.2.2 Scenario 2: Deep characterisation of huge media files 17 v 5.2.3 Scenario 3: Migrate digitised TIFFs to JPEG2000 17 5.2.4 Scenario 4: Migrate archive to new archiving system? 17 5.2.5 Scenario 5: RAW to NEXUS migration 18 6 Evaluation framework 18 6.1 Suitability for testbeds 19 6.2 Suitability for platform 19 6.3 Technical instalability 20 6.4 Legal constrains 20 6.5 Summary 20 7 Results 21 7.1 Identification of candidate tools 21 7.2 Evaluation and selection of tools 22 8 Conclusions 24 9 References 25 10 Appendix 28 10.1 List of identified action tools 28 vi 1 Introduction A preservation action is a concrete action, usually implemented by a software tool, that is performed on digital content in order to achieve some preservation goal. -

Supported Codecs and Formats Codecs

Supported Codecs and Formats Codecs: D..... = Decoding supported .E.... = Encoding supported ..V... = Video codec ..A... = Audio codec ..S... = Subtitle codec ...I.. = Intra frame-only codec ....L. = Lossy compression .....S = Lossless compression ------- D.VI.. 012v Uncompressed 4:2:2 10-bit D.V.L. 4xm 4X Movie D.VI.S 8bps QuickTime 8BPS video .EVIL. a64_multi Multicolor charset for Commodore 64 (encoders: a64multi ) .EVIL. a64_multi5 Multicolor charset for Commodore 64, extended with 5th color (colram) (encoders: a64multi5 ) D.V..S aasc Autodesk RLE D.VIL. aic Apple Intermediate Codec DEVIL. amv AMV Video D.V.L. anm Deluxe Paint Animation D.V.L. ansi ASCII/ANSI art DEVIL. asv1 ASUS V1 DEVIL. asv2 ASUS V2 D.VIL. aura Auravision AURA D.VIL. aura2 Auravision Aura 2 D.V... avrn Avid AVI Codec DEVI.. avrp Avid 1:1 10-bit RGB Packer D.V.L. avs AVS (Audio Video Standard) video DEVI.. avui Avid Meridien Uncompressed DEVI.. ayuv Uncompressed packed MS 4:4:4:4 D.V.L. bethsoftvid Bethesda VID video D.V.L. bfi Brute Force & Ignorance D.V.L. binkvideo Bink video D.VI.. bintext Binary text DEVI.S bmp BMP (Windows and OS/2 bitmap) D.V..S bmv_video Discworld II BMV video D.VI.S brender_pix BRender PIX image D.V.L. c93 Interplay C93 D.V.L. cavs Chinese AVS (Audio Video Standard) (AVS1-P2, JiZhun profile) D.V.L. cdgraphics CD Graphics video D.VIL. cdxl Commodore CDXL video D.V.L. cinepak Cinepak DEVIL. cljr Cirrus Logic AccuPak D.VI.S cllc Canopus Lossless Codec D.V.L. -

Infusion Therapy Standards of Practice 8Th Ed 2021.Pdf

Supplement to: January/February 2021 Volume 44 • Number 1S ISSN 1533-1458 www.journalofinfusionnursing.com Journal of Infusion Nursing The Official Publication of the Infusion Nurses Society Infusion Therapy Standards of Practice 8th Edition NANv44n1S-Cover.indd 1 12/30/20 12:57 AM Infusion Therapy Standards of Practice Lisa Gorski, MS, RN, HHCNS-BC, CRNI®, FAAN Lisa A. Gorski, MS, RN, HHCNS-BC, CRNI®, FAAN Lynn Hadaway Lynn Hadaway, MEd, RN, NPD-BC, CRNI® Mary E. Hagle, PhD, RN-BC, FAAN Mary E. Hagle, PhD, RN-BC, FAAN Daphne Broadhurst, MN, RN, CVAA(C) Daphne Broadhurst, MN, RN, CVAA(C) Simon Clare Simon Clare, MRes, BA, RGN Tricia Kleidon, MNSc (Nurs. Prac), BNSc, RN Tricia Kleidon, MNSc (Nurs. Prac), BNSc, RN Britt Meyer, PhD, RN, CRNI®, VA-BC, NE-BC Britt M. Meyer, PhD, RN, CRNI®, VA-BC, NE-BC Barbara Nickel Barb Nickel, APRN-CNS, CCRN, CRNI® Stephen Rowley, MSc, BSc (Hons), RGN, RSCN Stephen Rowley, MSc, BSc (Hons), RGN, RSCN Elizabeth Sharpe, DNP, APRN-CNP, NNP-BC, VA-BC, FNAP, FAANP Elizabeth Sharpe, DNP, APRN-CNP, NNP-BC, VA-BC, FNAP, FAANP, FAAN Mary Alexander, MA, RN, CRNI®, CAE, FAAN Mary Alexander, MA, RN, CRNI®, CAE, FAAN 8TH EDITION 8TH EDITION REVISED 2021 REVISED 2021 One Edgewater Drive, Norwood, MA 02062 One Edgewaterwww.ins1.org Drive, Norwood, MA 02062 www.ins1.org LEARN MORE AT WWW.INCC1.ORG The Art and Science of Infusion Nursing Journal of Infusion Nursing Editor INS Board of Directors Mary Alexander, MA, RN, CRNI®*, President Directors-at-Large ® ® ® ® CAE, FAAN Angie Sims, MSN, RN, CRNI , OCN Nancy Bowles, MHA, RN, OCN , CRNI , NEA-BE, CPC-A President Elect ® Associate Managing Editor Sue Weaver, PhD, RN, CRNI®, NEA-BC Angela Skelton, BSN, RN, CRNI Leslie Nikou Presidential Advisor Public Member Lynn Deutsch, MSN, RN, CRNI®, VA-BC John S. -

Wowza Media Server® 3

® Wowza Media Server 3 User's Guide Copyright © 2006 - 2013 Wowza Media Systems, LLC. All rights reserved. Wowza Media Server 3: User's Guide Version: 3.6.3 http://www.wowza.com Copyright © 2006 - 2013 Wowza Media Systems, LLC. All rights reserved. This document is for informational purposes only and in no way shall be interpreted or construed to create any warranties of any kind, either express or implied, regarding the information contained herein. Third Party Information This document contains links to third party websites that are not under the control of Wowza Media Systems, LLC ("Wowza") and Wowza is not responsible for the content on any linked site. If you access a third party website mentioned in this document, then you do so at your own risk. Wowza provides these links only as a convenience, and the inclusion of any link does not imply that Wowza endorses or accepts any responsibility for the content on third party sites. This document refers to third party software that is not licensed, sold, distributed or otherwise endorsed by Wowza. Please ensure that any and all use of Wowza® software and third party software is properly licensed. Trademarks Wowza, Wowza Media Systems, Wowza Media Server and related logos are either registered trademarks or trademarks of Wowza Media Systems, LLC in the United States and/or other countries. Adobe and Flash are either registered trademarks or trademarks of Adobe Systems Incorporated in the United States and/or other countries. Microsoft and Silverlight are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. -

1970 Evidence Convention – the Use of Video-Link

1970 Evidence Convention Guide to Good Practice The Use of Video-Link Hague Conference on Private International Law – Conférence de La Haye de droit international privé 1970 Evidence Convention Guide to Good Practice The Use of Video-Link Guide to Good Practice on the Use of Video-Link under the Evidence Convention Published by The Hague Conference on Private International Law – HCCH Permanent Bureau Churchillplein 6b 2517 JW The Hague Netherlands +31 70 363 3303 +31 70 360 4867 [email protected] www.hcch.net © Hague Conference on Private International Law 2020 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, including photocopying or recording, without the written permission of the Permanent Bureau of the Hague Conference. ISBN 978-94-90265-99-1 Published in The Hague, the Netherlands FOREWORD On behalf of the Permanent Bureau of the HCCH, I am delighted to present this Guide to Good Practice on the Use of Video-Link under the Convention of 18 March 1970 on the Taking of Evidence Abroad in Civil or Commercial Matters (Evidence Convention). The drafters of the Convention had the foresight to adopt an approach that is completely technology neutral – an approach which, as this Guide demonstrates, has stood the test of time. The use of technology to facilitate the operation of the Convention has ensured that it can keep pace with the realities of our rapidly changing world. Now, as the Evidence Convention nears its fiftieth anniversary, it continues to attract new Contracting Parties from across the globe. -

XP Machine Will Now Use Directx Mode by Default, Like in Previous Versions

Changes between 2.0.1 and 2.0.2: -------------------------------- Video Output: * XP machine will now use DirectX mode by default, like in previous versions. There were too many errors with broken drivers. * More accurate colourspaces conversions for YUV>RGB in OpenGL * Add menu support for libvlc / VLCKit applications on Mac OS X * Various fixes on Mac OS X, notably for crop, zoom, osd and menu support * Misc fixes in OpenGL module, on all platforms * Fix video output on PowerPCbased Macs equipped with an ATI Radeon 7500, an ATI Radeon 9200 or a NVIDIA GeForceFX 5200 Ultra. * Fix video output of 10bit encoded contents on Intelbased Macs equipped with an Intel GMA 950 chipset running OS X 10.6 or later. * Add support for the HiDPI mode used on recent Apple products with socalled Retina Displays. Access: * Rework Digital TV module for Windows. DVBT and DVBC should work again * Fixes for RAR compressed files * Fix DirectShow crashes on exit * Improve PulseAudio input latency * Fixes for HTTP access through a proxy * v4l2 webcam outputting H264 can now be used directly (use v4l2chroma=h264) * Fix subtitles autodetection in subfolders and detection behaviour * IE http proxy is not used anymore by VLC on Win32 * Accept more extensions for DVD images * Fix crash in VC1 packetizer * Improvements in BluRay playback * Improvements and fixes in HLS support Codec: * Fix crashes in AAC decoder on channels changes, notably in ISDB streams * Fix compilation with multiple FFmpeg and libav versions * Fix G726 support * Fix MP3 free format support Demuxers: