A Review of the 1.4 Μm Pixel Generation Ray Fontaine Technology Analysis Group Chipworks Inc

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nokia Lumia 521 User Manual

www.nokia.com Product and safety information Copyright © 2013 Nokia. All rights reserved. Nokia and Nokia Connecting People are trademarks or registered trademarks of Nokia Corporation. Other product and company names mentioned herein may be trademarks or trade names of their respective owners. The phone supplied in the sales package may differ from that shown. Specifications subject to change without notice. Printed in China. 9260765 Ver. 1.0 03/13 Quick Guide Psst... Nokia Lumia 521 This guide isn't all there is... For the online user guide, even more info, user Contents guides in another language, and Safety 3 troubleshooting help, go to www.nokia.com/ support. Keys and parts 4 Check out the videos at www.youtube.com/ Get started 5 NokiaSupportVideos. Get the basics 9 For info on Nokia Service terms and Privacy policy, go to www.nokia.com/privacy. Try out the touch screen 10 First start-up Take your friends with you 15 Your new phone comes with great features that will be installed when you start your phone Messages 17 for the first time. Allow some minutes for your Mail 21 phone to be ready. Take photos and share 25 HERE Maps 27 Browse the web 29 Feature-specific instructions 36 Product and safety information 38 2 Stop using the device until the glass is replaced by Safety qualified service personnel. Read these simple guidelines. Not following them may be dangerous or illegal. For further info, read the PROTECT YOUR HEARING complete user guide. To prevent possible hearing damage, do not listen at high volume levels for long periods. -

RADA Sense Mobile Application End-User Licence Agreement

RADA Sense Mobile Application End-User Licence Agreement PLEASE READ THESE LICENCE TERMS CAREFULLY BY CONTINUING TO USE THIS APP YOU AGREE TO THESE TERMS WHICH WILL BIND YOU. IF YOU DO NOT AGREE TO THESE TERMS, PLEASE IMMEDIATELY DISCONTINUE USING THIS APP. WHO WE ARE AND WHAT THIS AGREEMENT DOES We Kohler Mira Limited of Cromwell Road, Cheltenham, GL52 5EP license you to use: • Rada Sense mobile application software, the data supplied with the software, (App) and any updates or supplements to it. • The service you connect to via the App and the content we provide to you through it (Service). as permitted in these terms. YOUR PRIVACY Under data protection legislation, we are required to provide you with certain information about who we are, how we process your personal data and for what purposes and your rights in relation to your personal data and how to exercise them. This information is provided in https://www.radacontrols.com/en/privacy/ and it is important that you read that information. Please be aware that internet transmissions are never completely private or secure and that any message or information you send using the App or any Service may be read or intercepted by others, even if there is a special notice that a particular transmission is encrypted. APPLE APP STORE’S TERMS ALSO APPLY The ways in which you can use the App and Documentation may also be controlled by the Apple App Store’s rules and policies https://www.apple.com/uk/legal/internet-services/itunes/uk/terms.html and Apple App Store’s rules and policies will apply instead of these terms where there are differences between the two. -

Step 1(To Be Performed on Your Google Pixel 2 XL)

For a connection between your mobile phone and your Mercedes-Benz hands-free system to be successful, Bluetooth® must be turned on in your mobile phone. Please make sure to also read the operating and pairing instructions of the mobile phone. Please follow the steps below to connect your mobile phone Google Pixel 2 XL with the mobile phone application of your Mercedes-Benz hands-free system using Bluetooth®. Step 1(to be performed on your Google Pixel 2 XL) Step 2 To get to the telephone screen of your Mercedes-Benz hands-free system press the Phone icon on the homescreen. Step 3 Select the Phone icon in the lower right corner. Step 4 Select the “Connect a New Device” application. Page 1 of 3 Step 5 Select the “Start Search Function” Step 6 The system will now search for any Bluetooth compatible phones. This may take some time depending on how many devices are found by the system. Step 7 Once the system completes searching select your mobile phone (example "My phone") from the list. Step 8 The pairing process will generate a 6-digit passcode and display it on the screen. Verify that the same 6 digits are shown on the display of your phone. Step 9 (to be performed on your Google Pixel 2 XL) There will be a pop-up "Bluetooth Request: 'MB Bluetooth' would like to pair with your phone. Confirm that the code '### ###' is shown on 'MB Bluetooth'. " Select "Pair" on your phone if the codes match. Page 2 of 3 Step 10 After the passcode is verified on both the mobile and the COMAND, the phone will begin to be authorized. -

Comparison: Android Vs IOS for Mediography

Comparison: Android vs IOS for mediography 2016.12 Pure Android Google phone iPhone 6s and later (Nexus 5x, Nexus 6, (iPhone 6s, iPhone 6s Plus, Nexus 6p, Pixel, Pixel XL) iPhone 7, iPhone 7 Plus) Works with Project Fi? 100%, Officially, no... (see my related article) including seamless switching Unofficially yes... between WiFi, US Cellular, but only as well as an iPhone Sprint and T-Mobile, can work solely with T-Mobile, including WiFi and including WiFi and T-Mobile’s coveted T-Mobile’s coveted 700 MHz band 700 MHz band. (It can’t use the US Cellular and Sprint networks —until if and when— Apple and Google make it official.) Over 130 countries Yes! Yes! with data roaming at no With Project Fi With Project Fi extra cost or T-Mobile (Simple Choice) or T-Mobile (Simple Choice) as your primary carrier. as your primary carrier. Allows 5GHz personal Yes! No! hotspot? (See this article) What’s up with that Apple? It has been four generations since you added 5 GHz to the original iPhone 5. It’s about time you make it available for the personal hotspot. Allows WiFi Analyzer Yes! No! or equivalent (See this article) Still photos Tie Tie Video with FiLMiC Pro, Tie Tie including 4K UHD at 100 megabits per second Mono direct native Recording quality is a tie. Recording quality is a tie. 48 kHz audio recording from a single digital Regarding Regarding microphone, using my confidence monitoring: confidence monitoring: recommended apps Unless the digital mic has its Latency for live audio monitoring own latency-free monitoring from latest iPhone models is feature (i.e. -

Nokia 7.2 Is Designed to Offer Fans Advanced Tools to Express Their Creativity with a Powerful 48MP Triple Camera Featuring ZEISS Optics

Key features Key specifications1 Nokia 7.2 is designed to offer fans advanced tools to express their creativity with a powerful 48MP triple camera featuring ZEISS Optics. The ITEM SPECIFICATION smartphone combines stunning PureDisplay screen technology with SKU 1 ROW: GSM: 850, 900, 1800, 1900; WCDMA: 1, 5, 8; LTE: 1, 3, 5, 7, 8, Nokia 7.2 20, 28, 38, 40, 41 (120MHz) timeless Nordic design, in a class-defining package. NETWORK SKU 2 LATAM+US: GSM: 850, 900, 1800, 1900; WCDMA: 1, 2, 4, 5, 8; LTE: 1, BANDS 2, 3, 4, 5, 7, 8, 12/17, 13, 28, 66 Get creative with ZEISS Optics and powerful AI SKU 3 INDIA: GSM 900, 1800; WCDMA: 1, 5, 8; LTE: 1, 3, 5, 8, 40, 41 48MP triple camera with ZEISS Create shareworthy memories with intricate detail in both well lit and dim (120MHz) NETWORK Optics combined with state-of-the- conditions with Nokia 7.2’s triple camera featuring a highly sensitive 48MP SKU 1 & 2 LTE CAT6, SKU 3 LTE CAT 4 art PureDisplay sensor with Quad Pixel technology and ZEISS Optics and powerful AI. SPEED OS Android 9 Pie Portrait mode with unique ZEISS bokeh styles - ZEISS Modern, ZEISS Swirl CPU Qualcomm SDM660 and ZEISS Smooth - that recreate the way legendary ZEISS lenses produce RAM 4/6GB LPPDDR4x high visual impact and signature blur. STORAGE ROM: 64/128GB2 e-MMC 5.1, uSD supports to 512GB. Google Drive SIM Dual SIM + SD card slots (3 in 3) AI powered Night mode with image fusion and exposure stacking can 6.3" FHD+ Waterdrop, PureDisplay, Brightness (typ.) 500nits, contrast ratio sense whether hand held or on a tripod, adjusting the number of DISPLAY 1:1500, NTSC ratio 96%, SDR to HDR, HDR10 support for Amazon, Corning® exposures accordingly. -

These Phones Will Still Work on Our Network After We Phase out 3G in February 2022

Devices in this list are tested and approved for the AT&T network Use the exact models in this list to see if your device is supported See next page to determine how to find your device’s model number There are many versions of the same phone, and each version has its own model number even when the marketing name is the same. ➢EXAMPLE: ▪ Galaxy S20 models G981U and G981U1 will work on the AT&T network HOW TO ▪ Galaxy S20 models G981F, G981N and G981O will NOT work USE THIS LIST Software Update: If you have one of the devices needing a software upgrade (noted by a * and listed on the final page) check to make sure you have the latest device software. Update your phone or device software eSupport Article Last updated: Sept 3, 2021 How to determine your phone’s model Some manufacturers make it simple by putting the phone model on the outside of your phone, typically on the back. If your phone is not labeled, you can follow these instructions. For iPhones® For Androids® Other phones 1. Go to Settings. 1. Go to Settings. You may have to go into the System 1. Go to Settings. 2. Tap General. menu next. 2. Tap About Phone to view 3. Tap About to view the model name and number. 2. Tap About Phone or About Device to view the model the model name and name and number. number. OR 1. Remove the back cover. 2. Remove the battery. 3. Look for the model number on the inside of the phone, usually on a white label. -

Device Compatibility

Device compatibility Check if your smartphone is compatible with your Rexton devices Direct streaming to hearing aids via Bluetooth Apple devices: Rexton Mfi (made for iPhone, iPad or iPod touch) hearing aids connect directly to your iPhone, iPad or iPod so you can stream your phone calls and music directly into your hearing aids. Android devices: With Rexton BiCore devices, you can now also stream directly to Android devices via the ASHA (Audio Streaming for Hearing Aids) standard. ASHA-supported devices: • Samsung Galaxy S21 • Samsung Galaxy S21 5G (SM-G991U)(US) • Samsung Galaxy S21 (US) • Samsung Galaxy S21+ 5G (SM-G996U)(US) • Samsung Galaxy S21 Ultra 5G (SM-G998U)(US) • Samsung Galaxy S21 5G (SM-G991B) • Samsung Galaxy S21+ 5G (SM-G996B) • Samsung Galaxy S21 Ultra 5G (SM-G998B) • Samsung Galaxy Note 20 Ultra (SM-G) • Samsung Galaxy Note 20 Ultra (SM-G)(US) • Samsung Galaxy S20+ (SM-G) • Samsung Galaxy S20+ (SM-G) (US) • Samsung Galaxy S20 5G (SM-G981B) • Samsung Galaxy S20 5G (SM-G981U1) (US) • Samsung Galaxy S20 Ultra 5G (SM-G988B) • Samsung Galaxy S20 Ultra 5G (SM-G988U)(US) • Samsung Galaxy S20 (SM-G980F) • Samsung Galaxy S20 (SM-G) (US) • Samsung Galaxy Note20 5G (SM-N981U1) (US) • Samsung Galaxy Note 10+ (SM-N975F) • Samsung Galaxy Note 10+ (SM-N975U1)(US) • Samsung Galaxy Note 10 (SM-N970F) • Samsung Galaxy Note 10 (SM-N970U)(US) • Samsung Galaxy Note 10 Lite (SM-N770F/DS) • Samsung Galaxy S10 Lite (SM-G770F/DS) • Samsung Galaxy S10 (SM-G973F) • Samsung Galaxy S10 (SM-G973U1) (US) • Samsung Galaxy S10+ (SM-G975F) • Samsung -

Sprint Complete Equipment Replacement Insurance Program (ERP) Equipment Service and Repair Service Contract Program (ESRP)

Sprint Complete Equipment Replacement Insurance Program (ERP) Equipment Service and Repair Service Contract Program (ESRP) This device schedule is updated regularly to include new models. Check this document any time your equipment changes and before visiting an authorized repair center for service. If you are not certain of the model of your phone, refer to your original receipt or it may be printed on the white label located under the battery of your device. Repair eligibility is subject to change. Models Eligible for $29 Cracked Screen Repair Apple Samsung HTC LG • iPhone 5 • iPhone SE • Grand Prime • GS9 • One M8 • G Flex • G3 Vigor • iPhone 5C • iPhone 7 • GS4 • GS9 Plus • One E8 • G Flex II • G4 • iPhone 5S • iPhone 7 Plus • GS5 • Note 3 • One M9 • G Stylo • G5 • iPhone 6 • iPhone 8 • GS6 • Note 4 • One M10 • Stylo 2 • G6 • iPhone 6 Plus • iPhone 8 Plus • GS6 Edge • Note 5 • Bolt • Stylo 3 • V20 • iPhone 6S • iPhone X • GS6 Edge+ • Note 8 • HTC U11 • G7 ThinQ • X power • iPhone 6S Plus • iPhone XS • GS7 • Note 9 • G8 ThinQ • V40 ThinQ • iPhone XS Max • GS7 Edge • GS10 • iPhone XR • GS8 • GS10e • GS8 Plus • GS10+ Deductible/Service Fee and Repair Schedule Monthly Charge Tier 1 Tier 2 Tier 3 Tier 4 Tier 5 Sprint Complete $9 $9 - - - - Sprint Complete (Includes AppleCare® Services for eligible devices) - $15 $15 $15 $19 Equipment Service and Repair Program (ESRP) $8.25 $8.25 $8.25 $8.25 $11 Phone: Insurance Deductibles (ERP) and Service Contract ADH Service Fees during Asurion Administration (ESRP) ADH Cracked Screen Repair (ESRP) $25 $29 $29 $29 $29 ESRP standalone coverage does not include $29 cracked screens. -

Surflink Mini Mobile Compatibility Chart Download

Which cell phones have been tested with SurfLink Mini Mobile? These cell phones/tablets have passed interoperability testing or satisfied extensive field testing with SurfLink® Mini Mobile. Additional testing will be done as new phones/tablets get released or their firmware gets updated. Other cell phones/tablets may be compatible with SurfLink Mini Mobile. The list below only represents models that have been formally tested. Cell Phone / Tablet Apple iPhone 3G Apple iPhone SE LG Nexus 5 Samsung Galaxy Note 8 Apple iPhone 3GS Apple iPod Touch (5th Gen) Motorola Droid Turbo Samsung Galaxy S5 Apple iPhone 4 Asus ZenFone 2 Laser Motorola Moto E4 Plus Samsung Galaxy S7 Edge Apple iPhone 4S Asus ZenFone V Motorola Moto Z2 Play Samsung Galaxy S8 Apple iPhone 6 Google Pixel XL Motorola Moto Z2 Force Samsung Galaxy S8+ Apple iPhone 6S HTC One M7 OnePlus One Apple iPhone 6S+ LG G Flex Samsung Galaxy Avant Apple iPhone 7 LG G2 Samsung Galaxy J7 V Apple iPhone 7+ LG G6 Samsung Galaxy Note 4 Disclaimer: All cell phones and tablets in this list have been tested comprehensively by Starkey®, and have been found to fulfill the minimum requirements for SurfLink Mini Mobile compatibility at the time of testing. However, Starkey takes no responsibility for such compatibility in general. Specifically, Starkey shall not be responsible for incompatibility resulting from future updates of the cell phones or tablets, nor from events of incompatibility not covered by and/or found in these tests. Starkey takes no financial responsibility in terms of reimbursements of cell phones/tablets, which do not work as expected. -

COMPATIBLE DEVICES Which Phones Are Compatible with Kinsa

COMPATIBLE DEVICES Which phones are compatible with Kinsa thermometers? The Kinsa QuickCare, Smart Ear, and Smart Stick thermometers are compatible with numerous smartphones, and the details are listed below. If your phone doesn't meet the minimum requirements, it is not officially compatible and cannot be guaranteed to work with Kinsa thermometers. Find your thermometer in the table below and click iPhone or Android to view the compatible smartphones. Phone Compatibility iPhone Android QuickCare iPhone Android Smart Ear iPhone Android Smart Stick Minimum Requirements To enable smart features, all Kinsa thermometers must be connected to the Kinsa app, available for iPhone and Android. The Kinsa app requires iOS 10 or later on iPhones, and Android 5.0 (Lollipop) or later on Android phones. The Kinsa Smart Ear requires a Bluetooth LE connection and is therefore only compatible with smartphones which have Bluetooth 4.0. QuickCare and iPhone iPhone Status iPhone X ✅ iPhone 8 ✅ iPhone 8 Plus ✅ iPhone 7 ✅ iPhone 7 Plus ✅ iPhone 6S ✅ iPhone 6S Plus ✅ iPhone 6 ✅ iPhone 6 Plus ✅ iPhone SE ✅ iPhone 5s ✅ iPhone 5c ✅ iPhone 5 ✅ iPhone 4s ❌ iPhone 4 ❌ QuickCare and Android Compatible with any Android phone running Android 5.0 or above. Leading android phones listed below: Android Phone Status Samsung Note 8 ✅ Samsung Note 5 ✅ Samsung Note 4 ✅ Samsung Note 3 ✅ Samsung Note 2 ✅ Samsung Galaxy S8 ✅ Samsung Galaxy S7 ✅ Samsung Galaxy S7 Active ✅ Samsung Galaxy S7 Edge ✅ Samsung Galaxy S6 ✅ Samsung Galaxy S6 Active ✅ Samsung Galaxy S6 Edge ✅ Samsung Galaxy -

List of Supported Devices

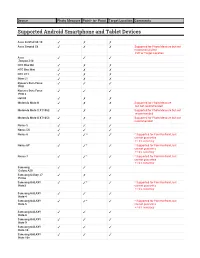

Device Photo Measure Point- to- Point Target Location Comments Supported Android Smartphone and Tablet Devices Asus ZenPad 3S 10 ✓ ✗ ✗ Asus Zenpad Z8 ✓ ✗ ✗ Supported for Photo Measure but not recommended for P2P or Target Location Asus ✓ ✓ ✓ Zenpad Z10 HTC One M8 ✓ ✗ ✗ HTC One Mini ✓ ✗ ✗ HTC U11 ✓ ✗ ✗ iNew L1 ✓ ✗ ✗ Kyocera Dura Force ✓ ✓ ✓ PRO Kyocera Dura Force ✓ ✓ ✓ PRO 2 LGV20 ✓ ✗ ✗ Motorola Moto G ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1052 ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1053 ✓ ✗ ✗ Supported for Photo Measure but not recommended Nexus 5 ✓ ✓ ✓ Nexus 5X ✓ ✓ ✓ Nexus 6 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 6P ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 7 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Samsung ✓ ✓ ✓ Galaxy A20 Samsung Galaxy J7 ✓ ✗ ✓ Prime Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note3 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 4 Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note 5 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 8 Samsung GALAXY ✓ ✓ ✓ Note 9 Samsung GALAXY ✓ ✓ ✓ Note 10 Samsung GALAXY ✓ ✓ ✓ Note 10+ Device Photo Measure Point- to- Point Target Location Comments Samsung GALAXY ✓ ✓ ✓ Note 10+ 5G Samsung GALAXY ✓ ✓ ✓ Note 20 Samsung GALAXY ✓ ✓ ✓ Note 20 5G Samsung GALAXY ✓ ✗ ✗ Supported for Photo Measure but not Tab 4 (old) recommended Samsung GALAXY ✓ ✗ ✓ Supported for Photo -

Mobile Device & OS Compatibility

Mobile Device & OS Compatibility Click here for English Cliquez ici pour Français Haga clic aquí para seleccionar Español Klicka här för Svenska Klicken Sie hier für Deutsch Fare clic qui per Italiano Hier klikken voor Nederlands Valitse tästä kieleksi suomi Κάντε κλικ εδώ για Ελληνικά Kliknij tutaj, aby włączyć język polski Haga clic aquí para la versión en español Cliquez ici pour le français Clique aqui para Português Klik her for dansk Klikk her for norsk اﻧﻘﺮ ھﻨﺎ ﻟﻠﻐﺔ اﻟﻌﺮﺑﯿﺔ Clique aqui para Português 點選此處瀏覽中文版 לחץ כאן עבור עברית 한국어를 선택하려면 여기를 클릭하십시오 Нажмите здесь, чтобы перейти на русский Türkçe için buraya tıklayın 中 文( 简 体 )请 点 击 这 里 FreeStyle, Libre, and related brand marks are trademarks of Abbott Diabetes Care Inc. in various jurisdictions. Other trademarks are the property of their respective owners. ©2019 Abbott ART39109-001 Rev. H 02/20 MOBILE DEVICE & OS COMPATIBILITY Popular mobile devices and operating systems (OS) are regularly tested to evaluate NFC scan performance, Bluetooth connectivity, and app compatibility with Sensors. We recommend checking this guide before installing a new OS version on your phone or before using the app with a new phone. Recommended app, device, and operating systems APP / VERSION DEVICE OS iPhone 7, 7 Plus, 8, 8 Plus, X, XS, XS Max, XR FreeStyle LibreLink Samsung Galaxy S6, Galaxy S7 Edge, Galaxy S8, Galaxy S8+, Galaxy S9 iOS: 12, 13 (version 2.4) Google Pixel, Pixel 2, Pixel 2 XL Android: 8, 9, 10 LG Nexus 5X iPhone 7, 7 Plus, 8, 8 Plus, X, XS, XS Max, XR Samsung Galaxy S5, Galaxy S6, Galaxy S7, Galaxy S7 Edge, Galaxy S8, FreeStyle LibreLink Galaxy S8+, Galaxy S9 iOS: 11, 12, 13 Android: 5, 6, 7, 8, 9, 10 (version 2.3) Google Pixel, Pixel 2, Pixel 2 XL LG Nexus 5X iPhone 7, 7 Plus, 8, 8 Plus, X Samsung Galaxy S5, Galaxy S6, Galaxy S7, Galaxy S7 Edge, Galaxy S8, Galaxy S8+, Galaxy S9 FreeStyle LibreLink iOS: 11, 12, 13 (version 2.2) Google Pixel, Pixel 2, Pixel 2 XL Android: 5, 6, 7, 8, 9, 10 Nexus 5X, 6P OnePlus 5T This table will be updated as other devices and operating systems are evaluated.