Low-Noise Local Oscillator Design Techniques Using a DLL-Based Frequency Multiplier for Wireless Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Toward a Large Bandwidth Photonic Correlator for Infrared Heterodyne Interferometry a first Laboratory Proof of Concept

A&A 639, A53 (2020) Astronomy https://doi.org/10.1051/0004-6361/201937368 & c G. Bourdarot et al. 2020 Astrophysics Toward a large bandwidth photonic correlator for infrared heterodyne interferometry A first laboratory proof of concept G. Bourdarot1,2, H. Guillet de Chatellus2, and J-P. Berger1 1 Univ. Grenoble Alpes, CNRS, IPAG, 38000 Grenoble, France e-mail: [email protected] 2 Univ. Grenoble Alpes, CNRS, LIPHY, 38000 Grenoble, France Received 19 December 2019 / Accepted 17 May 2020 ABSTRACT Context. Infrared heterodyne interferometry has been proposed as a practical alternative for recombining a large number of telescopes over kilometric baselines in the mid-infrared. However, the current limited correlation capacities impose strong restrictions on the sen- sitivity of this appealing technique. Aims. In this paper, we propose to address the problem of transport and correlation of wide-bandwidth signals over kilometric dis- tances by introducing photonic processing in infrared heterodyne interferometry. Methods. We describe the architecture of a photonic double-sideband correlator for two telescopes, along with the experimental demonstration of this concept on a proof-of-principle test bed. Results. We demonstrate the a posteriori correlation of two infrared signals previously generated on a two-telescope simulator in a double-sideband photonic correlator. A degradation of the signal-to-noise ratio of 13%, equivalent to a noise factor NF = 1:15, is obtained through the correlator, and the temporal coherence properties of our input signals are retrieved from these measurements. Conclusions. Our results demonstrate that photonic processing can be used to correlate heterodyne signals with a potentially large increase of detection bandwidth. -

Electronic Warfare Fundamentals

ELECTRONIC WARFARE FUNDAMENTALS NOVEMBER 2000 PREFACE Electronic Warfare Fundamentals is a student supplementary text and reference book that provides the foundation for understanding the basic concepts underlying electronic warfare (EW). This text uses a practical building-block approach to facilitate student comprehension of the essential subject matter associated with the combat applications of EW. Since radar and infrared (IR) weapons systems present the greatest threat to air operations on today's battlefield, this text emphasizes radar and IR theory and countermeasures. Although command and control (C2) systems play a vital role in modern warfare, these systems are not a direct threat to the aircrew and hence are not discussed in this book. This text does address the specific types of radar systems most likely to be associated with a modern integrated air defense system (lADS). To introduce the reader to EW, Electronic Warfare Fundamentals begins with a brief history of radar, an overview of radar capabilities, and a brief introduction to the threat systems associated with a typical lADS. The two subsequent chapters introduce the theory and characteristics of radio frequency (RF) energy as it relates to radar operations. These are followed by radar signal characteristics, radar system components, and radar target discrimination capabilities. The book continues with a discussion of antenna types and scans, target tracking, and missile guidance techniques. The next step in the building-block approach is a detailed description of countermeasures designed to defeat radar systems. The text presents the theory and employment considerations for both noise and deception jamming techniques and their impact on radar systems. -

Detecting and Locating Electronic Devices Using Their Unintended Electromagnetic Emissions

Scholars' Mine Doctoral Dissertations Student Theses and Dissertations Summer 2013 Detecting and locating electronic devices using their unintended electromagnetic emissions Colin Stagner Follow this and additional works at: https://scholarsmine.mst.edu/doctoral_dissertations Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering Recommended Citation Stagner, Colin, "Detecting and locating electronic devices using their unintended electromagnetic emissions" (2013). Doctoral Dissertations. 2152. https://scholarsmine.mst.edu/doctoral_dissertations/2152 This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact [email protected]. DETECTING AND LOCATING ELECTRONIC DEVICES USING THEIR UNINTENDED ELECTROMAGNETIC EMISSIONS by COLIN BLAKE STAGNER A DISSERTATION Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY in ELECTRICAL & COMPUTER ENGINEERING 2013 Approved by Dr. Steve Grant, Advisor Dr. Daryl Beetner Dr. Kurt Kosbar Dr. Reza Zoughi Dr. Bruce McMillin Copyright 2013 Colin Blake Stagner All Rights Reserved iii ABSTRACT Electronically-initiated explosives can have unintended electromagnetic emis- sions which propagate through walls and sealed containers. These emissions, if prop- erly characterized, enable the prompt and accurate detection of explosive threats. The following dissertation develops and evaluates techniques for detecting and locat- ing common electronic initiators. The unintended emissions of radio receivers and microcontrollers are analyzed. These emissions are low-power radio signals that result from the device's normal operation. -

Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique

University of Central Florida STARS Retrospective Theses and Dissertations 1986 Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique Luis M. Jimenez University of Central Florida Part of the Engineering Commons Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact [email protected]. STARS Citation Jimenez, Luis M., "Phase-Locked Loop Based Oscillator Phase Noise Measurement Technique" (1986). Retrospective Theses and Dissertations. 4980. https://stars.library.ucf.edu/rtd/4980 PHASE-LOCKED LOOP BASED OSCILLATOR PHASE NOISE MEASUREMENT TECHNIQUE BY LUIS MIGUEL JIMENEZ B.S.E., University of Central Florida, 1984 THESIS Submitted in partial fulfillment of the requirements for the degree of Master of Science in the Graduate Studies Program of the College of Engineering University of Central Florida Orlando, Florida Summer Term 1986 ABSTRACT Oscillators play an important role in the performance of various radio frequency (RF) systems. The generation of stable carrier and clock frequencies is necessary at both the transmitter and receiver ends of a communication system. Phase noise is the parameter used to characterize an oscillator frequency stability. This thesis introduces a phase noise measurement technique using a phase-locked loop. A 100 MHz Colpitt's oscillator, for the phase noise source, was designed and built. The output of the oscillator was mixed down to 10 MHz, before a phase-locked loop extracted the phase noise information. -

Principles of Interferometry

Principles of Interferometry Hans-Rainer Klöckner IMPRS Black Board Lectures 2014 acknowledgement § Mike Garrett lectures § Uli Klein lectures § Adam Deller NRAO Summer School lectures § WIKI – for technical stuff Lecture 3 § radio astronomical system § heterodyne receivers § low-noise amplifiers § system noise performance § data sampling/representation § Fourier transformation a basic system relate the voltages measured at the 2k receiver system to the antenna temperature Sν = TA Aeff alternating current (AC) detector input power ~ 10-5 W Tsys = 20 K, Δν 50 MHz P = 1.4 10-14 W direct current (DC) ~108 amplification / gain heterodyne receiver after all its just listening to radio the most used setup T1 needs cooling low noise amplifier High Electron Mobility Transistor need to stay in the linear regime mixer – frequencyFrequency (down) conversiondown conversion vRF vIF A typical receiver tries to down-convert the “sky signal” or “Radio vLO Frequency” (or RF) to a lower, “Intermediate Frequency” (or IF) signal. The reasons for doing this include: (i) signal losses (e.g. in cables) typically go as frequency2; (ii) it is much easier to mainpulate the signal (e.g. amplify, filter, delay, sample/process/digitise it) at lower frequencies. We use so-called “heterodyne” systems to mix the RF signal with a pure, monochromatic frequency tone, known as a Local Oscillator (or LO). Consider an RF signal in a band centred on frequency vRF, and an LO with frequency vLO, these can be represented as two sine waves with angular frequencies w and wo: -- Difference frequency -- -- Sum frequency -- vRF-vLO vRF+vLO Output freq Inputs vLO vRF LSB - regime USB - regime mixer – frequency down conversion The higher frequency component (“sum frequency” vRF+vLO) is usually removed by a The higher frequency component (“sum The higher frequency component (“sum filter that is included in the LO electronics. -

SUPERHETERODYNE CONVERTORS and 1-F AMPLIFIERS

ELECTRONIC TECHNOLOGY SERIES SUPERHETERODYNE CONVERTORS and 1-F AMPLIFIERS ,#.,_. •~· .• :· :-,:·,' . ...~ ' ' ' . ' ,\,.. • · ,, . ,·;, . :; ~: ~, :· ,. ~: '.·· .. '. •'.~ ;·. '~ . ' . ., . :• a publication SUPERHETERODYNE CONVERTERS AND 1-F AMPLIFIERS Edited by Alexander Schure, Ph. D., Ed. D. JOHN F. RIDER PUBLISHER, INC., NEW YORK a division of HAYDEN PUBLISHING COMPANY, INC. Copyright IC 1963 JOHN F. RIDER PUBLISHER, INC. All rights reserved. This book or any parts there may not be reproduced in any form or in any language without permission. SECOND EDITION Library of Congress Catalog Number 6J-20JJ6 Printed in the United States of America PREFACE The utilization of heterodyning action in receiver design via local oscillator, mixer, or converter action marks one of the major steps in the advance of communications. Application of the basic prin ciples of superheterodyne operation solved many of the problems inherent in the earlier tuned radio frequency receivers. Such factors as receiver stability, gain, selectivity, and uniform bandpass over an entire band could be improved by using the superheterodyne receiver. The reasons for the enormous popularity of this design are apparent, as is the need for the technician to understand the theory and operation of superheterodyne converters and i-f ampli fiers. This book is organized to provide the student with an under standing of these fundamental principles, with emphasis on the descriptive treatment and analyses. Mathematical formulas or numerical examples are presented where pertinent and necessary to illustrate the discussion more fully. Specific attention has been given to the essential theory of mixers and converters; basic superheterodyne operation; arithmetic selec tivity; image frequency considerations; double conversion; conver sion efficiency; oscillator tracking; pulling and squegging; types of converters (both early and modern) ; functions and design factors of i-f amplifiers; choices of i-f frequencies; ave and davc; the Miller effect; and the consideration of alignment procedures. -

Vii Iiiilii J F

Vii iiiilii J F II?iidIiit by PETER LANKSHEAR Converters, first detectors, or `mixers' For the past 65 years, the superheterodyne has dominated radio receiver technology. Although there has been a wide range of systems and configurations, all superhets change the frequency of the received signal by combining it with a locally generated oscillation, using devices known variously as mixers, first detectors, converters, modulators and translators. As would be expected, given its wide the valve where frequency conversion which as can be seen from Fig.1 was use and long history, the mixer has taken took place was the `First Detector', while remarkably complex. In fact without a many forms and has varied in complexi- the IF demodulator was the `Second few clues, the circuit operation is difficult ty from simple diodes through practical- Detector' . Although diodes could be to analyse. ly every valve type to specially made used, it was natural for the ubiquitous Briefly, the first valve is reflexed, func- octodes with six grids. Many converter grid leak detector to became the standard tioning as both an RF and first IF ampli- valves also had oscillator triodes in the superhet mixer. fier. The next valve also combines two same envelope. Some of these multi-grid These elementary converters needed operations, as a self-oscillating or mixers were the most complicated con- considerable taming. In the early period `Autodyne' mixer. The reason for this ventional valves made. following World War I Edwin complication was economy. TRF At first, mixers were simply standard Armstrong, following on his wartime receivers at the time had at most five detectors connected to an aerial by way work, set about making a practical super- valves, but a straight superhet needed of the usual tuned circuits to provide pre- het for RCA who by now practically eight far too expensive to be compet- selection, and coupled often by means monopolised the patents. -

Transmitters and Receivers: – AM Radio Transmitters – FM Transmitters – AM Receivers – FM Receivers – Problems

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY KAKINADA KAKINADA – 533 001 , ANDHRA PRADESH GATE Coaching Classes as per the Direction of Ministry of Education GOVERNMENT OF ANDHRA PRADESH Analog Communication 26-05-2020 to 06-07-2020 Prof. Ch. Srinivasa Rao Dept. of ECE, JNTUK-UCE Vizianagaram Analog Communication-Day 6, 31-05-2020 Presentation Outline Transmitters and Receivers: – AM Radio Transmitters – FM Transmitters – AM Receivers – FM Receivers – Problems 6/1/2020 Prof.Ch.Srinivasa Rao, JNTUK - UCEV 2 Learning Outcomes • At the end of this Session, Student will be able to: • LO 1 : Demonstrate the construction and operation of AM and FM Transmitters • LO 2 : Demonstrate the construction and operation of AM and FM Receivers • LO 3 : Image Frequency and its Rejection 6/1/2020 Prof.Ch.Srinivasa Rao, JNTUK - UCEV 3 AM Radio Transmitters • Transmitter must generate a signal with the right type of modulation, with sufficient power, at the right carrier frequency, and with reasonable efficiency. • Earlier, we have studied the basic concepts of amplitude modulation. Now, we are going to study the two basic topologies to generate and transmit amplitude modulated waves. They are 1. Low level modulation In low level modulation, the generation of AM wave takes place in the initial stage of amplification, i.e at a low power level. The generated AM signal then amplified using number of amplifier stages. 6/1/2020 Prof.Ch.Srinivasa Rao, JNTUK - UCEV 4 AM Low-Level Transmitter Figure: AM transmitter Block diagram with Low-Level Transmitter 6/1/2020 Prof.Ch.Srinivasa Rao, JNTUK - UCEV 5 Radio Transmitters Contd., 2. -

Local Oscillator and Focal Distance Measurement System for the Square Kilometre Array

University of Alberta Local Oscillator and Focal Distance Measurement System for the Square Kilometre Array Leonid Belostotski O A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science Department of Electrical and Cornputer Engineering Edmonton, Alberta Spnng 2000 National tibraiy Bibliothéque nationale du Canada Acquisitions and Acquisitions et Bibliographie Services seMces bibliographiques The author has granted a non- L'auteur a accordé une licence non exclusive licence allowing the exclusive permettant a la National Library of Canada to Biblioth6que nationale du Canada de reproduce, loan, distri'bute or seil reproduire, prêter, distri'buer ou copies of this thesis in microfom, vendre des copies de cette thèse sous paper or electronic formats. la forme de microfiche/nlm, de reproduction sur papier ou sur format électronique. The author retains ownefihip of the L'auteur conserve la propriété du copyright in this thesis. Neither the droit d'auteur qui protége cette thèse. thesis nor substantial exûacts fiorn it Ni la thèse ni des extraits substantiels may be printed or otherwise de celle-ci ne doivent être imprimés reproduced without the author's ou autrement reproduits sans son permi:ssion. autorisation. ABSTRACT A systern which sirnultaneously provides coherent local oscillator signal and mea- sures focal length for the Large Adaptive Reflector is discussed. The Local Oscillator subsystem provides a phasestable signal to an airborne platform over a radio Iink. A phase stability of 5"ms at 22 GHz is the goal for the system. Feedback is em- ployed to readjust the phase of the delivered signal, to compensate for changes in the transmission medium. -

Real-Time Detection of Radio Receivers Using Stimulated

Real-Time Detection of Radio Receivers Using Stimulated Emissions Colin Stagner, Christopher Osterwise, Daryl Beetner, and Steven Grant Missouri University of Science and Technology Introduction Challenges to Detection Simulated Performance RF Mixer IF Filter Local Oscillator Duty Cycle I Superheterodyne receivers can be Matched Filter Detector Periodogram Detector fH I Two-way radios are designed for GMRS LO Emissions, Unstimulated used to initiate explosive devices fRF fIF ROC: Matched Filter Detector with Simulated Noise ROC: Periodogram Detector with Simulated Noise f IF intermittent use 1400 1 ≥ -25 dB 1 I Potential threats can be detected by -15 dB fLO 1200 -30 dB ) locating radio receivers I Receiver deactivates its local ∆ 1000 0.8 0.8 -20 dB oscillator (LO) to conserve power 800 I Receivers use high-frequency 0.6 0.6 600 I There are no emissions of any kind -35 dB ≤ -25 dB signals in their RF mixers Magnitude ( 400 Variable Local Oscillator 0.4 0.4 when the LO is inactive 200 I These signals escape into the fIF = fRF − fLO Stimulation improves the duty cycle 0 True Positive Rate 0.2 -25 dB (area 1.00) True Positive Rate 0.2 -15 dB (area 0.99) environment as unintended I 0 100 200 300 400 500 600 -30 dB (area 0.96) -20 dB (area 0.82) Time (ms) -35 dB (area 0.54) -25 dB (area 0.55) fH = fRF + fLO I 20% when unstimulated 0 0 electromagnetic emissions [1, 2] 0 0.2 0.4 0.6 0.8 1 0 0.2 0.4 0.6 0.8 1 I 60% when stimulated False Positive Rate False Positive Rate Emissions’ Frequency Range I Quantitative improvements Unintended Emissions -

Subcarrier Modulation of a Reflex Klystron

, I - Document Room, IOBUMS3'T ROOM 36-41 Research Laboratory of Eltxrcic! Massachusetts Institute o echaleo SUBCARRIER MODULATION OF A REFLEX KLYSTRON J. JENSEN CoQY~~~~~~~~~~~~~~~~~~~~~~~~~~ TECHNICAL REPORT NO. 1, JANUARY 26, 1951 RESEARCH LABORATORY OF ELECTRONICS MASSACHUSETTS INSTITUTE OF TECHNOLOGY CAMBRIDGE, MASSACHUSETTS --- -- - I --- -- - - The research reported in this document was made possible through support extended the Massachusetts Institute of Tech- nology, Research Laboratory of Electronics, jointly by the Army Signal Corps, the Navy Department (Office of Naval Research) and the Air Force (Air Materiel Command), under Signal Corps Contract No. W36-039-sc-32037, Project No. 102B; Department of the Army Project No. 3-99-10-022. J I_ --- MASSACHUSETTS INSTITUTE OF TECHNOLOGY RESEARCH LABORATORY OF ELECTRONICS Technical Report No. 187 January 26, 1951 SUBCARRIER MODULATION OF A REFLEX KLYSTRON J. Jensen Abstract This report deals with a method of modulating a reflex klystron whereby the message to be transmitted is modulated on a subcarrier, which in turn modulates the klystron through its repeller. Of the resulting frequency spectrum only a narrow band, which contains the message, is transmitted. It is found that the message is contained in a frequency band centered locally about the first microwave sidebands, and in certain cases also about the microwave carrier. A theoretical analysis seems to indicate that the distortion introduced by transmitting only one of these local frequency bands can be made as small as desired under proper operating conditions, dependent upon the modula- tion index of the frequency-modulated klystron output. The power output obtainable by this method is considered, since the possibility of modulating microwave frequencies at high power levels is the main reason for studying this problem. -

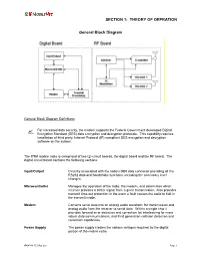

THEORY of OEPRATION General Block Diagram

SECTION 1: THEORY OF OEPRATION General Block Diagram General Block Diagram Definitions For increased data security, the modem supports the Federal Government developed Digital ? Encryption Standard (DES) data encryption and decryption protocols. This capability requires installation of third party, Internet Protocol (IP) compliant DES encryption and decryption software on the system. The IPM4 mobile radio is comprised of two (2) circuit boards, the digital board and the RF board. The digital circuit board contains the following sections: Input/Output Circuitry associated with the radio’s DB9 data connector providing all the RS232 data and handshake functions, including the necessary level changes. Microcontroller Manages the operation of the radio, the modem, and determines which receiver provides a better signal from a given transmission. Also provides transmit time-out protection in the event a fault causes the radio to halt in the transmit mode. Modem Converts serial data into an analog audio waveform for transmission and analog audio from the receiver to serial data. Within a single chip it provides forward error detection and correction, bit interleaving for more robust data communications, and third generation collision detection and correction capabilities. Power Supply The power supply creates the various voltages required by the digital portion of the mobile radio. IPM4748-FCCRpt.doc Page 1 SECTION 1: THEORY OF OPERATION The RF circuit board contains the following sections: Transmit Processing Circuitry that amplifies the analog audio signal from the modem and uses it to modulate the voltage controlled oscillator (VCO) and 10 MHz reference oscillator in the injection synthesizer section. Modulating the VCO and reference oscillator simultaneously results in a higher quality FM signal.