Digital Stop Watch System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

User's Guide 5636 (MTG)

MA2006-EA © 2020 CASIO COMPUTER CO., LTD. User’s Guide 5636 (MTG) ENGLISH Congratulations upon your selection of this CASIO watch. To ensure that this watch provides you with the years of service for which it is designed, carefully For details about how to use this watch and for read and follow the instructions in this manual, troubleshooting information, go to the website especially the information under “Operating below. Precautions” and “User Maintenance”. Be sure to keep all user documentation handy https://world.casio.com/manual/wat/ for future reference. x Keep the watch’s face exposed to light as much as possible (page E-5). Important! x For details about how to adjust the current time zone, time, and day settings, see “Timekeeping (Current Time and Day Adjustment)” (page E-6). E-1 Features The Bluetooth® word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by CASIO COMPUTER CO., LTD. is under license. Your watch provides you with the features and functions described below. This product has a Mobile Link function that lets it communicate with a Bluetooth® capable phone to perform automatic time adjustment and other operations. ◆ Solar powered operation ........................................................................................Page E-5 x This product complies with or has received approval under radio laws in various countries and The watch generates electrical power from sunlight and other types of light, and uses it to charge a geographic areas. Use of this product in an area where it does not conform to or where it has not battery that powers operation. -

Instructions Digital Atomic Watch

Instructions Digital Atomic Watch Introducing by ARCRON the world’s most accurate time keeping technology This wrist watch is a radio-controlled watch with SyncTime technology. A quartz oscillator, like most other modern clocks drives it. It has a built-in receiver to pick up the time signal broadcast from the U.S. Atomic Clock, which is operated by the National Institute of Science and Technology (NIST). This time protocol performs an internal check and, should any changes be necessary (e.g. Daylight Saving Time), corrects its internal time immediately. This check is carried out every day. This precise time information is also used to calibrate the internal oscillator, a feature only found in SyncTime time pieces. For these time pieces it is sufficient if a signal is received only every now and then. This gives you the added advantage of having the precise time even when traveling outside North America. SyncTime time pieces still run much more accurate than ordinary quartz clocks or even other radio-controlled clocks. Functions Your Chrono offers the following features: 1. Local Time in hours/minutes/seconds + Time Zone Indicator Date as Day of the week/month/day or World Time as UTC in h/min 2. Alarm 3. Date Alert The date alert is a silent alarm that flashes on the watch display on the day set, it continues to flash the entire day. 4. Time Zone display in three different ways: - indicator pointing to Time Zone in map - deviation from UTC in hours - Local Time in h/min/sec (manual adjustment to Daylight Saving Time possible) 5. -

TIME out Who Weighed About Three Hundred and fifty Pounds and His Two Grocery Carts Crammed with Bags of Tostitos and Bot- Confessions of a Watch Geek

ELECTRONICALLY REPRINTED FROM MARCH 20, 2017 rence. Since turning forty, I’d started to PERSONAL HISTORY suffer from a heightened sense of claus- trophobia. A few years ago, I was stuck for an hour in an elevator with a man TIME OUT who weighed about three hundred and fifty pounds and his two grocery carts crammed with bags of Tostitos and bot- Confessions of a watch geek. tles of Canada Dry, an experience both BY GARY SHTEYNGART frightening and lonely. The elevator had simply given up. What if a subway train also refused to move? I began walking seventy blocks at a time or splurging on taxis. But on this day I had taken the N train. Somewhere between Forty- ninth Street and Forty-second Street, a signal failed and we ground to a halt. For forty minutes, we stood still. An old man yelled at the conductor at full vol- ume in English and Spanish. Time and space began to collapse around me. The orange seats began to march toward each other. I was no longer breathing with any regularity. This is not going to end well. None of this will end well. We will never leave here. We will always be underground. This, right here, is the rest of my life. I walked over to the conduc- tor’s silver cabin. He was calmly explain- ing to the incensed passenger the scope of his duties as an M.T.A. employee. “Sir,” I said to him, “I feel like I’m dying.” “City Hall, City Hall, we got a sick passenger,” he said into the radio. -

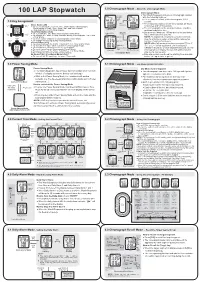

100 LAP Stopwatch

5.0 Chronograph Mode - About the Chronograph Mode 100 LAP Stopwatch Chronograph Mode ● This Watch/Stopwatch includes a chronograph function with the following features: ● The measurement unit of the chronograph: 1/100 1.0 Key Assignment second. ● The measuring capacity of the chronograph: 23 hours, Mode Button [M] ● To select among the Current Time, Daily Alarm, Chronograph, 59 minutes and 59.99 seconds. Chronograph Recall, Timer, Dual Time and Pacer Mode. ● The Chronograph can be used to measure: Lap time, ● Hold down to select setting display. split time/cumulative time. Start/Stop Button [S/S] ● Lap memory: Maximum 100 lap memories (see below ● To Turn ON/OFF the daily alarm in Daily Alarm Mode. ● To activate the 'start' or 'stop' function during Chronograph, Timer and note); Maximum 30 segments. Pacer Mode. NOTE: As registered a segment consumes memory, ● To recall target segment in Chronograph Recall Mode. thus the effective number of laps will be reduced as ● To change the setting during setting display. number of segment increases. Reset Button [L/R] ● To select between the Alarm 1 and Alarm 2 in Daily Alarm Mode. NOTE: When all memory has been occupied ('Free 0', ● To activate the 'lap' / 'save' function in Chronograph Mode. 'S--', or 'L---' will be appeared), the chronograph ● To activate the 'reload' function in Timer Mode. CANNOT record lap or save segment anymore, i.e.The ● To recall target lap in Chronograph Recall Mode. chronograph can display the lap and split/cumulative ● To select between the Timer 1 and Timer 2 in Timer Mode. ● To change the setting during setting display. -

Congratulations on Owning Your New Nautica Watch

CONGRATULATIONS ON OWNING YOUR NEW NAUTICA WATCH DEVELOPED FROM ADVANCED ELECTRONICS TECHNOLOGY, THE MOVEMENT IS MANUFACTURED FROM THE BEST QUALITY COMPONENTS AND POWERED BY A LONG LIFE BATTERY. NAUTICA watches have been developed with the highest attention to quality, function and detail, as befits the NAUTICA tradition. Please read the following instructions carefully to fully understand all of the functions of your finely crafted timepiece. WATER-RESISTANCE If your watch is water-resistant, it will be indicated on the watch face or on the caseback. • 50 Meter Water-Resistant watch withstands water pressure to 86p.s. i.a. (equals immersion to 164 feet or 50 meters below sea level) and dust as long as crystal, crown and case remain intact. • 100 Meter Water-Resistant watch withstands water pressure to 160p. s.i.a. (equals immersion to 328 feet or 100 meters below sea level) and dust as long as crystal, crown and case remain intact. • 200 Meter Water-Resistant watch withstands water pressure to 320p. s.i.a. (equals immersion to 656 feet or 200 meters below sea level) and dust as long as crystal, crown and case remain intact. NOTE: CROWN MUST BE SCREWED INTO THE CASE PROTRUSION TO ASSURE WATER RESISTANCE. INDIGLO® NIGHT-LIGHT If your watch has “INDIGLO” on the dial, your watch is equipped with the INDIGLO Night-Light. To activate this feature, depress the crown or the pusher on the left side of the watch to illuminate the entire dial for easy reading during nighttime or low light conditions. Light will appear immediately. Your NAUTICA watch featuring INDIGLO Night-Light contains a patented electroluminescent technology (U.S. -

Time and Frequency Users Manual

A 11 10 3 07512T o NBS SPECIAL PUBLICATION 559 J U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards Time and Frequency Users' Manual NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act of Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is per- formed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; develops, produces, and distributes Standard Reference Materials; and provides -

Lab 2: 8051-Based Timer and Stopwatch

Lab 2: 8051-Based Timer and Stopwatch ENGR 323: Microoprocessor Systems Prof. Taikang Ning Submitted by: Vishal Bharam and Bicky Shakya Introduction In the current digital age, microcontrollers have become an indispensible technological tool. Microcontrollers are single chip computers that are embedded into other systems, which can perform multiple complicated operations at the same time. In addition, microcontrollers have high integration of functionality, field programmability and are very easy to use. These features have helped microcontrollers to find a wide spectrum of applications, in the field of automobiles, video games, manufacturing industries and many others. Among all the microcontrollers in use today, the 8051 and its variations are considered the most popular. Problem Statement In this lab, we will use the popular 8-bit 8051 microcontroller to design a system to perform time-count. The timer is equipped with four 7-segment displays that will count from 00:00 to 59:59 and then reset back to counting from 00:00. The extension of the first lab will require us to include a stop-watch mode in our system. The final system should meet the following requirements: • To count minutes and seconds from 00:00 (out of reset) to 59:59 and repeat the counting after every full hour (completed in the first lab) • To allow external controls/interrupts to emulate a stopwatch which can reset, start and freeze counts by the 100th of a second. Specific Design Goals As mentioned already, the primary objective of the first laboratory is to design a digital clock on a 4 LED display using 8-bit 8051 microcontroller. -

You Are Now the Proud Owner of a SEIKO 1/100-Second Retrograde Chronograph Cal

You are now the proud owner of a SEIKO 1/100-Second Retrograde Chronograph Cal. 7T82. For best results, please read the instructions in this booklet carefully before using your SEIKO Analogue Quartz Watch. Please keep this manual handy for ready reference. Es usted ahora el orgulloso propietario del Cronógrafo Retrógrado de 1/100 de Segundo de SEIKO, Cal. 7T82. Para óptimo resultado, lea detenidamente las instrucciones de este folleto antes de usar el reloj. Guarde este manual para consulta posterior. ENGLISH English CONTENTS Page FEATURES ............................................................................................................... 4 SCREW DOWN CROWN ......................................................................................... 6 TIME AND CALENDAR SETTING AND STOPWATCH HAND POSITION ADJUSTMENT ..................................................... 7 HOW TO USE THE STOPWATCH ........................................................................... 12 DEMONSTRATION FUNCTION OF THE STOPWACH HAND MOVEMENT ........... 16 TACHYMETER (for models with tachymeter scale on the dial) ............................... 17 TELEMETER (for models with telemeter scale on the dial) ..................................... 19 BATTERY CHANGE .................................................................................................. 21 NECESSARY PROCEDURE AFTER BATTERY CHANGE ......................................... 23 TROUBLESHOOTING ............................................................................................. -

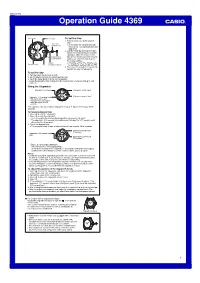

Operation Guide 4369

MA0508-EA Operation Guide 4369 Hour hand Minute hand To set the time 1. Pull the crown out to the second click. First click • (Setting day) At this time, the second hand will move to the 12 o’clock position and stop there. 2. Set the hands by rotating the crown. Rotate the crown to move the hands clockwise. Move the minute hand Second click four or five minutes past the time you (Setting time) want to set, and then back it up to the proper setting. Crown • Carefully set the time, making sure Second hand Day (Normal position) to distinguish between AM and PM. 3. Push the crown back in to the normal position to restart timekeeping. To set the day 1. Pull the crown out to the first click. 2. Set the day by rotating the crown towards you. 3. Push the crown back in to the normal position. • Avoid changing the date setting while the current time is between 9:00 p.m. and 1:00 a.m. Using the Stopwatch Stopwatch hour hand Stopwatch minute hand Stopwatch second hand Stopwatch 1/20 second hand *This hand rotates and indicates the 1/20 second count during the first 30 seconds. The stopwatch lets you measure elapsed time up to 11 hours, 59 minutes, 59.95 seconds. To measure elapsed time 1. Press A to start the stopwatch. 2. Press A to stop the stopwatch. • You can resume the measurement operation by pressing A again. The stopwatch 1/20 second hand rotates and indicates the 1/20 second count during the first 30 seconds. -

How Geoscience Novices Reason About Temporal Duration: the Role of Spatial Thinking and Large Numbers Kim A

JOURNAL OF GEOSCIENCE EDUCATION 61, 334–348 (2013) How Geoscience Novices Reason About Temporal Duration: The Role of Spatial Thinking and Large Numbers Kim A. Cheek1,a ABSTRACT Research about geologic time conceptions generally focuses on the placement of events on the geologic timescale, with few studies dealing with the duration of geologic processes or events. Those studies indicate that students often have very poor conceptions about temporal durations of geologic processes, but the reasons for that are relatively unexplored. Close connections between ideas about time and space over short time periods, as well as poor number sense for numbers in unfamiliar ranges have been repeatedly demonstrated. This study explored whether the conceptions geoscience novices hold about the temporal duration of geoscience processes across a variety of temporal scales are influenced by their ideas about space and large numbers. Seventeen undergraduates in an introductory geoscience course participated in task-based qualitative interviews. Students tended to equate spatial size with temporal duration over short and long time periods, sometimes modifying contradictory data to fit their interpretation. Confusion about the relative size of temporal periods up to 100,000,000 years was observed. They described durations operating on long temporal scales in largely qualitative, imprecise terms. Spatial compression of large temporal periods and expansion of short time periods were common. Students possessed few specific temporal markers for durations of task events. Specific pedagogical and curricular recommendations are discussed. Ó 2013 National Association of Geoscience Teachers. [DOI: 10.5408/12-365.1] Key words: duration, geologic time, large numbers, spatial, temporal INTRODUCTION time period required for a geologic process or event to occur Geologic time is a fundamental idea that undergirds (e.g., the assemblage of Pangea took place over ~100 My). -

Operation Guide 5522

MA1609-EA © 2016 CASIO COMPUTER CO., LTD. Operation Guide 5522 ENGLISH Congratulations upon your selection of this CASIO watch. E-1 About This Manual Things to check before using the watch x Depending on the model of your watch, display text 1. Check the Home City and the daylight saving time (DST) setting. appears either as dark figures on a light background, or light figures on a dark background. All sample displays Use the procedure under “To configure Home City settings” (page E-18) to configure in this manual are shown using dark figures on a light your Home City and daylight saving time settings. background. Important! Button operations are indicated using the letters shown x x Proper World Time Mode data depends on correct Home City, time, and date in the illustration. settings in the Timekeeping Mode. Make sure you configure these settings x Note that the product illustrations in this manual are correctly. intended for reference only, and so the actual product may appear somewhat different than depicted by an 2. Set the current time. illustration. x See “Adjusting the Digital Time and Date Settings” (page E-21). The watch is now ready for use. E-2 E-3 Contents Using the Stopwatch . E-25 To enter the Stopwatch Mode . E-26 About This Manual . .E-2 To perform an elapsed time operation . E-28 To pause at a split time . E-28 Things to check before using the watch . E-3 To measure two finishes . E-28 Mode Reference Guide . E-8 To set a target time . -

Service Category : Calibration of Stopwatch

Service category : Calibration of Stopwatch Basic information Quantity Time interval Instrument or Artifact Stopwatch Instrument Type or Method Time interval measurement Measurand Level or Range 0.01 to 100000 s Measurement Conditions Number of measurements = 10 Instruments Atomic Clock (Model : Agilent 5071A) Frequency Distribution Amplifier (Model : HP 5087A) Universal Counter (Model : Agilent 53131A) Stopwatch Calibrator (Model : NML-SIRIM) Measurement configuration 10 MHz Reference Universal Counter start stop Frequency Distribution Stopwatch Calibrator Amplifier start stop GPIB Caesium Clock Stopwatch List of uncertainties 1. Uncertainty of Caesium Clock 2. Cable Uncertainty 3. Frequency Distribution Amplifier Uncertainty 4. Universal Counter Uncertainty 5. Stopwatch Calibrator Uncertainty 6. Display Resolution of Stopwatch Page 1 of 7 Details of Uncertainty Calculations 1) Values taken from Agilent 5071A (High Performance) specifications. 2) Referring to Appendix in Figure 3, we extrapolate using a line with slope τ-1 to get the uncertainty of the cable in the worst case event of 7C change at 100000 s observation time. 3) From the measurement results at 100000 s observation time which are shown in Figure 5 in the Appendix. 4) Calculated based on equation and value taken from Agilent 53131A specifications, as follow: 15mV (1%xStart Trigger Lev elSetting) Trigger Level Timing Error Input Slew Rateat StartTrigger Point 15mV (1%xStop Trigger Lev elSetting) Input Slew Rateat StopTrigger Point 15mV (1%x 2.5V) 15mV (1%x