Final Program

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Oriented Conferences Four Solutions

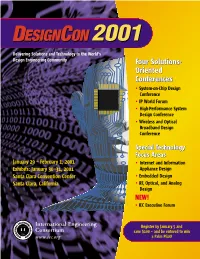

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

Android in the Cloud on Arm Native Servers

Android in the Cloud on Arm Native Servers Introduction All the chatter about Arm servers and the role of Android in the cloud in recent years generates questions about what these things could mean for a largely mobile based platform like Arm/Android. This whitepaper examines the practical and commercial use cases that are driving a new paradigm linking the primary mobile and embedded computing platform in the world today with its new cousin in cloud infrastructure: Arm servers + virtualization + native Android execution. While detailing the use cases driving a mobile platform migration to cloud infrastructure, this whitepaper also showcases the solution that Ampere Computing, Canonical, and NETINT Technologies have partnered to produce addressing this migration. The solution is a stellar example of how a service provider or developer can take advantage of Arm native computing in a cloud context to bring together an ecosystem of over 3M primarily mobile apps integrated with benefits from a cloud enabled infrastructure. A case study around cloud gaming fills in the practical real-world considerations of this hot new paradigm. Cloud gaming really showcases the advantages of all the solution components the partners have integrated to make a scalable, efficient cloud resource available to a new class of cloud-native applications catering to the billions of users with Arm based devices worldwide. The whitepaper concludes with thoughts and predictions about the evolution of this new paradigm as hardware and software components mature in the coming years. A New Paradigm The Arm architecture has dominated the mobile processor market with its unrivaled ability to maximize power-efficiency. -

ISSCC 2022 INTELLIGENT SILICON for a SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks

ISSCC 2022 INTELLIGENT SILICON FOR A SUSTAINABLE WORLD February 20-24, 2022 | San Francisco Marriott Marquis | San Francisco, California, USA Plenary Talks ClassicMoore to SysMoore, The Future of the Intelligent Sensing: Power, Energy, High Performance Semiconductor Enabling the Next and the Si Saturation: all we need is a 1000X… Industry and Design “Automation Age” Design What and How? Aart de Geus Renée James Marco Cassis Inyup Kang Founder, Chairman and Founder, Chairman, and CEO, President, Sales, Marketing, Communications President and General Manager of co-Chief Executive Officer, Synopsys Ampere Computing and Strategy Development STMicroelectronics System LSI Business at Samsung Electronics Tutorials Student Activities Analog Circuit Design in Bipolar-CMOS-DMOS (BCD) Technologies Student Research Preview (SRP): Short Presentations w/ Poster Session Marco Berkhout, Goodix Technology, Nijmegen, The Netherlands Silkroad Award: Scholarships awarded for Far-East full-time students Fundamentals of High Frequency DC-DC Converters Kousuke Miyaji, Shinshu University, Nagano, Japan Invited Industry Track Noise-Shaping SAR ADCs Two Invited Industry tracks will highlight recent hot-product releases and discuss innovative ways they solved Yun-Shiang Shu, MediaTek, Hsinchu City, Taiwan product-level challenges. The focus this year is on Digital/ML, Systems and Quantum Computing. Fundamentals of Self-Sensing Processing Systems Special Events Shidhartha Das, Arm, Cambridge, United Kingdom Fundamentals of Process Monitors for Signoff-Oriented Circuit Next Gen Circuit Designer Workshop The Next Gen Circuit Designer Workshop 2022 is an educational workshop for EE undergraduates and early graduate students Design (Master's students/1-2 years of PhD) who are interested in choosing a career in integrated circuit (IC) design. -

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures

NVIDIA and Tech Leaders Team to Build GPU-Accelerated Arm Servers for New Era of Diverse HPC Architectures Arm, Ampere, Cray, Fujitsu, HPE, Marvell to Build NVIDIA GPU-Accelerated Servers for Hyperscale-Cloud to Edge, Simulation to AI, High-Performance Storage to Exascale Supercomputing SC19 -- NVIDIA today introduced a reference design platform that enables companies to quickly build GPU-accelerated Arm®-based servers, driving a new era of high performance computing for a growing range of applications in science and industry. Announced by NVIDIA founder and CEO Jensen Huang at the SC19 supercomputing conference, the reference design platform -- consisting of hardware and software building blocks -- responds to growing demand in the HPC community to harness a broader range of CPU architectures. It allows supercomputing centers, hyperscale-cloud operators and enterprises to combine the advantage of NVIDIA's accelerated computing platform with the latest Arm-based server platforms. To build the reference platform, NVIDIA is teaming with Arm and its ecosystem partners -- including Ampere, Fujitsu and Marvell -- to ensure NVIDIA GPUs can work seamlessly with Arm-based processors. The reference platform also benefits from strong collaboration with Cray, a Hewlett Packard Enterprise company, and HPE, two early providers of Arm-based servers. Additionally, a wide range of HPC software companies have used NVIDIA CUDA-X™ libraries to build GPU-enabled management and monitoring tools that run on Arm-based servers. “There is a renaissance in high performance computing,'' Huang said. “Breakthroughs in machine learning and AI are redefining scientific methods and enabling exciting opportunities for new architectures. Bringing NVIDIA GPUs to Arm opens the floodgates for innovators to create systems for growing new applications from hyperscale-cloud to exascale supercomputing and beyond.'' Rene Haas, president of the IP Products Group at Arm, said: “Arm is working with ecosystem partners to deliver unprecedented performance and efficiency for exascale-class Arm-based SoCs. -

Organising Committees

DATE 2005 Executive Committee GENERAL CHAIR PROGRAMME CHAIR Nobert Wehn Luca Benini Kaiserslautern U, DE DEIS – Bologna U, IT VICE CHAIR & PAST PROG. CHAIR VICE PROGRAMME CHAIR Georges Gielen Donatella Sciuto KU Leuven, BE Politecnico di Milano, IT FINANCE CHAIR PAST GENERAL CHAIR Rudy Lauwereins Joan Figueras IMEC, Leuven, BE UP Catalunya, Barcelona, ES DESIGNERS’ FORUM DESIGNERS’ FORUM Menno Lindwer Christoph Heer Philips, Eindhoven, NL Infineon, Munich, DE SPECIAL SESSIONS & DATE REP AT DAC FRIDAY WORKSHOPS Ahmed Jerraya Bashir Al-Hashimi TIMA, Grenoble, FR Southampton U, UK INTERACTIVE PRESENTATIONS ELECTRONIC REVIEW Eugenio Villar Wolfgang Mueller Cantabria U, ES Paderborn U, DE WEB MASTER AUDIO VISUAL Udo Kebschull Jaume Segura Heidelberg U, DE Illes Baleares U, ES TUTORIALS & MASTER COURSES FRINGE MEETINGS Enrico Macii Michel Renovell Politecnico di Torino, IT LIRMM, Montpellier, FR AUTOMOTIVE DAY BIOCHIPS DAY Juergen Bortolazzi Christian Paulus DaimlerChrysler, DE Infineon, Munich, DE PROCEEDINGS EXHIBITION PROGRAMME Christophe Bobda Juergen Haase Erlangen U, DE edacentrum, Hannover, DE UNIVERSITY BOOTH UNIVERSITY BOOTH & ICCAD Volker Schoeber REPRESENTATIVE edacentrum, Hannover, DE Wolfgang Rosenstiel Tuebingen U/FZI, DE AWARDS & DATE REP. AT ASPDAC PCB SYMPOSIUM Peter Marwedel Rainer Asfalg Dortmund U, DE Mentor Graphics, DE TRAVEL GRANTS COMMUNICATIONS Marta Rencz Bernard Courtois TU Budapest, HU TIMA, Grenoble, FR LOCAL ARRANGEMENTS PRESS LIASON Volker Dueppe Fred Santamaria Siemens, DE Infotest, Paris, FR ESF CHAIR & EDAA -

Exhibition Report

Exhibition Report Japan Electronics and Information Technology Industries Association (JEITA) Contents Exhibition Outline 1 Exhibition Configuration 2 1. Scope of Exhibits 2 2. Conference 2 3. Number of Exhibitors and Booths 2 4. Suite Exhibits 2 5. Exhibitors 3 Conference Activities 4 1. Exhibitor Seminars 4 2. Keynote Speech 4 3. Special Event Stage 4 4. The 13th FPGA/PLD Design Conference 4 5. FPGA/PLD Design Conference User’s Presentations 4 6. IP(Intellectual Property) Flea Market in EDSFair 4 7. System Design Forum 2006 Conference 4 Other Events and Special Projects 5 1. Opening Ceremony 5 2. University Plaza 5 3. Venture Conpany Pavilion 5 4. EDAC Reception 5 5. Press 5 Number of Visitors 6 Results of Visitor Questionnaire 6-7 Exhibition Outline Name . Electronic Design and Solution Fair 2006 (EDSFair2006) Duration . Thursday, January 26 and Friday, January 27, 2006 (2 days) 10:00 a.m. to 6:00 p.m. Location . Pacifico Yokohama (Halls C-D hall and Annex Hall) 1-1-1 Minato Mirai, Nishi-ku, Yokohama 220-0012, Japan Admission. Exhibition: Free (registration required at show entrance) Conference: Fees charged for some sessions Sponsorship . Japan Electronics and Information Technology Industries Association (JEITA) Cooperation . Electronic Design Automation Consortium (EDAC) Support . Ministry of the Economy, Trade and Industry, Japan (METI) Embassy of the United States of America in Japan Distributors Association of Foreign Semiconductors (DAFS) City of Yokohama Assistance . Institute of Electronics, Information and Communication Engineers (IEICE) Information Processing Society of Japan (IPSJ) Japan Printed Circuit Association (JPCA) Spacial Assistance. Hewlett-Packard Japan, Ltd. Sun Microsystems K.K Management . -

28Th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010

28th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010 Preliminary Program (as of 3/25/10) Monday, 4/19/10 Plenary Session (9:00 – 11:00) Break (11:00 – 11:15) Sessions 1 (11:15 – 12:15) Session 1A: Delay & Performance Test 1 Moderator: M. Batek - Broadcom Fast Path Selection for Testing of Small Delay Defects Considering Path Correlations Z. He, T. Lv - Institute of Computing Technology, H. Li, X. Li - Chinese Academy of Sciences Identification of Critical Primitive Path Delay Faults without any Path Enumeration K. Christou, M. Michael, S. Neophytou - University of Cyprus Path Clustering for Adaptive Test T. Uezono, T. Takahashi - Tokyo Institute of Technology, M. Shintani , K. Hatayama - Semiconductor Technology Academic Research Center, K. Masu - Tokyo Institute of Technology, H. Ochi, T. Sato - Kyoto University Session 1B: Memory Test & Repair Moderator: P. Prinetto - Politecnico di Torino Automatic Generation of Memory Built-In Self-Repair Circuits in SOCs for Minimizing Test Time and Area Cost T. Tseng, C. Hou, J. Li - National Central University Bit Line Coupling Memory Tests for Single Cell Fails in SRAMs S. Irobi, Z. Al-ars, S. Hamdioui - Delft University of Technology Reducing Test Time and Area Overhead of an Embedded Memory Array Built-In Repair Analyzer with Optimal Repair Rate J. Chung, J. Park - The University of Texas at Austin, E. Byun, C. Woo - Samsung Electronics, J. Abraham - The University of Texas at Austin IP Session 1C: Innovative Practices in RF Test Organizer: R. Parekhji - Texas Instruments Moderator: TBA Test Time Reduction Using Parallel RF Test Techniques R. -

PLM Industry Summary Editor: Christine Bennett Vol

PLM Industry Summary Editor: Christine Bennett Vol. 11 No. 4 Friday 23 January 2009 Contents Acquisitions _______________________________________________________________________ 2 Autodesk Completes Acquisition of ALGOR, Inc. _____________________________________________2 Mentor Graphics Extends High Level Synthesis Leadership with Acquisition of Agility Design Solutions Inc. C Synthesis Suite ____________________________________________________________________3 Company News _____________________________________________________________________ 3 Anark Names Chris Garcia Senior Vice President, Business Development ___________________________3 Autodesk Manufacturing Community to Select 2008 Inventor of the Year Award Winner ______________4 Delcam Offers Free ArtCAM Demo Software for Artistic Users __________________________________5 DP signs Agreement with Italian Lathe Manufacturer GRAZIANO Tortona S.r.l. _____________________6 DP Technology Moves its Midwest Team to a Larger, New and Improved Site _______________________6 DP Technology Signs Agreement with Italian Machine-Tool Builder Salvadeo S.r.l. __________________7 Kalypso and Endeca Announce Partnership in Support of Engineering and PLM-Related Information Visibility Solutions ______________________________________________________________________7 New WorkXPlore 3D Website Allows Engineers to Download High Speed Collaborative CAD Viewer Free _____________________________________________________________________________________8 Si2’s Open Modeling Coalition Releases Document on Statistical -

OCP19 DRAFT Prospectus 081418

OCP GLOBAL SUMMIT | March 14–15, 2019 San Jose McEnery Convention Center | San Jose, CA SPONSOR PROSPECTUS 2018 OCP Global Summit Stats Attendees by Organizational Role Analyst 4% Marketer 7% Technology Engineer Architect 30% 11% Product Manager 12% Senior Business Executive Development/ 19% Account Manager 17% 3,441 813 100+ Companies Summit Attendees Media/Analysts Represented 81 34 Sponsors/ Countries Exhibitors Represented Page !2 of !19 Previous Summit Exhibitors and Sponsors OCP Global Summit 2018 - San Jose, CA 10Gtek Edgecore Networks Liqid Inc. Radisys Corporation 3M Eoptolink Liquid Telecom Rittal ADC Technologies Inc. Facebook LITE-On Storage Samsung ADLINK Technology Fadu LTO Ultrium Program Samtec Advanced Micro Devices, Fidelity Marvell Schneider Electric Inc. (AMD) Ampere Computing Finisar Mellanox Seagate Amphenol Flex Micron SK hynix Apstra Geist Microsoft Solarflare Artesyn Geist Global Mojo Networks Starline (Universal Electric Corp) ASRock Rack GIGABYTE Murata TE Connectivity Barefoot Networks Gigalight Nephos Inc. Telecom Infra Project (TIP) Bel Power Solutions HPE NGD Systems The Linux Foundation Big Switch Networks Huawei Nimbus Data TidalScale Cambridge Industries Hyve Solutions Nokia Toshiba Memory USA, Inc. America, Inc. Cavium Innovium OpenCAPI Consortium Vertiv ColorChip Inspur OpenPower Wave 2 Wave Solutions Lmtd. Cumulus Intel OpenStack Wiwynn DCD IP Infusion, Inc. OpenSwitch ZT Systems Dell EMC Ixia Penguin Delta Jess-link Products Co. Ltd. QCT/Quanta Distributed Management Lenovo Qualcomm Task Force (DMTF) -

SPONSORSHIP PROSPECTUS March 4–5, 2020 | San Jose Mcenery Convention Center | San Jose, California 2019 OCP Global Summit Stats

2020 OCP GLOBAL SUMMIT SPONSORSHIP PROSPECTUS March 4–5, 2020 | San Jose McEnery Convention Center | San Jose, California 2019 OCP Global Summit Stats Chart Title Analyst 4% Marketer 7% Technology Architect Engineer 11% 30% Product Manager 12% Business Senior Development Executive /Account 19% Manager 17% 3,600 727 100+ Summit Attendees Companies Media/Analysts Represented 77 42 Sponsors/ Countries Exhibitors Represented 2 Previous Summit Exhibitors and Sponsors 2019 OCP Global Summit - San Jose, CA 2CRSI Edgecore Networks Man Zai Industrial Co., Ltd. Schneider Electric 3M Eoptolink Marvell Seagate AMD Facebook Mellanox SK hynix Ampere Computing Finisar Micron SNIA Amphenol Flex Microsoft Starline AOI GIGABYTE MiTAC STORDIS GmbH Apstra HPE Molex Submer Immersion Cooling Arrcus Huawei Murata TE Connectivity Artesyn Hyve Solutions Nephos The Linux Foundation ASRock Rack Innovium Netronome TIP Auras Inspur Nokia Toshiba Barefoot Networks Intel OpenCAPI Vertiv Bel Power Solutions IT Renew OpenPOWER Western Digital Big Switch Networks Ixia, a Keysight Business OpenStack Wiwynn CIARA, a Hypertec Brand Juniper Networks Penguin Computing XCloud Networks CIG Lattice Semi QCT Xilinx Cumulus Networks Lenovo Rittal ZT Systems Dell LinkedIn Ruijie Networks Delta Electronics Americas Liqid Samsung DMTF Lite On Samtec 3 Schedule Overview* Day 1: Wednesday, March 4 Time Event 7:30am 9:00am Registration and Breakfast 9:00am 11:00am Keynotes 11:00am 12:00pm Expo Hall Open 12:00pm 2:00pm Lunch / Expo Hall Open / Expo Hall Talks 2:00pm 6:00pm Expo Hall Open -

LF Edge TAC Technical Advisory Council

LF Edge TAC Technical Advisory Council 21 October 2020 Meeting Details › October 21, 2020 (@ 7:00am PDT) › Meeting Info: › Join Zoom Meeting › https://zoom.us/j/286673048?pwd=REJlT1E2RmU3T3lpL0YrMzFHVVVsdz09 › › Meeting ID: 286 673 048 › Passcode: 254638 › › Dial by your location › 855 880 1246 US Toll-free › 877 369 0926 US Toll-free › Meeting ID: 286 673 048 › Find your local number: https://zoom.us/u/aeeh8taqXU Antitrust Policy Notice › Linux Foundation meetings involve participation by industry competitors, and it is the intention of the Linux Foundation to conduct all of its activities in accordance with applicable antitrust and competition laws. It is therefore extremely important that attendees adhere to meeting agendas, and be aware of, and not participate in, any activities that are prohibited under applicable US state, federal or foreign antitrust and competition laws. › Examples of types of actions that are prohibited at Linux Foundation meetings and in connection with Linux Foundation activities are described in the Linux Foundation Antitrust Policy available at http://www.linuxfoundation.org/antitrust-policy. If you have questions about these matters, please contact your company counsel, or if you are a member of the Linux Foundation, feel free to contact Andrew Updegrove of the firm of Gesmer Updegrove LLP, which provides legal counsel to the Linux Foundation. 8/28/20 3 LF Edge TAC Project/ Representative Named Alternate Project/ Representative Named Alternate Member Member Altran Shamik Mishra Nilanjan Samajdar GE Research Joel Markham James Ward Arm Reed Hinkel Tina Tsou HP Inc. Henry Lau AT&T Kandan Kathirvel HPE Rodney Richter Arun Thulasi Baidu Leding Li Huawei JianGuo Zeng Gabriel Yuyang Charter Jeffrey Saelens Mohammad IBM Joseph Pearson Ryan Anderson Zebetian Dell David Lake Trevor Conn Intel Jim St. -

When Innovation Is Hard

WhenWhen InnovationInnovation isis HardHard Does the Open Source Development Model Work in Hardware? ilkka.tuomi meaningprocessing.com © I. Tuomi 2 Oct. 2008 page: 1 ThesesTheses • 1. Software and hardware are epistemologically different artifacts • This leads to different innovation and conflict models in software and hardware projects • The success of the open distributed approach in ”close-to-hardware” software development (e.g. Linux kernel) is partly explained by this epistemological difference • 2. Close-to-hardware software, social software, and hardware are different • Close-to-hardware software development is easy to distribute because the developer community consists of a homogenous network of people and tools • There exists a ”phenomenological bottleneck:” Real hardware can only be approximated using digital representations; distributed hardware projects can therefore be really hard • There also exists a ”political bottleneck:” Social software can be hard as there are multiple interpretations and systems of meaning © I. Tuomi 2 Oct. 2008 page: 2 DifferentDifferent TypesTypes ofof AnimalsAnimals RequireRequire DifferentDifferent StylesStyles ofof BreedingBreeding • Close-to-hardware SW • HW • In a given HW environment: • The context is the open world: SW is both the description and the Unmodeled features matter implementation Systems wear, tear and break down Mapping between software and the Although dominant voices are loudest, functionality of the system is one-to-one evaluation criteria have to be negotiated Technical functionality can be empirically from multiple perspectives tested • A homogenous developer community, • A homogenous developer community, rooted in its own ”objective reality.” rooted in its own ”professional reality.” or: • A network of interacting communities, each with their own stocks of knowledge.