The Alphaserver 4100 Cached Processor Module Architecture And

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Alphaserver 4000/4100 Configuration and Installation Guide

AlphaServer 4000/4100 Configuration and Installation Guide Order Number: EK–4100A–CG. E01 This manual is for manufacturing and field personnel, and resellers who require AlphaServer 4000/4100 system drawer configuration information. Digital Equipment Corporation Maynard, Massachusetts First Printing, June 1997 Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description. The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies. Copyright 1997 by Digital Equipment Corporation. All rights reserved. The following are trademarks of Digital Equipment Corporation: AlphaServer, OpenVMS, StorageWorks, VAX, and the DIGITAL logo. The following are third-party trademarks: UNIX is a registered trademark in the U.S. and other countries, licensed exclusively through X/Open Company Ltd. Windows NT is a trademark of Microsoft, Inc. All other trademarks and registered trademarks are the property of their respective holders. FCC Notice: The equipment described in this manual generates, uses, and may emit radio frequency energy. -

HS1CP Device Channel Processor Operating Software HSOF V3.1

TM HS1CP Device Channel Processor Operating Software HSOF Version 3.1 Release Notes Order Number: EK−HS1CP−RN. E01 This document summarizes features and characteristics of the HS1CP Device Channel Processor operating software Version 3.1 that are not covered elsewhere in the documentation. These release notes also contain instructions for installing the software. _____________________________ Note____________________________ These Release Notes contain instructions for C_SWAP and HSUTIL that supersede information in the product documentation. Keep these Release Notes near your StorageWorks subsystem. ______________________________________________________________ Software Version: HSOF V3.1 Digital Equipment Corporation Maynard, Massachusetts April 1997 While Digital Equipment Corporation believes the information included in this manual is correct as of the date of publication, it is subject to change without notice. DIGITAL makes no representations that the interconnection of its products in the manner described in this document will not infringe existing or future patent rights, nor do the descriptions contained in this document imply the granting of licenses to make, use, or sell equipment or software in accordance with the description. No responsibility is assumed for the use or reliability of firmware on equipment not supplied by DIGITAL or its affiliated companies. Possession, use, or copying of the software or firmware described in this documentation is authorized only pursuant to a valid written license from DIGITAL, an authorized sublicensor, or the identified licensor. Commercial Computer Software, Computer Software Documentation and Technical Data for Commercial Items are licensed to the U.S. Government with DIGITAL’s standard commercial license and, when applicable, the rights in DFAR 252.227-7015, “Technical Data—Commercial Items.” © Digital Equipment Corporation 1997. -

Xa9846175 Indc(Nds)

XA9846175 international Atomic Energy Agency INDC(NDS)-374 Distr. G, NC I N DC INTERNATIONAL NUCLEAR DATA COMMITTEE Report on the Consultants' Meeting on CO-ORDINATION OF THE NUCLEAR REACTION DATA CENTERS (Technical Aspects) IAEA Headquarters, Vienna, Austria 26-28 May 1997 Edited by O. Schwerer and H. Wienke October 1997 IAEA NUCLEAR DATA SECTION, WAGRAMERSTRASSE §, A-1400 VIENNA Reproduced by the IAEA in Austria October 1997 INDC(NDS)-374 Distr. G, NC Report on the Consultants' Meeting on CO-ORDINATION OF THE NUCLEAR REACTION DATA CENTERS (Technical Aspects) IAEA Headquarters, Vienna, Austria 26-28 May 1997 Edited by O. Schwerer and H. Wienke October 1997 Contents Introduction 7 The Network of Nuclear Reaction Data Centers 9 List of Acronyms 11 Agenda 13 List of Participants 15 Conclusions and Actions 17 Appendix 1 Agreement on Charged-Particle Data Compilation Responsibility 25 Status Reports Rl Nuclear Data Section 27 R2 RIKEN 41 R3 JCPRG 43 R4 CAJAD 47 R5 NDG-VNIIEF 51 R6 CNDC 53 R7 CJD 57 R8 NEA Data Bank 59 R9 ATOMKI 67 RIO NNDC 73 Selected Working Papers 77 NEXT PAQE(S) left BLANK -7- IAEA Consultants' Meeting on Co-ordination of the Nuclear Reaction Data Centers (Technical Aspects) IAEA Headquarters, Vienna, Austria 26-28 May 1997 Introduction The IAEA Nuclear Data Section convenes in annual intervals coordination meetings of the Network of the Nuclear Reaction Data Centers. The last meeting, with center heads and technical staff present, took place in Brookhaven, USA, 3-7 June 1996. See the report INDC(NDS)-360. The present meeting was attended by technical staff only to discuss technical matters of the nuclear data compilation and exchange by means of the jointly operated computerized systems CINDA, EXFOR, ENDF and others. -

HP Openvms Cluster Software SPD 29.78.27

Software Product Description PRODUCT NAME: HP OpenVMS Cluster Software SPD 29.78.27 This Software Product Description describes Versions a mix of AlphaServer and VAX or AlphaServer and In- 6.2–1H3, 7.1–1H1, 7.1–1H2, 7.1–2, 7.2, 7.2–1, 7.2– tegrity server systems. In this SPD, this environment is 1H1, 7.2-2, 7.3, 7.3–1, 7.3–2, 8.2, 8.2–1 and 8.3 of the referred to as an OpenVMS Cluster system. following products: Systems in an OpenVMS Cluster system can share pro- • HP VMScluster Software for OpenVMS for Integrity cessing, mass storage (including system disks), and Servers other resources under a single OpenVMS security and management domain. Within this highly integrated en- • HP VMScluster Software for OpenVMS AlphaServers vironment, systems retain their independence because (through V8.3) they use local, memory-resident copies of the OpenVMS operating system. Thus, OpenVMS Cluster systems • HP VAXcluster Software for OpenVMS VAX (through can boot and shut down independently while benefiting V7.3) from common resources. • HP OpenVMS Cluster Client Software for Integrity Servers Applications running on one or more systems in an OpenVMS Cluster system can access shared resources • HP OpenVMS Cluster Client Software for Al- in a coordinated manner. OpenVMS Cluster soft- phaServers (part of NAS150) ware components synchronize access to shared re- sources, allowing multiple processes on any system in • HP OpenVMS Cluster Client Software for VAX the OpenVMS Cluster to perform coordinated, shared (through V7.3) (part of NAS150) data updates. Except where noted, the features described in this Because resources are shared, OpenVMS Cluster sys- SPD apply equally to Integrity server, AlphaServers and tems offer higher availability than standalone systems. -

1 DS-DWZZH-05 Ultrascsi Hub 1.1 General Overview

TruCluster Software Products Hardware Configuration Technical Update for DS-DWZZH-05 UltraSCSI Hub December 1998 Product Version: TruCluster Production Server Software Software Version 1.4A and TruCluster Production Server Software Version 1.5 and TruCluster Available Server Software 1.4A and TruCluster Available Server Software Version 1.5 Operating System and Version: Compaq’s DIGITAL UNIX Version 4.0B and Compaq’s DIGITAL UNIX Version 4.0D This technical update describes how to configure the DS-DWZZH-05 UltraSCSI hub in a TruCluster Software Products environment. Compaq Computer Corporation Houston, Texas © Compaq Computer Corporation 1998 All rights reserved. The following are trademarks of Compaq Computer Corporation: ALL–IN–1, Alpha AXP, AlphaGeneration, AlphaServer, AltaVista, ATMworks, AXP, Bookreader, CDA, DDIS, DEC, DEC Ada, DEC Fortran, DEC FUSE, DECnet, DECstation, DECsystem, DECterm, DECUS, DECwindows, DTIF, Massbus, MicroVAX, OpenVMS, POLYCENTER, PrintServer, Q–bus, StorageWorks, TruCluster, ULTRIX, ULTRIX Mail Connection, ULTRIX Worksystem Software, UNIBUS, VAX, VAXstation, VMS, XUI, and the Compaq logo. Prestoserve is a trademark of Legato Systems, Inc.; the trademark and software are licensed to Compaq Computer Corporation by Legato Systems, Inc. NFS is a registered trademark of Sun Microsystems, Inc. Open Software Foundation, OSF, OSF/1, OSF/Motif, and Motif are trademarks of the Open Software Foundation, Inc. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, -

Alpha and VAX Comparison Based on Industry-Standard Benchmark

Alpha and VAX Comparison based on Industry-standard Benchmark Results Digital Equipment Corporation December 1994 EC-N3909-10 Version 3.0 December 1994 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. Digital conducts its business in a manner that conserves the environment and protects the safety and health of its employees, customers, and the community. Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c) (1 )(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227 7013. Copyright© 1994 Digital Equipment Corporation All rights reserved. Printed in U.S.A. The following are trademarks of Digital Equipment Corporation: AlphaServer, AlphaStation, AlphaGeneration, DEC, OpenVMS, VMS, ULTRIX, and the DIGITAL logo. The following are third-party trademarks: MIPS is a trademark of MIPS Computer Systems, Inc. TPC-A is a trademark of the Transaction Processing Performance Council. INFORMIX is a registered trademark of lnformix Software, Inc. OSF/1 is a registered trademark of the Open Software Foundation, Inc. ORACLE is a registered trademark of Oracle Corporation. SPEC, SPECfp92, and SPECratio are trademarks of Standard Performance Evaluation Corporation. MIPS is a trademark of MIPS Computer Systems, Inc. All other trademarks and registered -

DIGITAL Alphaserver 400 Firmware Update Procedures

DIGITAL AlphaServer 400 Firmware Update Procedures Digital Equipment Corporation Maynard, Massachusetts First Printing, March 1996 Revised, May 1996 Revised, September 1996 Revised, December 1996 Revised, March 1997 Revised, October 1997 Revised, January 1998 Revised, June 1998 Revised, September 1998 Revised,March 1999 Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description. Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from DIGITAL or an authorized sublicensor. Copyright © Digital Equipment Corporation, 1996, 1997, 1998, 1999. All Rights Reserved. COMPAQ, the Compaq logo and the Digital logo Registered in U.S. Patent and Trademark Office. Alpha, AlphaServer, Bookreader, DEC, DECchip, DECpc, DECwindows, DEC VET, DIGITAL, InfoServer, OpenVMS, RRD43, RZ, TURBOchannel, ULTRIX, VAX, VAX DOCUMENT, and VMS are trademarks of Compaq Computer Corporation. PostScript is a registered trademark of Adobe Systems, Inc. Windows NT is a trademark of Microsoft, Inc. Motif is a registered trademark of the Open Software Foundation, Inc., licensed by Digital. UNIX is a registered trademark in the United States and other countries licensed exclusively through X/Open Company Ltd. All other trademarks and registered trademarks are the property of their respective holders. FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

DSSI Vmscluster Installation and Troubleshooting Guide

DSSI VMScluster Installation and Troubleshooting Guide Order Number: EK–410AB–MG. D01 Digital Equipment Corporation Maynard, Massachusetts First Printing, October 1994 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation makes no representation that the use of its products in the manner described in the publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description. Possession, use or copying of the sofware described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor. Copyright © Digital Equipment Corporation, 1994. All Rights reserved. The Reader’s Comments form at the end of this document requests your critical evaluation to assist in preparing future documentation. The following are trademarks of Digital Equipment Corporation: Alpha AXP, AXP, DEC, DECnet, Digital, MicroVAX, OpenVMS, VAX, VAX DOCUMENT, VAXcluster, VMScluster, the AXP logo, and the DIGITAL logo. OSF/1 is a registered trademark of Open Software Foundation, Inc. All other trademarks and registered trademarks are the property of their respective holders. FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. -

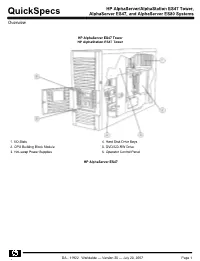

HP Alphaserver/Alphastation ES47 Tower, Alphaserver ES47, And

HP AlphaServer/AlphaStation ES47 Tower, QuickSpecs AlphaServer ES47, and AlphaServer ES80 Systems Overview HP AlphaServer ES47 Tower HP AlphaStation ES47 Tower 1. I/O Slots 4. Hard Disk Drive Bays 2. CPU Building Block Module 5. DVD/CD-RW Drive 3. Hot-swap Power Supplies 6. Operator Control Panel HP AlphaServer ES47 DA - 11922 Worldwide — Version 25 — July 23, 2007 Page 1 HP AlphaServer/AlphaStation ES47 Tower, QuickSpecs AlphaServer ES47, and AlphaServer ES80 Systems Overview 1. Cable/DSL HUB 2. StorageWorks Drawer (optional) 3. PCI/PCI-X I/O Expansion Drawer(s) (optional) 4. System Building Block Drawer (Model 2 includes 1 drawer; Model 4 includes 2 drawers) 5. AC input controller(s) (mandatory options) HP AlphaServer ES80 DA - 11922 Worldwide — Version 25 — July 23, 2007 Page 2 HP AlphaServer/AlphaStation ES47 Tower, QuickSpecs AlphaServer ES47, and AlphaServer ES80 Systems Overview 1. Cable/DSL HUB 2. StorageWorks Drawer (optional) 3. PCI/PCI-X I/O Expansion Drawer(s) (optional) 4. System Building Block Drawer (Model 2 includes 1 drawer; Model 3 includes 2 drawers; Model 6 includes 3 drawers; Model 8 includes 4 drawers) 5. AC input controller(s) (mandatory options) DA - 11922 Worldwide — Version 25 — July 23, 2007 Page 3 HP AlphaServer/AlphaStation ES47 Tower, QuickSpecs AlphaServer ES47, and AlphaServer ES80 Systems Overview At A Glance AlphaServer ES47/ES80 systems Up to 8 Alpha 21364 EV7 processors at 1150 MHz and 1000 MHz with advanced on-chip memory controllers and switch logic capable of providing 12.3 GB/s of memory bandwidth -

VAX VMS at 20

1977–1997... and beyond Nothing Stops It! Of all the winning attributes of the OpenVMS operating system, perhaps its key success factor is its evolutionary spirit. Some would say OpenVMS was revolutionary. But I would prefer to call it evolutionary because its transition has been peaceful and constructive. Over a 20-year period, OpenVMS has experienced evolution in five arenas. First, it evolved from a system running on some 20 printed circuit boards to a single chip. Second, it evolved from being proprietary to open. Third, it evolved from running on CISC-based VAX to RISC-based Alpha systems. Fourth, VMS evolved from being primarily a technical oper- ating system, to a commercial operat- ing system, to a high availability mission-critical commercial operating system. And fifth, VMS evolved from time-sharing to a workstation environment, to a client/server computing style environment. The hardware has experienced a similar evolution. Just as the 16-bit PDP systems laid the groundwork for the VAX platform, VAX laid the groundwork for Alpha—the industry’s leading 64-bit systems. While the platforms have grown and changed, the success continues. Today, OpenVMS is the most flexible and adaptable operating system on the planet. What start- ed out as the concept of ‘Starlet’ in 1975 is moving into ‘Galaxy’ for the 21st century. And like the universe, there is no end in sight. —Jesse Lipcon Vice President of UNIX and OpenVMS Systems Business Unit TABLE OF CONTENTS CHAPTER I Changing the Face of Computing 4 CHAPTER II Setting the Stage 6 CHAPTER -

Compaq Alphaserver DS Series Space-Saving Speed

CMPQ000034_AlphaServDS.qxd 5/30/01 4:03 PM Page 4 Compaq AlphaServer DS Series Space-saving speed “The AlphaServer DS10 is a neatly packaged, powerful server that we can Performance leadership accommodates stack in our racks. The performance is incredible and the price is right.” the astounding growth of Internet and Jan Isley Senior Engineer e-commerce-related applications EarthLink, Inc. Contact info for resellers Helpful urls Compaq provides industry-leading For more detailed information on support to our partners, at any time. these and other Compaq products Please use one of the numbers or and services, visit the following sites: websites below to contact us for more > www.compaq.com/alphaserver information on products, services or other questions you might have. And > www.compaq.com/support remember, the best online resource > www.compaq.com/services for our resellers and partners is the > www.compaq.com/solutions/ Compaq Partner Network, customsystems cpn.compaq.com The Compaq AlphaServer™ space is limited. These high- Compaq advantage Phone contacts: DS Series features new- density rack-mount systems > Includes Compaq > Compaq product information generation processors so ease the constraints of space, Management for 1-800-345-1518 customers receive the frequent system upgrades exceptional server and network management > Compaq reseller consulting competitive advantage of and maintenance, while capabilities from on-site 1-800-444-7575 Compaq Alpha™ 64-bit improving availability or remote locations performance for their most and reliability. Compaq > Flexible leasing and financing alternatives Websites: intensive applications. Newly AlphaServer systems continue enable businesses to designed space-saving to successfully power the adapt to changing > cpn.compaq.com pedestals, desktops and most demanding computing business conditions > www.compaq.com/resellers industry-standard racks offer environments, performing > Compaq CustomSystems integrates, packages and more power in a smaller mission-critical applications deploys ready-to-run footprint.