Introduction to Microprocessors DCAP210

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

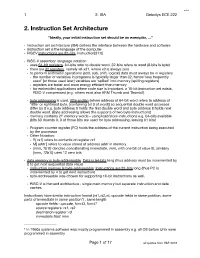

2. Instruction Set Architecture

!1 2. ISA Gebotys ECE 222 2. Instruction Set Architecture “Ideally, your initial instruction set should be an exemplar, …” " Instruction set architecture (ISA) defines the interface between the hardware and software# " instruction set is the language of the computer# " RISCV instructions are 32-bits, instruction[31:0]# " RISC-V assembly1 language notation # " uses 64-bit registers, 64-bits refer to double word, 32-bits refers to word (8-bits is byte).# " there are 32 registers, namely x0-x31, where x0 is always zero # " to perform arithmetic operations (add, sub, shift, logical) data must always be in registers # " the number of variables in programs is typically larger than 32, hence ‘less frequently used’ [or those used later] variables are ‘spilled’ into memory [spilling registers]# " registers are faster and more energy e$cient than memory# " for embedded applications where code size is important, a 16-bit instruction set exists, RISC-V compressed (e.g. others exist also ARM Thumb and Thumb2)# " byte addressing is used, little endian (where address of 64-bit word refers to address of ‘little' or rightmost byte, [containing bit 0 of word]) so sequential double word accesses di%er by 8 e.g. byte address 0 holds the first double word and byte address 8 holds next double word. (Byte addressing allows the supports of two byte instructions)# " memory contains 261 memory words - using load/store instructions e.g. 64-bits available (bits 63 downto 0, 3 of those bits are used for byte addressing, leaving 61 bits)# " Program counter register (PC) -

Over View of Microprocessor 8085 and Its Application

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) e-ISSN: 2278-2834,p- ISSN: 2278-8735.Volume 10, Issue 6, Ver. II (Nov - Dec .2015), PP 09-14 www.iosrjournals.org Over view of Microprocessor 8085 and its application Kimasha Borah Assistant Professor, Centre for Computer Studies Centre for Computer Studies, Dibrugarh University, Dibrugarh, Assam, India Abstract: Microprocessor is a program controlled semiconductor device (IC), which fetches, decode and executes instructions. It is versatile in application and is flexible to some extent. Nowadays, modern microprocessors can perform extremely sophisticated operations in areas such as meteorology, aviation, nuclear physics and engineering, and take up much less space as well as delivering superior performance Here is a brief review of microprocessor and its various application Key words: Semi Conductor, Integrated Circuits, CPU, NMOS ,PMOS, VLSI I. Introduction: Microprocessor is derived from two words micro and processor. Micro means small, tiny and processor means which processes something. It is a single Very Large Scale of Integration (VLSI) chip that incorporates all functions of central processing unit (CPU) fabricated on a single Integrated Circuits (ICs) (1).Some other units like caches, pipelining, floating point processing arithmetic and superscaling units are additionally present in the microprocessor and that results in increasing speed of operation.8085,8086,8088 are some examples of microprocessors(2). The technology used for microprocessor is N type metal oxide semiconductor(NMOS)(3). Basic operations of microprocessor are fetching instructions from memory ,decoding and executing them ie it takes data or operand from input device, perform arithmetic and logical operations and store results in required location or send result to output devices(1).Word size identifies the microprocessor.E.g. -

Exploiting Branch Target Injection Jann Horn, Google Project Zero

Exploiting Branch Target Injection Jann Horn, Google Project Zero 1 Outline ● Introduction ● Reverse-engineering branch prediction ● Leaking host memory from KVM 2 Disclaimer ● I haven't worked in CPU design ● I don't really understand how CPUs work ● Large parts of this talk are based on guesses ● This isn't necessarily how all CPUs work 3 Variants overview Spectre Meltdown ● CVE-2017-5753 ● CVE-2017-5715 ● CVE-2017-5754 ● Variant 1 ● Variant 2 ● Variant 3 ● Bounds Check ● Branch Target ● Rogue Data Cache Bypass Injection Load ● Primarily affects ● Primarily affects ● Affects kernels (and interpreters/JITs kernels/hypervisors architecturally equivalent software) 4 Performance ● Modern consumer CPU clock rates: ~4GHz ● Memory is slow: ~170 clock cycles latency on my machine ➢ CPU needs to work around high memory access latencies ● Adding parallelism is easier than making processing faster ➢ CPU needs to do things in parallel for performance ● Performance optimizations can lead to security issues! 5 Performance Optimization Resources ● everyone wants programs to run fast ➢ processor vendors want application authors to be able to write fast code ● architectural behavior requires architecture documentation; performance optimization requires microarchitecture documentation ➢ if you want information about microarchitecture, read performance optimization guides ● Intel: https://software.intel.com/en-us/articles/intel-sdm#optimization ("optimization reference manual") ● AMD: https://developer.amd.com/resources/developer-guides-manuals/ ("Software Optimization Guide") 6 (vaguely based on optimization manuals) Out-of-order execution front end out-of-order engine port (scheduler, renaming, ...) port instruction stream add rax, 9 add rax, 8 inc rbx port inc rbx sub rax, rbx mov [rcx], rax port cmp rax, 16 .. -

An 8085 Microprocessor Based Monitor System for a 750 Cc Honda Motorcycle

Rochester Institute of Technology RIT Scholar Works Theses 1988 An 8085 Microprocessor based monitor system for a 750 cc Honda motorcycle Robert H. Leet Follow this and additional works at: https://scholarworks.rit.edu/theses Recommended Citation Leet, Robert H., "An 8085 Microprocessor based monitor system for a 750 cc Honda motorcycle" (1988). Thesis. Rochester Institute of Technology. Accessed from This Thesis is brought to you for free and open access by RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact [email protected]. Rochester Institute of Technology School of Computer Science and Technology An 8085 Microprocessor Based Monitor System For A 750 cc Honda Motorcycle By Robert H. Leet A thesis, submitted to The Faculty of the School of Computer Science and Technology, in partial fulfillment of the requirements for the degree of Master of Science in Computer Science Approved by: Protapa Reddy Dr. Protapa Reddy Peter G. Andrews Dr. Peter Anderson Rayno N,eimi Dr. Rayno Niemi March 24, 1988 I Robert H. Leet prefer to be contacted each time a ~equest for reproduction is made. I can be reached at the following address: 15417 Preston Road #1152 Dallas, Texas 75248 Ma r c h 2 5, 1 9 8 8 Abstract This system replaces the analog speedometer and tachometer gauge cluster of a 750 cc Honda motorcycle with a computerized monitor system based on the INTEL 8085A microprocessor and family of peripherals. The system adds the enhanced functionality of engine temperature, battery charging, fuel level, turn signal, and kick stand monitoring and status display. -

Simty: Generalized SIMT Execution on RISC-V Caroline Collange

Simty: generalized SIMT execution on RISC-V Caroline Collange To cite this version: Caroline Collange. Simty: generalized SIMT execution on RISC-V. CARRV 2017: First Work- shop on Computer Architecture Research with RISC-V, Oct 2017, Boston, United States. pp.6, 10.1145/nnnnnnn.nnnnnnn. hal-01622208 HAL Id: hal-01622208 https://hal.inria.fr/hal-01622208 Submitted on 7 Oct 2020 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Simty: generalized SIMT execution on RISC-V Caroline Collange Inria [email protected] ABSTRACT and programming languages to target GPU-like SIMT cores. Be- We present Simty, a massively multi-threaded RISC-V processor side simplifying software layers, the unification of CPU and GPU core that acts as a proof of concept for dynamic inter-thread vector- instruction sets eases prototyping and debugging of parallel pro- ization at the micro-architecture level. Simty runs groups of scalar grams. We have implemented Simty in synthesizable VHDL and threads executing SPMD code in lockstep, and assembles SIMD synthesized it for an FPGA target. instructions dynamically across threads. Unlike existing SIMD or We present our approach to generalizing the SIMT model in SIMT processors like GPUs or vector processors, Simty vector- Section 2, then describe Simty’s microarchitecture is Section 3, and izes scalar general-purpose binaries. -

8085 Microprocessor Submitted in Partial Fulfillment of the Requirement for the Award of Degree of Electronics

www.studymafia.org A Seminar report On 8085 microprocessor Submitted in partial fulfillment of the requirement for the award of degree of Electronics SUBMITTED TO: SUBMITTED BY: www.studymafia.org www.studymafia.org www.studymafia.org Acknowledgement I would like to thank respected Mr…….. and Mr. ……..for giving me such a wonderful opportunity to expand my knowledge for my own branch and giving me guidelines to present a seminar report. It helped me a lot to realize of what we study for. Secondly, I would like to thank my parents who patiently helped me as i went through my work and helped to modify and eliminate some of the irrelevant or un-necessary stuffs. Thirdly, I would like to thank my friends who helped me to make my work more organized and well-stacked till the end. Next, I would thank Microsoft for developing such a wonderful tool like MS Word. It helped my work a lot to remain error-free. Last but clearly not the least, I would thank The Almighty for giving me strength to complete my report on time. www.studymafia.org Preface I have made this report file on the topic 8085 microprocessor; I have tried my best to elucidate all the relevant detail to the topic to be included in the report. While in the beginning I have tried to give a general view about this topic. My efforts and wholehearted co-corporation of each and everyone has ended on a successful note. I express my sincere gratitude to …………..who assisting me throughout the preparation of this topic. -

Datasheet-AMD-Am29202.Pdf

Advance Information Advanced Am29202 Micro Low-Cost RISC Microcontroller with Devices IEEE-1284-Compliant Parallel Interface DISTINCTIVE CHARACTERISTICS Completely integrated system for IEEE Std 1284-1994-compliant parallel port cost-sensitive embedded applications interface (peripheral-side only) supports fast requiring high performance bidirectional data transfers. Full 32-bit RISC architecture offers faster — Compatibility, Nibble, Byte, and ECP modes instruction execution and higher performance. — Supports Microsoft Windows Printing System — 32-bit instruction/data bus Bidirectional bit serializer/deserializer for direct — 22-bit address bus connection to raster input and output devices — 192 general-purpose registers 12-line programmable I/O port — Fully pipelined, three-address instruction (8 lines interruptible) architecture DRAM page-mode support improves memory — 104-Mbyte address space access time. — 12-, 16-, and 20-MHz operating frequencies On-chip DRAM mapping reduces memory — 16 VAX MIPS sustained at 20 MHz requirements. Glueless system interfaces with on-chip wait Advanced debugging support state control lower total system cost. — IEEE Std 1149.1-1990-compliant Standard — ROM controller supports four banks of ROM, Test Access Port and Boundary Scan Architec- each separately programmable for 8-, 16-, or ture (JTAG) for testing system hardware 32-bit-wide interface. — Instruction tracing — DRAM controller supports four banks of — UART serial port DRAM, each separately programmable for Software and hardware development tools -

Lecture-1 an Overview of Microprocessor the First

Lecture-1 An Overview of Microprocessor The first question that comes in one’s mind is "What is a microprocessor?”. Let us start with a more familiar term computer. A digital computer is an electronic machine capable of quickly performing a wide variety of tasks. They can be used to compile, correlate, sort, merge and store data as well as perform complex calculations at much faster rate than human being by means of stored instructions. A digital computer is different from a general purpose calculator in a sense that digital computer is capable of operating according to the instructions that are stored within the computer whereas a calculator must be given instructions on a step by step basis to perform calculations. By this definition a programmable calculator can be considered a computer. Historically, digital computers have been categorized according to the size using the words large, medium, minicomputer and microcomputer. In the early years of development, the emphasis was on large and more powerful computers. Large and medium sized computers were designed to solve complex scientific and engineering problems. In early stage of development these computers were accessible and affordable only to large corporations, big universities and government agencies. Later on, minicomputers were made available for use in office, small collage, medium size business organization, small factory etc. As the technology has advanced from SSI to VLSI & SLSI, the face of the computer has changed gradually and it became possible to build the entire central processing unit (CPU) on a single-chip known as microprocessor. A control processing unit (CPU) with its related timing functions on a single chip known as microprocessor. -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

Vysoké Učení Technické V Brně Návrh Řídicí Jednotky

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ BRNO UNIVERSITY OF TECHNOLOGY FAKULTA STROJNÍHO INŽENÝRSTVÍ ÚSTAV AUTOMATIZACE A INFORMATIKY FACULTY OF MECHANICAL ENGINEERING INSTITUTE OF AUTOMATION AND COMPUTER SCIENCE NÁVRH ŘÍDICÍ JEDNOTKY PRO AUTONOMNÍ MOBILNÍ ROBOT DESIGN OF CONTROL BOARD FOR AUTONOMOUS MOBILE ROBOT BAKALÁŘSKÁ PRÁCE BACHELOR'S THESIS AUTOR PRÁCE PETR MAŠEK AUTHOR VEDOUCÍ PRÁCE ING. STANISLAV VĚCHET, PH.D. SUPERVISOR BRNO 2010 Strana 3 Vysoké učení technické v Brně, Fakulta strojního inženýrství Ústav automatizace a informatiky Akademický rok: 2009/2010 ZADÁNÍ BAKALÁŘSKÉ PRÁCE student(ka): Petr Mašek který/která studuje v bakalářském studijním programu obor: Aplikovaná informatika a řízení (3902R001) Ředitel ústavu Vám v souladu se zákonem č.111/1998 o vysokých školách a se Studijním a zkušebním řádem VUT v Brně určuje následující téma bakalářské práce: Návrh řídicí jednotky pro autonomní mobilní robot v anglickém jazyce: Design of control board for autonomous mobile robot. Stručná charakteristika problematiky úkolu: Cílem práce je návrh a výroba základní řídicí jednotky autonomního mobilního robotu. Účelem této jednotky je zpracování informací z infračervených senzoru vzdálenosti a jejich vyhodnocení. Dále pak řízení aktuátorů. Řídicí jednotka musí být dostatečně výkonná pro zpracování základních navigačních tzv. “bug” algoritmů. Cíle bakalářské práce: Prostudujte možnosti řízení konstrukčně podobných robotů Navrhněte nejvhodnější strukturu řídicí jednotky Tuto řídicí jednotku vyrobte Výsledný produkt prakticky otestujte Strana 4 Seznam odborné literatury: www.robotika.cz www.megarobot.net www.hobbyrobot.cz Vedoucí bakalářské práce: Ing. Stanislav Věchet, Ph.D. Termín odevzdání bakalářské práce je stanoven časovým plánem akademického roku 2009/2010. V Brně, dne L.S. _______________________________ _______________________________ Ing. Jan Roupec, Ph.D. prof. RNDr. -

Ep 2182433 A1

(19) & (11) EP 2 182 433 A1 (12) EUROPEAN PATENT APPLICATION published in accordance with Art. 153(4) EPC (43) Date of publication: (51) Int Cl.: 05.05.2010 Bulletin 2010/18 G06F 9/38 (2006.01) (21) Application number: 07768016.3 (86) International application number: PCT/JP2007/063241 (22) Date of filing: 02.07.2007 (87) International publication number: WO 2009/004709 (08.01.2009 Gazette 2009/02) (84) Designated Contracting States: • AOKI, Takashi AT BE BG CH CY CZ DE DK EE ES FI FR GB GR Kawasaki-shi HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE Kanagawa 211-8588 (JP) SI SK TR Designated Extension States: (74) Representative: Ward, James Norman AL BA HR MK RS Haseltine Lake LLP Lincoln House, 5th Floor (71) Applicant: Fujitsu Limited 300 High Holborn Kawasaki-shi, Kanagawa 211-8588 (JP) London WC1V 7JH (GB) (72) Inventors: • TOYOSHIMA, Takashi Kawasaki-shi Kanagawa 211-8588 (JP) (54) INDIRECT BRANCHING PROGRAM, AND INDIRECT BRANCHING METHOD (57) A processor 100 reads an interpreter program the indirect branch instruction in a link register 120c (the 200a to start an interpreter. The interpreter makes branch processor 100 internally stacks the branch destination prediction by executing, in place of an indirect branch addresses also in a return address stack 130) in inverse instruction that is necessary for execution of a source order and reading the addresses from the return address program 200b, storing branch destination addresses in stack 130 in one at a time manner. EP 2 182 433 A1 Printed by Jouve, 75001 PARIS (FR) 1 EP 2 182 433 A1 2 Description vised and brought into practical use. -

Using and Porting the GNU Compiler Collection

Using and Porting the GNU Compiler Collection Richard M. Stallman Last updated 14 June 2001 for gcc-3.0 Copyright c 1988, 1989, 1992, 1993, 1994, 1995, 1996, 1998, 1999, 2000, 2001 Free Software Foundation, Inc. For GCC Version 3.0 Published by the Free Software Foundation 59 Temple Place - Suite 330 Boston, MA 02111-1307, USA Last printed April, 1998. Printed copies are available for $50 each. ISBN 1-882114-37-X Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation; with the Invariant Sections being “GNU General Public License”, the Front-Cover texts being (a) (see below), and with the Back-Cover Texts being (b) (see below). A copy of the license is included in the section entitled “GNU Free Documentation License”. (a) The FSF’s Front-Cover Text is: A GNU Manual (b) The FSF’s Back-Cover Text is: You have freedom to copy and modify this GNU Manual, like GNU software. Copies published by the Free Software Foundation raise funds for GNU development. Short Contents Introduction......................................... 1 1 Compile C, C++, Objective C, Fortran, Java ............... 3 2 Language Standards Supported by GCC .................. 5 3 GCC Command Options ............................. 7 4 Installing GNU CC ............................... 111 5 Extensions to the C Language Family .................. 121 6 Extensions to the C++ Language ...................... 165 7 GNU Objective-C runtime features .................... 175 8 gcov: a Test Coverage Program ...................... 181 9 Known Causes of Trouble with GCC ................... 187 10 Reporting Bugs.................................