Intel's Core Family – the TOCK Lines I Introduction and the Core 2 Line

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

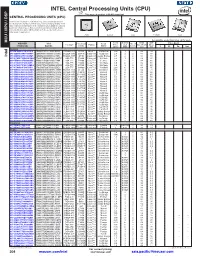

INTEL Central Processing Units (CPU) This Page of Product Is Rohs Compliant

INTEL Central Processing Units (CPU) This page of product is RoHS compliant. CENTRAL PROCESSING UNITS (CPU) Intel Processor families include the most powerful and flexible Central Processing Units (CPUs) available today. Utilizing industry leading 22nm device fabrication techniques, Intel continues to pack greater processing power into smaller spaces than ever before, providing desktop, mobile, and embedded products with maximum performance per watt across a wide range of applications. Atom Celeron Core Pentium Xeon For quantities greater than listed, call for quote. MCU \ MPU / DSP MPU / MCU \ MOUSER Intel Core Cache Data TDP Price Each Package Processor Family Code Freq. Size No. of Bus Width (Max) STOCK NO. Part No. Series Name (GHz) (MB) Cores (bit) (W) 1 25 50 100 Desktop 607-DF8064101211300Y DF8064101211300S R0VY FCBGA-559 D2550 Atom™ Cedarview 1.86 1 2 64 10 607-CM8063701444901S CM8063701444901S R10K FCLGA-1155 G1610 Celeron® Ivy Bridge 2.6 2 2 64 55 Intel 607-CM8062301046804S CM8062301046804S R05J FCLGA-1155 G540 Celeron® Sandy Bridge 2.5 2 2 64 65 607-AT80571RG0641MLS AT80571RG0641MLS LGTZ LGA-775 E3400 Celeron® Wolfdale 2.6 1 2 64 65 607-HH80557PG0332MS HH80557PG0332MS LA99 LGA-775 E4300 Core™ 2 Conroe 1.8 2 2 64 65 607-AT80570PJ0806MS AT80570PJ0806MS LB9J LGA-775 E8400 Core™ 2 Wolfdale 3.0 6 2 64 65 607-AT80571PH0723MLS AT80571PH0723MLS LGW3 LGA-775 E7400 Core™ 2 Wolfdale 2.8 3 2 64 65 607-AT80580PJ0676MS AT80580PJ0676MS LB6B LGA-775 Q9400 Core™ 2 Yorkfield 2.66 6 4 64 95 607-CM80616003060AES CM80616003060AES LBTD FCLGA-1156 -

Lambert-Mastersreport-2016

Copyright by Timothy Michael Lambert 2016 The Report Committee for Timothy Michael Lambert Certifies that this is the approved version of the following report: Enterprise Platform Systems Management Security Threats and Mitigation Techniques APPROVED BY SUPERVISING COMMITTEE: Supervisor: Suzanne Barber Elie Jreij Enterprise Platform Systems Management Security Threats and Mitigation Techniques by Timothy Michael Lambert, B.S.E.E., M.B.A. Report Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of Master of Science in Engineering The University of Texas at Austin December 2016 Dedication For Jake Lambert, whose life and passing spurned the author’s commitment to enter and dedication to complete this degree program. Acknowledgements I would like to express special thanks to my family and employer, Dell Technologies, Inc., for allowing me the time to pursue my educational and professional interests via this superb graduate program. Additionally, I would like to thank my supervisor, Dr. Suzanne Barber, and reader, Elie Jreij, who is a professional mentor in this research area. v Abstract Enterprise Platform Systems Management Security Threats and Mitigation Techniques Timothy Michael Lambert, MSE The University of Texas at Austin, 2016 Supervisor: Suzanne Barber Developers and technologists of enterprise systems such as servers, storage and networking products must constantly anticipate new cybersecurity threats and evolving security requirements. These requirements are typically sourced from marketing, customer expectations, manufacturing and evolving government standards. Much ongoing major research focus has been on securing the main enterprise system purpose functionality, operating system, network and storage. -

Multiprocessing Contents

Multiprocessing Contents 1 Multiprocessing 1 1.1 Pre-history .............................................. 1 1.2 Key topics ............................................... 1 1.2.1 Processor symmetry ...................................... 1 1.2.2 Instruction and data streams ................................. 1 1.2.3 Processor coupling ...................................... 2 1.2.4 Multiprocessor Communication Architecture ......................... 2 1.3 Flynn’s taxonomy ........................................... 2 1.3.1 SISD multiprocessing ..................................... 2 1.3.2 SIMD multiprocessing .................................... 2 1.3.3 MISD multiprocessing .................................... 3 1.3.4 MIMD multiprocessing .................................... 3 1.4 See also ................................................ 3 1.5 References ............................................... 3 2 Computer multitasking 5 2.1 Multiprogramming .......................................... 5 2.2 Cooperative multitasking ....................................... 6 2.3 Preemptive multitasking ....................................... 6 2.4 Real time ............................................... 7 2.5 Multithreading ............................................ 7 2.6 Memory protection .......................................... 7 2.7 Memory swapping .......................................... 7 2.8 Programming ............................................. 7 2.9 See also ................................................ 8 2.10 References ............................................. -

High-Performance Computing and Compiler Optimization

High-Performance Computing and Compiler Optimization P. (Saday) Sadayappan August 2019 What is a compiler? What •is Traditionally:a Compiler? Program that analyzes and translates from a high level language (e.g., C++) to low-level assembly languageCompilers that can be executed are translators by hardware • Fortran var a • C Machine code var b int a, b; Virtual machine code • C++ mov 3 a a = • 3;Java Transformed source code mov 4 r1 if (a• Text < processing4) { translate Augmented sourcecmpi a r1 b language= 2; • HTML/XML code jge l_e } else { • Command & Low-level commands mov 2 b b Scripting= 3; Semantic jmp l_d } Languages components • Natural language Anotherl_e: language mov 3 b • Domain specific l_d: ;done languages Wednesday,Wednesday, August 22, August 12 22, 12 Source: Milind Kulkarni 2 Compilers are optimizers • Can perform optimizations to make a program more What isefficient a Compiler? Compilers are optimizers var a • Can perform optimizations to make a program more efficient var b var a var c var b int a, b, c; mov a r1 var c b = av + 3; addi 3 r1 mov a r1 var a c = av + 3; mov varr1 bb addivar a3 r1 mov vara r2c movvar r1b b int a, b, c; addimov 3 ar2 r1 movvar r1c c b = a + 3; mov addir2 c3 r1 mov a Source:r1 Milind Kulkarni c = a + 3; mov r1 b addi 3 r1 ♦ Early days of computing: Minimizingmov a numberr2 of executedmov r1 b instructions Wednesday,minimized August 22, 12 program execution timeaddi 3 r2 mov r1 c § Sequential processors: had a singlemov functional r2 c unit to execute instructions § Compiler technology is very advanced in minimizing number of instructions ♦ Today:Wednesday, August 22, 12 § All computers are highly parallel: must make use of all parallel resources § Cost of data movement dominates the cost of performing the operations on data § Many challenging problems for compilers 3 The Good Old Days for Software Source: J. -

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

The Paramountcy of Reconfigurable Computing

Energy Efficient Distributed Computing Systems, Edited by Albert Y. Zomaya, Young Choon Lee. ISBN 978-0-471--90875-4 Copyright © 2012 Wiley, Inc. Chapter 18 The Paramountcy of Reconfigurable Computing Reiner Hartenstein Abstract. Computers are very important for all of us. But brute force disruptive architectural develop- ments in industry and threatening unaffordable operation cost by excessive power consumption are a mas- sive future survival problem for our existing cyber infrastructures, which we must not surrender. The pro- gress of performance in high performance computing (HPC) has stalled because of the „programming wall“ caused by lacking scalability of parallelism. This chapter shows that Reconfigurable Computing is the sil- ver bullet to obtain massively better energy efficiency as well as much better performance, also by the up- coming methodology of HPRC (high performance reconfigurable computing). We need a massive cam- paign for migration of software over to configware. Also because of the multicore parallelism dilemma, we anyway need to redefine programmer education. The impact is a fascinating challenge to reach new hori- zons of research in computer science. We need a new generation of talented innovative scientists and engi- neers to start the beginning second history of computing. This paper introduces a new world model. 18.1 Introduction In Reconfigurable Computing, e. g. by FPGA (Table 15), practically everything can be implemented which is running on traditional computing platforms. For instance, recently the historical Cray 1 supercomputer has been reproduced cycle-accurate binary-compatible using a single Xilinx Spartan-3E 1600 development board running at 33 MHz (the original Cray ran at 80 MHz) 0. -

5 Microprocessors

Color profile: Disabled Composite Default screen BaseTech / Mike Meyers’ CompTIA A+ Guide to Managing and Troubleshooting PCs / Mike Meyers / 380-8 / Chapter 5 5 Microprocessors “MEGAHERTZ: This is a really, really big hertz.” —DAVE BARRY In this chapter, you will learn or all practical purposes, the terms microprocessor and central processing how to Funit (CPU) mean the same thing: it’s that big chip inside your computer ■ Identify the core components of a that many people often describe as the brain of the system. You know that CPU CPU makers name their microprocessors in a fashion similar to the automobile ■ Describe the relationship of CPUs and memory industry: CPU names get a make and a model, such as Intel Core i7 or AMD ■ Explain the varieties of modern Phenom II X4. But what’s happening inside the CPU to make it able to do the CPUs amazing things asked of it every time you step up to the keyboard? ■ Install and upgrade CPUs 124 P:\010Comp\BaseTech\380-8\ch05.vp Friday, December 18, 2009 4:59:24 PM Color profile: Disabled Composite Default screen BaseTech / Mike Meyers’ CompTIA A+ Guide to Managing and Troubleshooting PCs / Mike Meyers / 380-8 / Chapter 5 Historical/Conceptual ■ CPU Core Components Although the computer might seem to act quite intelligently, comparing the CPU to a human brain hugely overstates its capabilities. A CPU functions more like a very powerful calculator than like a brain—but, oh, what a cal- culator! Today’s CPUs add, subtract, multiply, divide, and move billions of numbers per second. -

Creating a Pci Express Interconnect in the Gem5 Simulator

CREATING A PCI EXPRESS INTERCONNECT IN THE GEM5 SIMULATOR BY KRISHNA PARASURAM SRINIVASAN THESIS Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018 Urbana, Illinois Adviser: Associate Professor Nam Sung Kim ABSTRACT In this thesis, the objective was to implement a PCI (Peripheral Component Interconnect) Express interconnect in the gem5 architecture simulator. The interconnect was designed with the goal of aiding accurate modeling of PCI Express-based devices in gem5 in the future. The PCI Express interconnect that was created consisted of a root complex, PCI Express switch, as well as individual PCI Express links. Each of these created components can work independently, and can be easily integrated into the existing gem5 platforms for the ARM Instruction Set Architecture. The created PCI Express interconnect was evaluated against a real PCI Express interconnect present on an Intel Xeon server platform. The bandwidth offered by both interconnects was compared by reading data from storage devices using the Linux utility “dd”. The results indicate that the gem5 PCI Express interconnect can provide between 81% - 91.6% of the bandwidth of the real PCI Express interconnect. However, architectural differences between the gem5 and Intel Xeon platforms used, as well as unimplemented features of the PCI Express protocol in the gem5 PCI Express interconnect, necessitate more strenuous validation -

Double Play Intel’S Haswell-E & Skylake Lineups Offer Power for All

Double Play Intel’s Haswell-E & Skylake Lineups Offer Power For All ho is a power user? Sure, it’s really Intel Smart Cache is the most W easy to point to a $10,000 gaming you’ll find among PC—complete with a flagship processor, any of Intel’s desktop four graphics cards, PCIe SSDs, and all chips. The 5960X’s the requisite trimmings—and say, “that 3GHz stock clock guy,” but there’s a better answer. We think speed is expected for a that being a power user is more a state processor that boasts of mind than a state of hardware. True so many discrete cores, power users are those who make the most and it’s capable of of the hardware available to them. dialing in a 3.5GHz With a fleet of terrific, cutting-edge Turbo frequency for CPUs, Intel wants to make power users lightly threaded loads. out of everyone, regardless of budget. A pair of ruthless six- Thanks to a pair of processor families, core processors join the enthusiasts with a passion for pushing 5960X in formation. their CPUs have plenty of options. The Core i7-5930K and i7- 5820K are clocked at 3.5GHz Hail To The King and 3.3GHz, respectively, and The undisputed champ of desktop as you’ll soon find out, there’s performance continues its reign. The potential for much higher clocks. leader of the Haswell-E Dynasty, Both of these chips are equipped with 15MB you pair a Haswell-E CPU with a capable Intel’s Core i7-5960X is as good as it of Intel Smart Cache. -

The Intel X86 Microarchitectures Map Version 2.2

The Intel x86 Microarchitectures Map Version 2.2 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • New instructions: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

PCA-6009 Full-Sized PCA/ISA-Bus LGA775 Pentium® 4/Celeron® D

PCA-6009 Full-sized PC PCA-6009 Full-sized PCA/ISA-bus LGA775 with VGA/Gigabit Card Pentium® 4/Celeron® D Processor Card with VGA/Gigabit LAN/HISA (800 MHz FSB) Packing List Specifications Before you begin installing your card, please make Standard SBC Functions sure that the following materials have been shipped: • CPU: Intel LGA 775 Celeron D up to 3.06 GHz, Pentium 4 up to 3.4 GHz, FSB 533/800 MHz. • 1 PCA-6009 Pentium® 4/Celeron® D processor- • BIOS: Award 4 Mb Flash memory BIOS based single board computer • Chipset: Intel 915GV with ICH6 • 1 PCA-6009 Startup Manual • System Memory: Up to 2 GB; two 240-pin DIMM sock- ets. Supports dual channel DDRII 400/533 SDRAM. • 1 CD with driver utility and manual (in PDF format) • SATA/IDE Interface: Two on-board serial ATA connec- • 1 FDD cable p/n: 1700340640 tors with data transmission rate up to 150 MB/Sec and supporting Advanced Host controller interface (AHCI) • 1 Ultra ATA 66/100 HDD cables p/n: 1701400452 technology. One IDE hard disk drives or two enhanced LAN/HISA (800 MHz FSB) I/ISA-bus LGA775 Pentium • 2 Serial ATA HDD data cables p/n: 1700071000 IDE devices. Supports PIO mode 4 (16.67MB/s data transfer rate) and ATA 33/66/100 (33/66/100MB/s data • 2 Serial ATA HDD power cables p/n: 1703150102 transfer rate.) BIOS enabled/disabled. • 1 ATX 12V power converter p/n: 170304015K • FDD interface: Supports one FDD cable • Serial ports: Two serial RS-232 ports • 1 Printer (parallel) port & COM p/n: 1701260305 • Parallel port: One parallel port, supports SPP/EPP/ port cable kit ECP mode • -

Redalyc.Optimization of Operating Systems Towards Green Computing

International Journal of Combinatorial Optimization Problems and Informatics E-ISSN: 2007-1558 [email protected] International Journal of Combinatorial Optimization Problems and Informatics México Appasami, G; Suresh Joseph, K Optimization of Operating Systems towards Green Computing International Journal of Combinatorial Optimization Problems and Informatics, vol. 2, núm. 3, septiembre-diciembre, 2011, pp. 39-51 International Journal of Combinatorial Optimization Problems and Informatics Morelos, México Available in: http://www.redalyc.org/articulo.oa?id=265219635005 How to cite Complete issue Scientific Information System More information about this article Network of Scientific Journals from Latin America, the Caribbean, Spain and Portugal Journal's homepage in redalyc.org Non-profit academic project, developed under the open access initiative © International Journal of Combinatorial Optimization Problems and Informatics, Vol. 2, No. 3, Sep-Dec 2011, pp. 39-51, ISSN: 2007-1558. Optimization of Operating Systems towards Green Computing Appasami.G Assistant Professor, Department of CSE, Dr. Pauls Engineering College, Affiliated to Anna University – Chennai, Villupuram, Tamilnadu, India E-mail: [email protected] Suresh Joseph.K Assistant Professor, Department of computer science, Pondicherry University, Pondicherry, India E-mail: [email protected] Abstract. Green Computing is one of the emerging computing technology in the field of computer science engineering and technology to provide Green Information Technology (Green IT / GC). It is mainly used to protect environment, optimize energy consumption and keeps green environment. Green computing also refers to environmentally sustainable computing. In recent years, companies in the computer industry have come to realize that going green is in their best interest, both in terms of public relations and reduced costs.