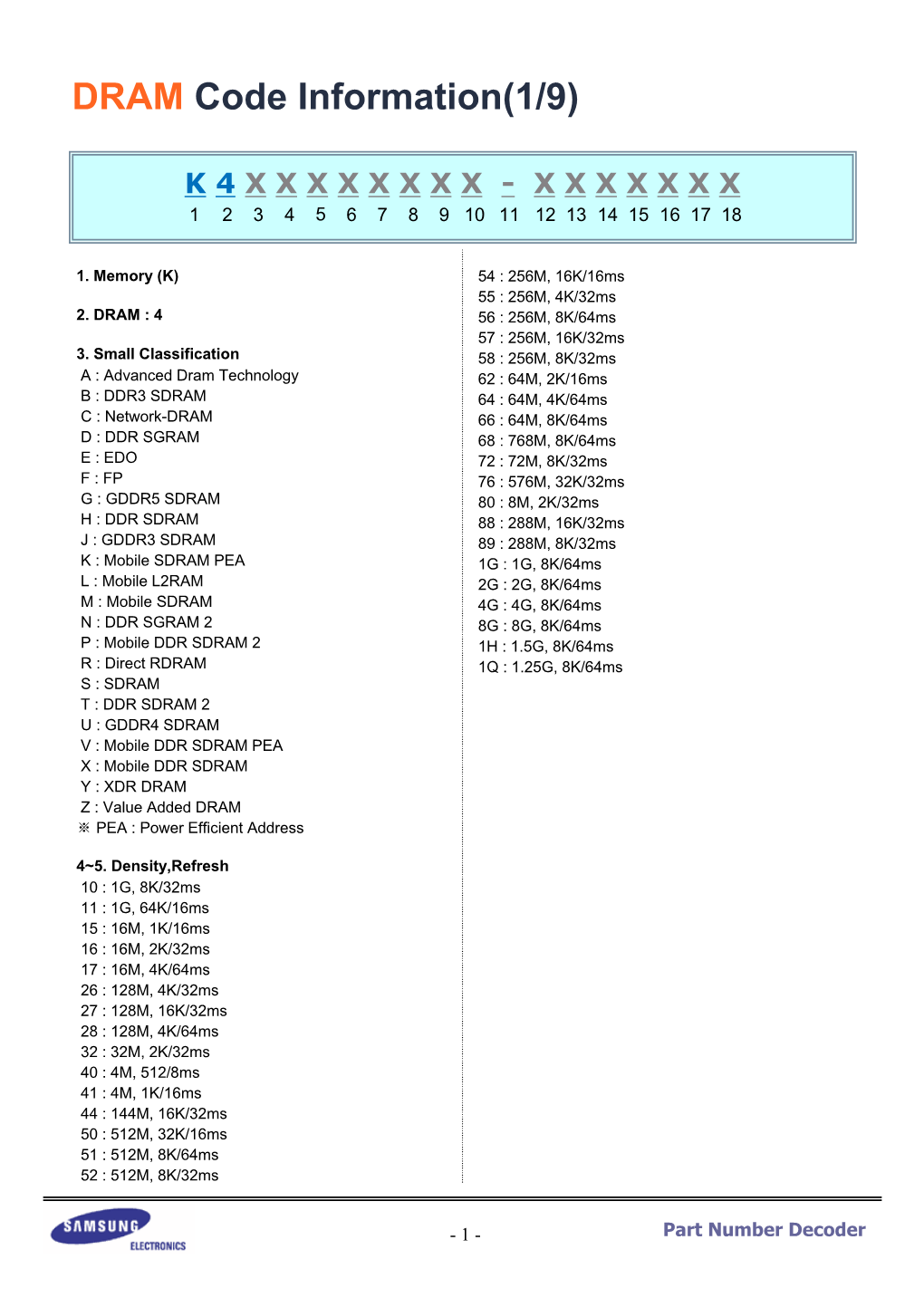

DRAM Code Information(1/9)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory & Devices

Memory & Devices Memory • Random Access Memory (vs. Serial Access Memory) • Different flavors at different levels – Physical Makeup (CMOS, DRAM) – Low Level Architectures (FPM,EDO,BEDO,SDRAM, DDR) • Cache uses SRAM: Static Random Access Memory – No refresh (6 transistors/bit vs. 1 transistor • Main Memory is DRAM: Dynamic Random Access Memory – Dynamic since needs to be refreshed periodically (1% time) – Addresses divided into 2 halves (Memory as a 2D matrix): • RAS or Row Access Strobe • CAS or Column Access Strobe Random-Access Memory (RAM) Key features – RAM is packaged as a chip. – Basic storage unit is a cell (one bit per cell). – Multiple RAM chips form a memory. Static RAM (SRAM) – Each cell stores bit with a six-transistor circuit. – Retains value indefinitely, as long as it is kept powered. – Relatively insensitive to disturbances such as electrical noise. – Faster and more expensive than DRAM. Dynamic RAM (DRAM) – Each cell stores bit with a capacitor and transistor. – Value must be refreshed every 10-100 ms. – Sensitive to disturbances. – Slower and cheaper than SRAM. Semiconductor Memory Types Static RAM • Bits stored in transistor “latches” à no capacitors! – no charge leak, no refresh needed • Pro: no refresh circuits, faster • Con: more complex construction, larger per bit more expensive transistors “switch” faster than capacitors charge ! • Cache Static RAM Structure 1 “NOT ” 1 0 six transistors per bit 1 0 (“flip flop”) 0 1 0/1 = example 0 Static RAM Operation • Transistor arrangement (flip flop) has 2 stable logic states • Write 1. signal bit line: High à 1 Low à 0 2. address line active à “switch” flip flop to stable state matching bit line • Read no need 1. -

Tesla K80 Gpu Accelerator

TESLA K80 GPU ACCELERATOR BD-07317-001_v05 | January 2015 Board Specification DOCUMENT CHANGE HISTORY BD-07317-001_v05 Version Date Authors Description of Change 01 June 23, 2014 GG, SM Preliminary Information (Information contained within this board specification is subject to change) 02 October 8, 2014 GG, SM • Updated product name • Minor change to Table 2 03 October 31, 2014 GG, SM • Added “8-Pin CPU Power Connector” section • Updated Figure 2 04 November 14, 2014 GG, SM • Removed preliminary and NDA • Updated boost clocks • Minor edits throughout document 05 January 30, 2015 GG, SM Updated Table 2 with MTBF data Tesla K80 GPU Accelerator BD-07317-001_v05 | ii TABLE OF CONTENTS Overview ............................................................................................. 1 Key Features ...................................................................................... 2 NVIDIA GPU Boost on Tesla K80 ................................................................ 3 Environmental Conditions ....................................................................... 4 Configuration ..................................................................................... 5 Mechanical Specifications ........................................................................ 6 PCI Express System ............................................................................... 6 Tesla K80 Bracket ................................................................................ 7 8-Pin CPU Power Connector ................................................................... -

1Gb Gddr3 SDRAM E-Die

K4W1G1646E 1Gb gDDR3 SDRAM 1Gb gDDR3 SDRAM E-die 96 FBGA with Lead-Free & Halogen-Free (RoHS Compliant) INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE. NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHER- WISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOL- OGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND. 1. For updates or additional information about Samsung products, contact your nearest Samsung office. 2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply. * Samsung Electronics reserves the right to change products or specification without notice. 1 of 123 Rev. 1.2 July 2009 K4W1G1646E 1Gb gDDR3 SDRAM Revision History Revision Month Year History 0.0 July 2008 - First release - Correction ball configuration on page 4. 0.9 October 2008 - Changed ordering Infomation 0.9 November 2008 - Correction package size on page 5. - Added thermal characteristics table 0.91 December 2008 - Added speed bin 1066Mbps - Corrected tFAW value on page 44 0.92 February 2009 - Corrected Package Dimension on page - Corrected Package pinout on page 4 - Added thermal characteristics values (speed bin 1066/1333/1600Mbps ) on page 14. 1.0 February 2009 - Added IDD SPEC values (speed bin 1066/1333/1600Mbps) on page 36. -

NVIDIA Quadro CX Overview

QuickSpecs NVIDIA Quadro CX Overview Models NVIDIA Quadro CX – The Accelerator for Creative Suite 4 Introduction The NVIDIA® Quadro® CX is the accelerator for Adobe® Creative Suite® 4-giving creative professionals the performance, tools, and reliability they need to maximize their creativity. Quadro CX enables H.264 video encoding at lightning-fast speeds with NVIDIA CUDA™ technology and accelerates rendering time for advanced effects. A Faster Way to Work Faster video encoding: Encode H.264 video at lightning-fast speeds with the NVIDIA CUDA™-enabled plug-in for Adobe Premiere® Pro CS4. Accelerated effects: Accelerate rendering time for advanced effects such as transformations, color correction, depth of field blur, turbulent noise, and more. A Better Way to Work High-quality preview: Accurately see what your deliverable will look like with 30-bit color or uncompressed 10-bit/12-bit SDI before final output.* Natural canvas: Experience fluid interaction with the Adobe Photoshop® canvas for smoother zooming and image rotation. Advanced multi-display management tools: Easily work across multiple displays with NVIDIA nView® advanced management tools for a smoother production pipeline. A More Reliable Way to Work Designed for CS4: NVIDIA Quadro CX is designed and optimized for Creative Suite 4. Built by NVIDIA: Quadro CX is engineered and optimized by NVIDIA to ensure your system works when you need it. Extended product lifecycle: Extended (24-36 month) product life cycle and availability for a stable platform environment. NOTE: As of August 1, 2009 Quadro CX is being replaced with Elemental Accelerator Software for NVIDIA Quadro. The same functionality is offered with drop in the box software, across multiple NVIDIA Quadro graphics cards. -

GRA110 3U VPX High Performance Graphics Board

GE Fanuc Embedded Systems GRA110 3U VPX High Performance Graphics Board Features The GRA110 is the first graphics board to be With a rich set of I/O, the GRA110 is designed • NVIDIA G73 GPU announced in the 3U VPX form factor. Bringing to serve many of the most common video - As used on NVIDIA® GeForce® 7600GT desktop performance to the rugged market, applications. Dual, independent channels the GRA110 represents a step change in mean that it is capable of driving RGB analog • Leading OpenGL performance capability for the embedded systems integrator. component video, digital DVI 1.0, and RS170, • 256 MBytes DDR SDRAM With outstanding functionality, together with NTSC or PAL standards. In addition, the GRA110’s • Two independent output channels PCI ExpressTM interconnect, even the most video input capability allows integration of sensor demanding applications can now be deployed data using RS170, NTSC or PAL video formats. • VESA output resolutions to 1600x1200 with incredible fidelity. • RS-170, NTSC & PAL video output • DVI 1.0 digital video output The VPX form factor allows for high speed PCI Express connections to single board computers in • RS170, NTSC & PAL Video output the system. The GRA110 supports the 16-lane PCI • Air- and rugged conduction- variants Express implementation, providing the maximum • 3U VPX Form Factors available communication bandwidth to a CPU such as GE Fanuc Embedded System’s SBC340. The PCI Express link will automatically adapt to the active number of lanes available, and so will work with single board computers -

DDR and DDR2 SDRAM Controller Compiler User Guide

DDR and DDR2 SDRAM Controller Compiler User Guide 101 Innovation Drive Software Version: 9.0 San Jose, CA 95134 Document Date: March 2009 www.altera.com Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending ap- plications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. UG-DDRSDRAM-10.0 Contents Chapter 1. About This Compiler Release Information . 1–1 Device Family Support . 1–1 Features . 1–2 General Description . 1–2 Performance and Resource Utilization . 1–4 Installation and Licensing . 1–5 OpenCore Plus Evaluation . 1–6 Chapter 2. Getting Started Design Flow . 2–1 SOPC Builder Design Flow . 2–1 DDR & DDR2 SDRAM Controller Walkthrough . -

AXP Internal 2-Apr-20 1

2-Apr-20 AXP Internal 1 2-Apr-20 AXP Internal 2 2-Apr-20 AXP Internal 3 2-Apr-20 AXP Internal 4 2-Apr-20 AXP Internal 5 2-Apr-20 AXP Internal 6 Class 6 Subject: Computer Science Title of the Book: IT Planet Petabyte Chapter 2: Computer Memory GENERAL INSTRUCTIONS: • Exercises to be written in the book. • Assignment questions to be done in ruled sheets. • You Tube link is for the explanation of Primary and Secondary Memory. YouTube Link: ➢ https://youtu.be/aOgvgHiazQA INTRODUCTION: ➢ Computer can store a large amount of data safely in their memory for future use. ➢ A computer’s memory is measured either in Bits or Bytes. ➢ The memory of a computer is divided into two categories: Primary Memory, Secondary Memory. ➢ There are two types of Primary Memory: ROM and RAM. ➢ Cache Memory is used to store program and instructions that are frequently used. EXPLANATION: Computer Memory: Memory plays a very important role in a computer. It is the basic unit where data and instructions are stored temporarily. Memory usually consists of one or more chips on the mother board, or you can say it consists of electronic components that store instructions waiting to be executed by the processor, data needed by those instructions, and the results of processing the data. Memory Units: Computer memory is measured in bits and bytes. A bit is the smallest unit of information that a computer can process and store. A group of 4 bits is known as nibble, and a group of 8 bits is called byte. -

AMD Radeon E8860

Components for AMD’s Embedded Radeon™ E8860 GPU INTRODUCTION The E8860 Embedded Radeon GPU available from CoreAVI is comprised of temperature screened GPUs, safety certi- fiable OpenGL®-based drivers, and safety certifiable GPU tools which have been pre-integrated and validated together to significantly de-risk the challenges typically faced when integrating hardware and software components. The plat- form is an off-the-shelf foundation upon which safety certifiable applications can be built with confidence. Figure 1: CoreAVI Support for E8860 GPU EXTENDED TEMPERATURE RANGE CoreAVI provides extended temperature versions of the E8860 GPU to facilitate its use in rugged embedded applications. CoreAVI functionally tests the E8860 over -40C Tj to +105 Tj, increasing the manufacturing yield for hardware suppliers while reducing supply delays to end customers. coreavi.com [email protected] Revision - 13Nov2020 1 E8860 GPU LONG TERM SUPPLY AND SUPPORT CoreAVI has provided consistent and dedicated support for the supply and use of the AMD embedded GPUs within the rugged Mil/Aero/Avionics market segment for over a decade. With the E8860, CoreAVI will continue that focused support to ensure that the software, hardware and long-life support are provided to meet the needs of customers’ system life cy- cles. CoreAVI has extensive environmentally controlled storage facilities which are used to store the GPUs supplied to the Mil/ Aero/Avionics marketplace, ensuring that a ready supply is available for the duration of any program. CoreAVI also provides the post Last Time Buy storage of GPUs and is often able to provide additional quantities of com- ponents when COTS hardware partners receive increased volume for existing products / systems requiring additional inventory. -

Solving High-Speed Memory Interface Challenges with Low-Cost Fpgas

SOLVING HIGH-SPEED MEMORY INTERFACE CHALLENGES WITH LOW-COST FPGAS A Lattice Semiconductor White Paper May 2005 Lattice Semiconductor 5555 Northeast Moore Ct. Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 www.latticesemi.com Introduction Memory devices are ubiquitous in today’s communications systems. As system bandwidths continue to increase into the multi-gigabit range, memory technologies have been optimized for higher density and performance. In turn, memory interfaces for these new technologies pose stiff challenges for designers. Traditionally, memory controllers were embedded in processors or as ASIC macrocells in SoCs. With shorter time-to-market requirements, designers are turning to programmable logic devices such as FPGAs to manage memory interfaces. Until recently, only a few FPGAs supported the building blocks to interface reliably to high-speed, next generation devices, and typically these FPGAs were high-end, expensive devices. However, a new generation of low-cost FPGAs has emerged, providing the building blocks, high-speed FPGA fabric, clock management resources and the I/O structures needed to implement next generation DDR2, QDR2 and RLDRAM memory controllers. Memory Applications Memory devices are an integral part of a variety of systems. However, different applications have different memory requirements. For networking infrastructure applications, the memory devices required are typically high-density, high-performance, high-bandwidth memory devices with a high degree of reliability. In wireless applications, low-power memory is important, especially for handset and mobile devices, while high-performance is important for base-station applications. Broadband access applications typically require memory devices in which there is a fine balance between cost and performance. -

NVIDIA Quadro FX 560 Graphics Controller Overview

QuickSpecs NVIDIA Quadro FX 560 Graphics Controller Overview Models NVIDIA Quadro FX 560 PCI-Express graphics controller kit. ES354AA Includes: PCA with ATX bracket, DVI to VGA converters, HDTV dongle, CD and manual. Introduction NVIDIA Quadro FX 560 features uncompromised performance and programmability at an entry-level price for professional CAD, DCC, and visualization applications. NVIDIA Quadro FX 560 entrylevel graphics are designed to deliver cost-effective solutions to professional 3D environments without compromising on quality, precision, performance, and programmability. Featuring advanced features ranging from a 128-bit floating point graphics pipeline, 12-bit subpixel precision, fast GDDR3 memory, and HD output, the NVIDIA Quadro FX 560 is certified on a wide set of CAD, DCC, and visualization applications, offering the value and capabilities professional users expect. In addition, support for one dual-link DVI output and HD component out enables direct connection to both high resolution digital flat panels and broadcast monitors, making the NVIDIA Quadro FX 560 a must have for any video editing solution. Performance & Features Features include an array of parallel vertex engines, fully programmable pixel pipelines, a high-speed graphics memory bus, and next-generation crossbar memory architecture: 128MB G-DDR3 graphics memory Two DVI-I (one dual-link) + 9-pin HDTV Out (HD output cable included) OpenGL quad-buffered stereo Rotated-Grid FSAA High Precision Dynamic Range Technology Unlimited Vertex & Pixel programmability 128-bit IEEE floating-point precision graphics pipeline\ 32-bit floating point color precision per component Hardware overlays Hardware accelerated anti-aliased points and lines Two-sided lighting Occlusion culling Advanced full-scene anti-aliasing Optimized and certified for OpenGL 2.0 and DirectX® 9.0 applications Multi-display productivity PCIe x16 bus Compatibility The NVIDIA Quadro FX 560 is supported on HP xw6400, xw8400 Workstations. -

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441 Contract Institution: Georgia Institute of Technology Project Director: D. Scott Wills Project Report 12 September 2002 — 11 September 2004 This project explored the impact of developing memory technologies on future supercomputers. This activity included both a literature study (see attached whitepaper), plus a more practical exploration of potential memory interfacing techniques using the sponsor recommended HyperTransport interface. The report indicates trends that will affect interconnection network design in future supercomputers. Related publications during the contract period include: 1. P. G. Sassone and D. S. Wills, On the Scaling of the Atlas Chip-Scale Multiprocessor, to appear in IEEE Transaction on Computers. 2. P. G. Sassone and D. S. Wills, Dynamic Strands: Collapsing Speculative Dependence Chains for Reducing Pipeline Communication, to appear in IEEE/ACM International Symposium on Microarchitecture, Portland, OR, December 2004. 3. B. A. Small, A. Shacham, K. Bergman, K. Athikulwongse, C. Hawkins, and D. S. Wills, Emulation of Realistic Network Traffic Patterns on an Eight-Node Data Vortex Interconnection Network Subsystem, to appear in OSA Journal of Optical Networking. 4. P. G. Sassone and D. S. Wills, On the Extraction and Analysis of Prevalent Dataflow Patterns, to appear in The IEEE 7th Annual Workshop on Workload Characterization (WWC-7), 8 pages, Austin, TX, October 2004. 5. H. Kim, D. S. Wills, and L. M. Wills, Empirical Analysis of Operand Usage and Transport in Multimedia Applications, in Proceedings of the 4th IEEE International Workshop on System-on-Chip for Real-Time Applications(IWSOC'04), pages 168-171, Banff, Alberta, Canada, July 2004. -

HP Grafične Postaje: HP Z1, HP Z2, HP Z4, ……

ARES RAČUNALNIŠTVO d.o.o. HP Z1 Tržaška cesta 330 HP Z2 1000 Ljubljana, Slovenia, EU HP Z4 tel: 01-256 21 50 Grafične kartice GSM: 041-662 508 e-mail: [email protected] www.ares-rac.si 29.09.2021 DDV = 22% 1,22 Grafične postaje HP Grafične postaje: HP Z1, HP Z2, HP Z4, …….. ZALOGA Nudimo vam tudi druge modele, ki še niso v ceniku preveri zalogo Na koncu cenika so tudi opcije: Grafične kartice. Ostale opcije po ponudbi. Objavljamo neto ceno in ceno z DDV (PPC in akcijsko). Dokončna cena in dobavni rok - po konkretni ponudbi Objavljamo neto ceno in ceno z DDV (PPC in akcijsko). Dokončna cena po ponudbi. Koda HP Z1 TWR Grafična postaja /Delovna postaja Zaloga Neto cena Cena z DDV (EUR) (EUR) HP Z1 G8 TWR Zaloga Neto cena Cena z DDV 29Y17AV HP Z1 G8 TWR, Core i5-11500, 16GB, SSD 512GB, nVidia GeForce RTX 3070 8GB, USB-C, Win10Pro #71595950 Koda: 29Y17AV#71595950 HP delovna postaja, HP grafična postaja, Procesor Intel Core i5 -11500 (2,7 - 4,6 GHz) 12MB 6 jedr/12 niti Nabor vezja Intel Q570 Pomnilnik 16 GB DDR4 3200 MHz (1x16GB), 3x prosta reža, do 128 GB 1.735,18 2.116,92 SSD pogon 512 GB M.2 2280 PCIe NVMe TLC Optična enota: brez, HDD pogon : brez Razširitvena mesta 2x 3,5'', 1x 2,5'', RAID podpira RAID AKCIJA 1.657,00 2.021,54 Grafična kartica: nVidia GeForce RTX 3070 8GB GDDR6, 256bit, 5888 Cuda jeder CENA Žične povezave: Intel I219-LM Gigabit Network Brezžične povezave: brez Razširitve: 1x M.2 2230; 1x PCIe 3.0 x16; 2x PCIe 3,0 x16 (ožičena kot x4); 2x M.2 2230/2280; 2x PCIe 3.0 x1 Čitalec kartic: brez Priključki spredaj: 1x USB-C, 2x