Condition Code Register Bits N, Z, V, C

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Research Brief March 2017 Publication #2017-16

Research Brief March 2017 Publication #2017-16 Flourishing From the Start: What Is It and How Can It Be Measured? Kristin Anderson Moore, PhD, Child Trends Christina D. Bethell, PhD, The Child and Adolescent Health Measurement Introduction Initiative, Johns Hopkins Bloomberg School of Every parent wants their child to flourish, and every community wants its Public Health children to thrive. It is not sufficient for children to avoid negative outcomes. Rather, from their earliest years, we should foster positive outcomes for David Murphey, PhD, children. Substantial evidence indicates that early investments to foster positive child development can reap large and lasting gains.1 But in order to Child Trends implement and sustain policies and programs that help children flourish, we need to accurately define, measure, and then monitor, “flourishing.”a Miranda Carver Martin, BA, Child Trends By comparing the available child development research literature with the data currently being collected by health researchers and other practitioners, Martha Beltz, BA, we have identified important gaps in our definition of flourishing.2 In formerly of Child Trends particular, the field lacks a set of brief, robust, and culturally sensitive measures of “thriving” constructs critical for young children.3 This is also true for measures of the promotive and protective factors that contribute to thriving. Even when measures do exist, there are serious concerns regarding their validity and utility. We instead recommend these high-priority measures of flourishing -

The Origin of the Peculiarities of the Vietnamese Alphabet André-Georges Haudricourt

The origin of the peculiarities of the Vietnamese alphabet André-Georges Haudricourt To cite this version: André-Georges Haudricourt. The origin of the peculiarities of the Vietnamese alphabet. Mon-Khmer Studies, 2010, 39, pp.89-104. halshs-00918824v2 HAL Id: halshs-00918824 https://halshs.archives-ouvertes.fr/halshs-00918824v2 Submitted on 17 Dec 2013 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Published in Mon-Khmer Studies 39. 89–104 (2010). The origin of the peculiarities of the Vietnamese alphabet by André-Georges Haudricourt Translated by Alexis Michaud, LACITO-CNRS, France Originally published as: L’origine des particularités de l’alphabet vietnamien, Dân Việt Nam 3:61-68, 1949. Translator’s foreword André-Georges Haudricourt’s contribution to Southeast Asian studies is internationally acknowledged, witness the Haudricourt Festschrift (Suriya, Thomas and Suwilai 1985). However, many of Haudricourt’s works are not yet available to the English-reading public. A volume of the most important papers by André-Georges Haudricourt, translated by an international team of specialists, is currently in preparation. Its aim is to share with the English- speaking academic community Haudricourt’s seminal publications, many of which address issues in Southeast Asian languages, linguistics and social anthropology. -

1 Curl and Divergence

Sections 15.5-15.8: Divergence, Curl, Surface Integrals, Stokes' and Divergence Theorems Reeve Garrett 1 Curl and Divergence Definition 1.1 Let F = hf; g; hi be a differentiable vector field defined on a region D of R3. Then, the divergence of F on D is @ @ @ div F := r · F = ; ; · hf; g; hi = f + g + h ; @x @y @z x y z @ @ @ where r = h @x ; @y ; @z i is the del operator. If div F = 0, we say that F is source free. Note that these definitions (divergence and source free) completely agrees with their 2D analogues in 15.4. Theorem 1.2 Suppose that F is a radial vector field, i.e. if r = hx; y; zi, then for some real number p, r hx;y;zi 3−p F = jrjp = (x2+y2+z2)p=2 , then div F = jrjp . Theorem 1.3 Let F = hf; g; hi be a differentiable vector field defined on a region D of R3. Then, the curl of F on D is curl F := r × F = hhy − gz; fz − hx; gx − fyi: If curl F = 0, then we say F is irrotational. Note that gx − fy is the 2D curl as defined in section 15.4. Therefore, if we fix a point (a; b; c), [gx − fy](a; b; c), measures the rotation of F at the point (a; b; c) in the plane z = c. Similarly, [hy − gz](a; b; c) measures the rotation of F in the plane x = a at (a; b; c), and [fz − hx](a; b; c) measures the rotation of F in the plane y = b at the point (a; b; c). -

FC = Mac V2 R V = 2Πr T F = T 1

Circular Motion Gravitron Cars Car Turning (has a curse) Rope Skip There must be a net inward force: Centripetal Force v2 F = maC a = C C R Centripetal acceleration 2πR v v v = R v T v 1 f = T The motorcycle rider does 13 laps in 150 s. What is his period? Frequency? R = 30 m [11.5 s, 0.087 Hz] What is his velocity? [16.3 m/s] What is his aC? [8.9 m/s2] If the mass is 180 kg, what is his FC? [1600 N] The child rotates 5 times every 22 seconds... What is the period? 60 kg [4.4 s] What is the velocity? [2.86 m/s] What is the acceleration? Which way does it point? [4.1 m/s2] What must be the force on the child? [245 N] Revolutions Per Minute (n)2πR v = 60 s An Ipod's hard drive rotates at 4200 RPM. Its radius is 0.03 m. What is the velocity in m/s of its edge? 1 Airplane Turning v = 232 m/s (520 mph) aC = 7 g's What is the turn radius? [785 m = 2757 ft] 2 FC Solving Circular Motion Problems 1. Determine FC (FBD) 2 2. Set FC = m v R 3. Solve for unknowns The book's mass is 2 kg it is spun so that the tension is 45 N. What is the velocity of the book in m/s? In RPM? R = 0.75 m [4.11 m/s] [52 RPM] What is the period (T) of the book? [1.15 s] The car is traveling at 25 m/s and the turn's radius is 63 m. -

TPS. 21 and 22 N., R. 11 E. by CLARENCE S. ROSS. INTRODUCTION. the Area Included in Tps. 21 and 22 N., R. 11 E., Lies in The

TPS. 21 AND 22 N., R. 11 E. By CLARENCE S. ROSS. INTRODUCTION. The area included in Tps. 21 and 22 N., R. 11 E., lies in the south eastern part of the Osage Reservation and in the eastern part of the Hominy quadrangle. (See fig. 1.) It may be reached from Skia took and Sperry, on the Midland Valley Railroad, about 4 miles to the east. Two major roads run west from these towns, following the valleys of Hominy and Delaware creeks, but the minor roads are very poor, and much of the area is difficult of access. The entire area is hilly and has a maximum relief of 400 feet. Most of the ridges are timbered, and farming is confined to the alluvial bottoms of the larger creeks. The areal geology of the Hominy quadrangle has been mapped on a scale of 2 miles to the inch in cooperation with the Oklahoma Geological Survey. The detailed structural examination of Tps. 21 and 22 N., R. 11 E., was made in March, April, May, and June, 1918, by the writer, Sidney Powers, W. S. W. Kew, and P. V. Roundy. All the mapping was done with plane table and telescope alidade. STRATIGRAPHY. EXPOSED ROCKS. The rocks exposed at the surface in this area belong to the middle Pennsylvanian, and consist of sandstone, shale, and limestone, ag gregating about 700 feet in thickness. Shale predominates, but sand stone and limestone form the prominent rock exposures. A few of the strata that may be used as key beds will be described for the benefit of those who may wish to do geologic work in the region. -

ISO Basic Latin Alphabet

ISO basic Latin alphabet The ISO basic Latin alphabet is a Latin-script alphabet and consists of two sets of 26 letters, codified in[1] various national and international standards and used widely in international communication. The two sets contain the following 26 letters each:[1][2] ISO basic Latin alphabet Uppercase Latin A B C D E F G H I J K L M N O P Q R S T U V W X Y Z alphabet Lowercase Latin a b c d e f g h i j k l m n o p q r s t u v w x y z alphabet Contents History Terminology Name for Unicode block that contains all letters Names for the two subsets Names for the letters Timeline for encoding standards Timeline for widely used computer codes supporting the alphabet Representation Usage Alphabets containing the same set of letters Column numbering See also References History By the 1960s it became apparent to thecomputer and telecommunications industries in the First World that a non-proprietary method of encoding characters was needed. The International Organization for Standardization (ISO) encapsulated the Latin script in their (ISO/IEC 646) 7-bit character-encoding standard. To achieve widespread acceptance, this encapsulation was based on popular usage. The standard was based on the already published American Standard Code for Information Interchange, better known as ASCII, which included in the character set the 26 × 2 letters of the English alphabet. Later standards issued by the ISO, for example ISO/IEC 8859 (8-bit character encoding) and ISO/IEC 10646 (Unicode Latin), have continued to define the 26 × 2 letters of the English alphabet as the basic Latin script with extensions to handle other letters in other languages.[1] Terminology Name for Unicode block that contains all letters The Unicode block that contains the alphabet is called "C0 Controls and Basic Latin". -

![B1. the Generating Functional Z[J]](https://docslib.b-cdn.net/cover/0425/b1-the-generating-functional-z-j-230425.webp)

B1. the Generating Functional Z[J]

B1. The generating functional Z[J] The generating functional Z[J] is a key object in quantum field theory - as we shall see it reduces in ordinary quantum mechanics to a limiting form of the 1-particle propagator G(x; x0jJ) when the particle is under thje influence of an external field J(t). However, before beginning, it is useful to look at another closely related object, viz., the generating functional Z¯(J) in ordinary probability theory. Recall that for a simple random variable φ, we can assign a probability distribution P (φ), so that the expectation value of any variable A(φ) that depends on φ is given by Z hAi = dφP (φ)A(φ); (1) where we have assumed the normalization condition Z dφP (φ) = 1: (2) Now let us consider the generating functional Z¯(J) defined by Z Z¯(J) = dφP (φ)eφ: (3) From this definition, it immediately follows that the "n-th moment" of the probability dis- tribution P (φ) is Z @nZ¯(J) g = hφni = dφP (φ)φn = j ; (4) n @J n J=0 and that we can expand Z¯(J) as 1 X J n Z Z¯(J) = dφP (φ)φn n! n=0 1 = g J n; (5) n! n ¯ so that Z(J) acts as a "generator" for the infinite sequence of moments gn of the probability distribution P (φ). For future reference it is also useful to recall how one may also expand the logarithm of Z¯(J); we write, Z¯(J) = exp[W¯ (J)] Z W¯ (J) = ln Z¯(J) = ln dφP (φ)eφ: (6) 1 Now suppose we make a power series expansion of W¯ (J), i.e., 1 X 1 W¯ (J) = C J n; (7) n! n n=0 where the Cn, known as "cumulants", are just @nW¯ (J) C = j : (8) n @J n J=0 The relationship between the cumulants Cn and moments gn is easily found. -

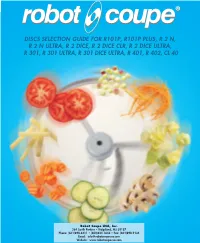

Discs Selection Guide for R101p, R101p Plus, R 2 N, R 2 N Ultra, R 2 Dice, R 2 Dice Clr, R 2 Dice Ultra, R 301, R 301 Ultra

R 301 Dice Ultra, R 402 and CL 40 ONLY Julienne Dicing R 2 Dice, R 2 Dice CLR, R 2 Dice Ultra ONLY R 101P, R 101P Plus, R 2 N, R 2 N CLR, R 2 N Ultra, R 2 Dice, R 2 Dice Ultra, R 301, R 301 Ultra, R 301 Dice Ultra, R 401, R 402 and CL 40 8x8 mm* 10x10 mm* 12x12 mm* (5/16” x 5/16”) (3/8” x 3/8”) (15/32” x 15/32”) Ref. 27113 Ref. 27114 Ref. 27298 Ref. 27264 Ref. 27290 DISCS SELECTION GUIDE FOR R101P, R101P PLUS, R 2 N, 2x2 mm 2x4 mm 2x6 mm Ref. 27265 (5/64” x 5/64”) (5/64” x 5/32”) (5/64” x 1/4”) R 2 N ULTRA, R 2 DICE, R 2 DICE CLR, R 2 DICE ULTRA, Ref. 27599 Ref. 27080 Ref. 27081 R 301, R 301 ULTRA, R 301 DICE ULTRA, R 401, R 402, CL 40 * Use Dice Cleaning Kit to Clean (ref. 39881) French Fries R 301 Dice Ultra, R 402 and CL 40 ONLY 8x8 mm 10x10 mm (5/16” x 5/16”) (3/8” x 3/8”) 4x4 mm 6x6 mm 8x8 mm Ref. 27116 Ref. 27117 (5/32”x 5/32”) (1/4”x 1/4”) (5/16” x 5/16”) Ref. 27047 Ref. 27610 Ref. 27048 Dice Cleaning Kit Reversible grid holder • One side for Smaller Dicing Unit's discs: R 2 Dice, R 301 Dice Ultra, R 402 and CL 40 • One side for Larger Dicing Unit's discs: R 502, R 602 V.V., CL 50, CL 50 Gourmet, CL 51, Cleaning tool CL 52, CL 55 and CL 60 dicing grids Dicing grid cleaning tool 5 mm (3/16”), 8 mm (5/16”) or 10 mm (3/8”) Robot Coupe USA, Inc. -

Ffontiau Cymraeg

This publication is available in other languages and formats on request. Mae'r cyhoeddiad hwn ar gael mewn ieithoedd a fformatau eraill ar gais. [email protected] www.caerphilly.gov.uk/equalities How to type Accented Characters This guidance document has been produced to provide practical help when typing letters or circulars, or when designing posters or flyers so that getting accents on various letters when typing is made easier. The guide should be used alongside the Council’s Guidance on Equalities in Designing and Printing. Please note this is for PCs only and will not work on Macs. Firstly, on your keyboard make sure the Num Lock is switched on, or the codes shown in this document won’t work (this button is found above the numeric keypad on the right of your keyboard). By pressing the ALT key (to the left of the space bar), holding it down and then entering a certain sequence of numbers on the numeric keypad, it's very easy to get almost any accented character you want. For example, to get the letter “ô”, press and hold the ALT key, type in the code 0 2 4 4, then release the ALT key. The number sequences shown from page 3 onwards work in most fonts in order to get an accent over “a, e, i, o, u”, the vowels in the English alphabet. In other languages, for example in French, the letter "c" can be accented and in Spanish, "n" can be accented too. Many other languages have accents on consonants as well as vowels. -

Percent R, X and Z Based on Transformer KVA

SHORT CIRCUIT FAULT CALCULATIONS Short circuit fault calculations as required to be performed on all electrical service entrances by National Electrical Code 110-9, 110-10. These calculations are made to assure that the service equipment will clear a fault in case of short circuit. To perform the fault calculations the following information must be obtained: 1. Available Power Company Short circuit KVA at transformer primary : Contact Power Company, may also be given in terms of R + jX. 2. Length of service drop from transformer to building, Type and size of conductor, ie., 250 MCM, aluminum. 3. Impedance of transformer, KVA size. A. %R = Percent Resistance B. %X = Percent Reactance C. %Z = Percent Impedance D. KVA = Kilovoltamp size of transformer. ( Obtain for each transformer if in Bank of 2 or 3) 4. If service entrance consists of several different sizes of conductors, each must be adjusted by (Ohms for 1 conductor) (Number of conductors) This must be done for R and X Three Phase Systems Wye Systems: 120/208V 3∅, 4 wire 277/480V 3∅ 4 wire Delta Systems: 120/240V 3∅, 4 wire 240V 3∅, 3 wire 480 V 3∅, 3 wire Single Phase Systems: Voltage 120/240V 1∅, 3 wire. Separate line to line and line to neutral calculations must be done for single phase systems. Voltage in equations (KV) is the secondary transformer voltage, line to line. Base KVA is 10,000 in all examples. Only those components actually in the system have to be included, each component must have an X and an R value. Neutral size is assumed to be the same size as the phase conductors. -

Medical Terminology Abbreviations Medical Terminology Abbreviations

34 MEDICAL TERMINOLOGY ABBREVIATIONS MEDICAL TERMINOLOGY ABBREVIATIONS The following list contains some of the most common abbreviations found in medical records. Please note that in medical terminology, the capitalization of letters bears significance as to the meaning of certain terms, and is often used to distinguish terms with similar acronyms. @—at A & P—anatomy and physiology ab—abortion abd—abdominal ABG—arterial blood gas a.c.—before meals ac & cl—acetest and clinitest ACLS—advanced cardiac life support AD—right ear ADL—activities of daily living ad lib—as desired adm—admission afeb—afebrile, no fever AFB—acid-fast bacillus AKA—above the knee alb—albumin alt dieb—alternate days (every other day) am—morning AMA—against medical advice amal—amalgam amb—ambulate, walk AMI—acute myocardial infarction amt—amount ANS—automatic nervous system ant—anterior AOx3—alert and oriented to person, time, and place Ap—apical AP—apical pulse approx—approximately aq—aqueous ARDS—acute respiratory distress syndrome AS—left ear ASA—aspirin asap (ASAP)—as soon as possible as tol—as tolerated ATD—admission, transfer, discharge AU—both ears Ax—axillary BE—barium enema bid—twice a day bil, bilateral—both sides BK—below knee BKA—below the knee amputation bl—blood bl wk—blood work BLS—basic life support BM—bowel movement BOW—bag of waters B/P—blood pressure bpm—beats per minute BR—bed rest MEDICAL TERMINOLOGY ABBREVIATIONS 35 BRP—bathroom privileges BS—breath sounds BSI—body substance isolation BSO—bilateral salpingo-oophorectomy BUN—blood, urea, nitrogen -

Y=Yes, N=No, C=Conditional CODE Mandatory (Y/N/C)* DECODE Description COAF Y to Be Used Here Instead of COAF: ISSUER DISCLOSURE

CODE Mandatory DECODE Description (Y/N/C)* COAF Y To be used here instead This field is used to show the official and of COAF: ISSUER unique identification assigned to a DISCLOSURE REQUEST shareholder’s identification disclosure IDENTIFIER request process by the issuer, or third party nominated by it. DTCM N DATE CALCULATION Indicates the logical method to be used to METHOD determine and communicate from which date the shares have been held. The two possible values are LIFO and FIFO. For further guidance please refer to the Market Standards for Shareholder Identification. FWRI N FORWARD REQUEST TO Indicates whether the request is to be NEXT INTERMEDIARY forwarded to and responded by intermediaries down the chain of intermediaries. If to be forwarded, the indicator (Y) is added. If not to be forwarded, the indicator will either be (N) or not be present. INFO N ADDITIONAL Any additional information will be stated INFORMATION here. INME N ISSUER NAME Name of Issuer of the ISIN ISDD Y ISSUER DISCLOSURE Latest date/time set by the issuer, or a DEADLINE third party appointed by the issuer, at which the response to the request to disclose shareholder identity shall be provided by each intermediary to the Response Recipient. RADR C ADDRESS OF RECIPIENT Address of the party to which the disclosure response must be sent. RADT N ADDRESS TYPE OF Address type to be used for the Response RECIPIENT Recipient, e.g. BIC, Email or URL RBIC C BIC OF RECEPIENT BIC of Response Recipient REML C EMAIL ID OF RECEPIENT Email Address of Response Recipient RLEI N LEI OF RECEPIENT Legal Entity Identifier of Response Recipient RNME N RECEPIENT NAME Name of Response Recipient RTCI N RESPONSE THROUGH Indicates whether the shareholder CHAIN OF identification disclosure response is to be INTERMEDIARIES sent back up the chain of intermediaries or directly to the determined Response Recipient.