KTS-A Memory Management Control User's Guide Digital Equipment Corporation • Maynard, Massachusetts

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pdp11-40.Pdf

processor handbook digital equipment corporation Copyright© 1972, by Digital Equipment Corporation DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation. ii TABLE OF CONTENTS CHAPTER 1 INTRODUCTION 1·1 1.1 GENERAL ............................................. 1·1 1.2 GENERAL CHARACTERISTICS . 1·2 1.2.1 The UNIBUS ..... 1·2 1.2.2 Central Processor 1·3 1.2.3 Memories ........... 1·5 1.2.4 Floating Point ... 1·5 1.2.5 Memory Management .............................. .. 1·5 1.3 PERIPHERALS/OPTIONS ......................................... 1·5 1.3.1 1/0 Devices .......... .................................. 1·6 1.3.2 Storage Devices ...................................... .. 1·6 1.3.3 Bus Options .............................................. 1·6 1.4 SOFTWARE ..... .... ........................................... ............. 1·6 1.4.1 Paper Tape Software .......................................... 1·7 1.4.2 Disk Operating System Software ........................ 1·7 1.4.3 Higher Level Languages ................................... .. 1·7 1.5 NUMBER SYSTEMS ..................................... 1-7 CHAPTER 2 SYSTEM ARCHITECTURE. 2-1 2.1 SYSTEM DEFINITION .............. 2·1 2.2 UNIBUS ......................................... 2-1 2.2.1 Bidirectional Lines ...... 2-1 2.2.2 Master-Slave Relation .. 2-2 2.2.3 Interlocked Communication 2-2 2.3 CENTRAL PROCESSOR .......... 2-2 2.3.1 General Registers ... 2-3 2.3.2 Processor Status Word ....... 2-4 2.3.3 Stack Limit Register 2-5 2.4 EXTENDED INSTRUCTION SET & FLOATING POINT .. 2-5 2.5 CORE MEMORY . .... 2-6 2.6 AUTOMATIC PRIORITY INTERRUPTS .... 2-7 2.6.1 Using the Interrupts . 2-9 2.6.2 Interrupt Procedure 2-9 2.6.3 Interrupt Servicing ............ .. 2-10 2.7 PROCESSOR TRAPS ............ 2-10 2.7.1 Power Failure .............. -

Lecture 04 Linear Structures Sort

Algorithmics (6EAP) MTAT.03.238 Linear structures, sorting, searching, etc Jaak Vilo 2018 Fall Jaak Vilo 1 Big-Oh notation classes Class Informal Intuition Analogy f(n) ∈ ο ( g(n) ) f is dominated by g Strictly below < f(n) ∈ O( g(n) ) Bounded from above Upper bound ≤ f(n) ∈ Θ( g(n) ) Bounded from “equal to” = above and below f(n) ∈ Ω( g(n) ) Bounded from below Lower bound ≥ f(n) ∈ ω( g(n) ) f dominates g Strictly above > Conclusions • Algorithm complexity deals with the behavior in the long-term – worst case -- typical – average case -- quite hard – best case -- bogus, cheating • In practice, long-term sometimes not necessary – E.g. for sorting 20 elements, you dont need fancy algorithms… Linear, sequential, ordered, list … Memory, disk, tape etc – is an ordered sequentially addressed media. Physical ordered list ~ array • Memory /address/ – Garbage collection • Files (character/byte list/lines in text file,…) • Disk – Disk fragmentation Linear data structures: Arrays • Array • Hashed array tree • Bidirectional map • Heightmap • Bit array • Lookup table • Bit field • Matrix • Bitboard • Parallel array • Bitmap • Sorted array • Circular buffer • Sparse array • Control table • Sparse matrix • Image • Iliffe vector • Dynamic array • Variable-length array • Gap buffer Linear data structures: Lists • Doubly linked list • Array list • Xor linked list • Linked list • Zipper • Self-organizing list • Doubly connected edge • Skip list list • Unrolled linked list • Difference list • VList Lists: Array 0 1 size MAX_SIZE-1 3 6 7 5 2 L = int[MAX_SIZE] -

Specification of Bit Handling Routines AUTOSAR CP Release 4.3.1

Specification of Bit Handling Routines AUTOSAR CP Release 4.3.1 Document Title Specification of Bit Handling Routines Document Owner AUTOSAR Document Responsibility AUTOSAR Document Identification No 399 Document Status Final Part of AUTOSAR Standard Classic Platform Part of Standard Release 4.3.1 Document Change History Date Release Changed by Change Description 2017-12-08 4.3.1 AUTOSAR Addition on mnemonic for boolean Release as “u8”. Management Editorial changes 2016-11-30 4.3.0 AUTOSAR Removal of the requirement Release SWS_Bfx_00204 Management Updation of MISRA violation com- ment format Updation of unspecified value range for BitPn, BitStartPn, BitLn and ShiftCnt Clarifications 1 of 42 Document ID 399: AUTOSAR_SWS_BFXLibrary - AUTOSAR confidential - Specification of Bit Handling Routines AUTOSAR CP Release 4.3.1 Document Change History Date Release Changed by Change Description 2015-07-31 4.2.2 AUTOSAR Updated SWS_Bfx_00017 for the Release return type of Bfx_GetBit function Management from 1 and 0 to TRUE and FALSE Updated chapter 8.1 for the defini- tion of bit addressing and updated the examples of Bfx_SetBit, Bfx_ClrBit, Bfx_GetBit, Bfx_SetBits, Bfx_CopyBit, Bfx_PutBits, Bfx_PutBit Updated SWS_Bfx_00017 for the return type of Bfx_GetBit function from 1 and 0 to TRUE and FALSE without changing the formula Updated SWS_Bfx_00011 and SWS_Bfx_00022 for the review comments provided for the exam- ples In Table 2, replaced Boolean with boolean In SWS_Bfx_00029, in example re- placed BFX_GetBits_u16u8u8_u16 with Bfx_GetBits_u16u8u8_u16 2014-10-31 4.2.1 AUTOSAR Correct usage of const in function Release declarations Management Editoral changes 2014-03-31 4.1.3 AUTOSAR Editoral changes Release Management 2013-10-31 4.1.2 AUTOSAR Improve description of how to map Release functions to C-files Management Improve the definition of error classi- fication Editorial changes 2013-03-15 4.1.1 AUTOSAR Change return value of Test Bit API Administration to boolean. -

RISC-V Bitmanip Extension Document Version 0.90

RISC-V Bitmanip Extension Document Version 0.90 Editor: Clifford Wolf Symbiotic GmbH [email protected] June 10, 2019 Contributors to all versions of the spec in alphabetical order (please contact editors to suggest corrections): Jacob Bachmeyer, Allen Baum, Alex Bradbury, Steven Braeger, Rogier Brussee, Michael Clark, Ken Dockser, Paul Donahue, Dennis Ferguson, Fabian Giesen, John Hauser, Robert Henry, Bruce Hoult, Po-wei Huang, Rex McCrary, Lee Moore, Jiˇr´ıMoravec, Samuel Neves, Markus Oberhumer, Nils Pipenbrinck, Xue Saw, Tommy Thorn, Andrew Waterman, Thomas Wicki, and Clifford Wolf. This document is released under a Creative Commons Attribution 4.0 International License. Contents 1 Introduction 1 1.1 ISA Extension Proposal Design Criteria . .1 1.2 B Extension Adoption Strategy . .2 1.3 Next steps . .2 2 RISC-V Bitmanip Extension 3 2.1 Basic bit manipulation instructions . .4 2.1.1 Count Leading/Trailing Zeros (clz, ctz)....................4 2.1.2 Count Bits Set (pcnt)...............................5 2.1.3 Logic-with-negate (andn, orn, xnor).......................5 2.1.4 Pack two XLEN/2 words in one register (pack).................6 2.1.5 Min/max instructions (min, max, minu, maxu)................7 2.1.6 Single-bit instructions (sbset, sbclr, sbinv, sbext)............8 2.1.7 Shift Ones (Left/Right) (slo, sloi, sro, sroi)...............9 2.2 Bit permutation instructions . 10 2.2.1 Rotate (Left/Right) (rol, ror, rori)..................... 10 2.2.2 Generalized Reverse (grev, grevi)....................... 11 2.2.3 Generalized Shuffleshfl ( , unshfl, shfli, unshfli).............. 14 2.3 Bit Extract/Deposit (bext, bdep)............................ 22 2.4 Carry-less multiply (clmul, clmulh, clmulr).................... -

Digital Equipment: Corporation, Maynard, Massachusetts 01754 Digital Equipment Cor1poration • Maynard

TOPS .. 10 DOCUMENTATION DIRECTORY Order Number AA-0858C-TB April 1979 This document describes the manuals for the TOPS·10 Software Notebooks. This manual supersedes the TOPS·10 Documentation Directory, Order Number AA·0858B·TB. To order additional copies; of this document, contact the Software Distribution Center, Digital Equipment: Corporation, Maynard, Massachusetts 01754 digital equipment cor1poration • maynard. massachusetts First Printing, February, 1978 Upda ted, May, 1978 Updated, June, 1978 Updated, August, 1978 Revised, Nov~mber, 1978 Revised, April, 1979 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by DIGITAL and its affiliated companies. copyright©l979 by Digital Equipment Corporation The postage-prepaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation. The following are trademarks of Digital Equipment Corporation: DIGITAL DECsystem-lO MASSBUS DEC DECSYSTEM-20 OMNIBUS PDP DEC tape OS/8 DECUS DIBOL PHA UNIBUS EDUSYSTEM RSTS COMPUTER LABS FLIP CHIP RSX COMTEX -

On the Cognitive Prerequisites of Learning Computer Programming

On the Cognitive Prerequisites of Learning Computer Programming Roy D. Pea D. Midian Kurland Technical Report No. 18 ON THE COGNITIVE PREREQUISITES OF LEARNING COMPUTER PROGRAMMING* Roy D. Pea and D. Midian Kurland Introduction Training in computer literacy of some form, much of which will consist of training in computer programming, is likely to involve $3 billion of the $14 billion to be spent on personal computers by 1986 (Harmon, 1983). Who will do the training? "hardware and software manu- facturers, management consultants, -retailers, independent computer instruction centers, corporations' in-house training programs, public and private schools and universities, and a variety of consultants1' (ibid.,- p. 27). To date, very little is known about what one needs to know in order to learn to program, and the ways in which edu- cators might provide optimal learning conditions. The ultimate suc- cess of these vast training programs in programming--especially toward the goal of providing a basic computer programming compe- tency for all individuals--will depend to a great degree on an ade- quate understanding of the developmental psychology of programming skills, a field currently in its infancy. In the absence of such a theory, training will continue, guided--or to express it more aptly, misguided--by the tacit Volk theories1' of programming development that until now have served as the underpinnings of programming instruction. Our paper begins to explore the complex agenda of issues, promise, and problems that building a developmental science of programming entails. Microcomputer Use in Schools The National Center for Education Statistics has recently released figures revealing that the use of micros in schools tripled from Fall 1980 to Spring 1983. -

DIBOL for Beginners Order No

DIBOL for Beginners Order No. AA-BI77 A-TK April 1984 Supersession: This is a new manual. Operating System: VAXNMS, CTS-300, RSTS/E, Professional, RSX-11 M-Plus, Micro/RSX, Professional CTS-300 Software Version: Applicable to all products containing DIBOL-83 . First Printing, April 1984 The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software on equipment that is not supplied by DIGITAL or its affiliated companies. The specifications and drawings, herein, are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission. Copyright © 1984 by Digital Equipment Corporation. All Rights Reserved The following are trademarks of Digital Equipment Corporation: CTI BUS MASSBUS RSTS DEC PDP RSX DECmate P/OS Tool Kit DECsystem-10 PRO/BASIC UNIBUS DECSYSTEM-20 Professional VAX DECUS PRO/FMS VMS DECwriter PRO/RMS VT DIBOL PROSE Work Processor mamDOma Rainbow CONTENTS Page PREFACE ............................................................................................. v INTRODUCTION ...................................................................... Introduction-1 CHAPTER 1 COMMUNICATING WITH YOUR COMPUTER ........................ 1-1 CHAPTER 2 HOW DATA IS STORED ..................................................... 2-1 Accessing Stored Data............................................................. 2-2 CHAPTER 3 HOW DATA IS PROCESSED ............................................... 3-1 The Basic Data Processing Cycle............................................. -

Reference Guide for X86-64 Cpus

REFERENCE GUIDE FOR X86-64 CPUS Version 2019 TABLE OF CONTENTS Preface............................................................................................................. xi Audience Description.......................................................................................... xi Compatibility and Conformance to Standards............................................................ xi Organization....................................................................................................xii Hardware and Software Constraints...................................................................... xiii Conventions....................................................................................................xiii Terms............................................................................................................xiv Related Publications.......................................................................................... xv Chapter 1. Fortran, C, and C++ Data Types................................................................ 1 1.1. Fortran Data Types....................................................................................... 1 1.1.1. Fortran Scalars.......................................................................................1 1.1.2. FORTRAN real(2).....................................................................................3 1.1.3. FORTRAN 77 Aggregate Data Type Extensions.................................................. 3 1.1.4. Fortran 90 Aggregate Data Types (Derived -

HP Powerpoint 2000 Dark Template

OpenVMS Strategy and Futures OpenVMS Division, Hewlett-Packard © 2006 Hewlett-Packard Development Company, L.P. The information contained herein is subject to change without notice Agenda • OpenVMS Today • OpenVMS Tomorrow • Integrity Update • Summary 2 20 October 2007 OpenVMS Today 3 20 October 2007 The OpenVMS Mission Statement The OpenVMS Division is committed to delivering the OpenVMS roadmaps on time and with outstanding quality. The capabilities that customers have come to rely on in OpenVMS - leadership clustering, high availability, excellent quality, exceptional security and “bullet-proof” operations - will continue to be delivered and enhanced by HP, ensuring product leadership now and in the future. 4 20 October 2007 OpenVMS Celebrating 29 years across 3 computer architectures • Differentiating product • Some key Customers attributes Vodafone Toys R Us − Availability: Disaster Tolerance Deutsche Borse Renault − Clustering: Scalable to 96 nodes, Ikea USPS up to 500 miles apart Verizon Wireless Fraport USAF Commerzbank − Security: System and Cluster Mayo Foundation Intel − Best TCO in class Indian Railways PKE − Strong Integration technology Korean Exchange HKJC Veterans Association Volvo • Core Markets • Market Profile − Finance: Capital Markets, Retail − #1 rated in Healthcare Banking, Wholesale Banking, − 90% of manufacturing of the world’s CPU − Telecommunications: Mobile chips Billing, SMS, Prepaid, HLR, Cable − 30%+ of mobile phones billed in the world & Satellite TV − Over 50% of the world’s SMS transactions − Healthcare: -

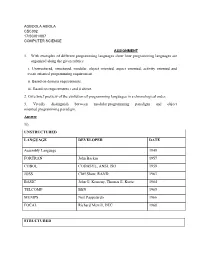

1. with Examples of Different Programming Languages Show How Programming Languages Are Organized Along the Given Rubrics: I

AGBOOLA ABIOLA CSC302 17/SCI01/007 COMPUTER SCIENCE ASSIGNMENT 1. With examples of different programming languages show how programming languages are organized along the given rubrics: i. Unstructured, structured, modular, object oriented, aspect oriented, activity oriented and event oriented programming requirement. ii. Based on domain requirements. iii. Based on requirements i and ii above. 2. Give brief preview of the evolution of programming languages in a chronological order. 3. Vividly distinguish between modular programming paradigm and object oriented programming paradigm. Answer 1i). UNSTRUCTURED LANGUAGE DEVELOPER DATE Assembly Language 1949 FORTRAN John Backus 1957 COBOL CODASYL, ANSI, ISO 1959 JOSS Cliff Shaw, RAND 1963 BASIC John G. Kemeny, Thomas E. Kurtz 1964 TELCOMP BBN 1965 MUMPS Neil Pappalardo 1966 FOCAL Richard Merrill, DEC 1968 STRUCTURED LANGUAGE DEVELOPER DATE ALGOL 58 Friedrich L. Bauer, and co. 1958 ALGOL 60 Backus, Bauer and co. 1960 ABC CWI 1980 Ada United States Department of Defence 1980 Accent R NIS 1980 Action! Optimized Systems Software 1983 Alef Phil Winterbottom 1992 DASL Sun Micro-systems Laboratories 1999-2003 MODULAR LANGUAGE DEVELOPER DATE ALGOL W Niklaus Wirth, Tony Hoare 1966 APL Larry Breed, Dick Lathwell and co. 1966 ALGOL 68 A. Van Wijngaarden and co. 1968 AMOS BASIC FranÇois Lionet anConstantin Stiropoulos 1990 Alice ML Saarland University 2000 Agda Ulf Norell;Catarina coquand(1.0) 2007 Arc Paul Graham, Robert Morris and co. 2008 Bosque Mark Marron 2019 OBJECT-ORIENTED LANGUAGE DEVELOPER DATE C* Thinking Machine 1987 Actor Charles Duff 1988 Aldor Thomas J. Watson Research Center 1990 Amiga E Wouter van Oortmerssen 1993 Action Script Macromedia 1998 BeanShell JCP 1999 AngelScript Andreas Jönsson 2003 Boo Rodrigo B. -

Openvms Debugger Manual

OpenVMS Debugger Manual Order Number: AA–QSBJD–TE April 2001 This manual explains the features of the OpenVMS Debugger for programmers in high-level languages and assembly language. Revision/Update Information: This manual supersedes the OpenVMS Debugger Manual, Version 7.2. Software Version: OpenVMS Alpha Version 7.3 OpenVMS VAX Version 7.3 Compaq Computer Corporation Houston, Texas © 2001 Compaq Computer Corporation Compaq, VAX, VMS, and the Compaq logo Registered in the U.S. Patent and Trademark Office. OpenVMS is a trademark of Compaq Information Technologies Group, L.P. in the United States and other countries. Microsoft, Windows, and Windows NT are trademarks of Microsoft Corporation in the United States and other countries. Intel is a trademark of Intel Corporation in the United States and other countries. Motif, Open Software Foundation, OSF/1, and UNIX are trademarks of The Open Group in the United States and other countries. All other product names mentioned herein may be the trademarks of their respective companies. Confidential computer software. Valid license from Compaq required for possession, use, or copying. Consistent with FAR 12.211 and 12.212, Commercial Computer Software, Computer Software Documentation, and Technical Data for Commercial Items are licensed to the U.S. Government under vendor’s standard commercial license. Compaq shall not be liable for technical or editorial errors or omissions contained herein. The information in this document is provided "as is" without warranty of any kind and is subject to change without notice. The warranties for Compaq products are set forth in the express limited warranty statements accompanying such products. -

The DEC PDP-8 Vectors

The ISP of the PDP-8 Pc is about the most trivial in the book. Chapter 5 — It has only a few data operators, namely, <—,+, (negate), -j, It on A, / 2, X 2, (optional) X, /, and normalize. operates words, The DEC PDP-8 vectors. there are microcoded integers, and boolean However, instructions, which allow compound instructions to be formed in Introduction 1 a single instruction. is the levels dis- The PDP-8 is a single-address, 12-bit-word computer of the second The computer straightforward and illustrates 1. look at it from the down." generation. It is designed for task environments with minimum cussed in Chap. We can easily "top arithmetic computing and small Mp requirements. For example, The C in PMS notation is it can be used to control laboratory devices, such as gas chromoto- 12 graphs or sampling oscilloscopes. Together with special T's, it is C('PDP-8; technology:transistors; b/w; programmed to be a laboratory instrument, such as a pulse height descendants:'PDP-8/S, 'PDP-8/I, 'PDP-8/L; antecedents: 'PDP-5; analyzer or a spectrum analyzer. These applications are typical Mp(core; #0:7; 4096 w; tc:1.5 /is/w); of the laboratory and process control requirements for which the ~ 4 it Pc(Mps(2 w); machine was designed. As another example, can serve as a instruction length:l|2 w message concentrator by controlling telephone lines to which : 1 address/instruction ; occasion- typewriters and Teletypes are attached. The computer operations on data/od:(<— , +, —\, A, —(negate), X 2, stands alone as a small-scale general-purpose computer.