SAF7115 Multistandard Video Decoder with Super-Adaptive Comb Filter

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Video Compression for New Formats

ANNÉE 2016 THÈSE / UNIVERSITÉ DE RENNES 1 sous le sceau de l’Université Bretagne Loire pour le grade de DOCTEUR DE L’UNIVERSITÉ DE RENNES 1 Mention : Traitement du Signal et Télécommunications Ecole doctorale Matisse présentée par Philippe Bordes Préparée à l’unité de recherche UMR 6074 - INRIA Institut National Recherche en Informatique et Automatique Adapting Video Thèse soutenue à Rennes le 18 Janvier 2016 devant le jury composé de : Compression to new Thomas SIKORA formats Professeur [Tech. Universität Berlin] / rapporteur François-Xavier COUDOUX Professeur [Université de Valenciennes] / rapporteur Olivier DEFORGES Professeur [Institut d'Electronique et de Télécommunications de Rennes] / examinateur Marco CAGNAZZO Professeur [Telecom Paris Tech] / examinateur Philippe GUILLOTEL Distinguished Scientist [Technicolor] / examinateur Christine GUILLEMOT Directeur de Recherche [INRIA Bretagne et Atlantique] / directeur de thèse Adapting Video Compression to new formats Résumé en français Adaptation de la Compression Vidéo aux nouveaux formats Introduction Le domaine de la compression vidéo se trouve au carrefour de l’avènement des nouvelles technologies d’écrans, l’arrivée de nouveaux appareils connectés et le déploiement de nouveaux services et applications (vidéo à la demande, jeux en réseau, YouTube et vidéo amateurs…). Certaines de ces technologies ne sont pas vraiment nouvelles, mais elles ont progressé récemment pour atteindre un niveau de maturité tel qu’elles représentent maintenant un marché considérable, tout en changeant petit à petit nos habitudes et notre manière de consommer la vidéo en général. Les technologies d’écrans ont rapidement évolués du plasma, LED, LCD, LCD avec rétro- éclairage LED, et maintenant OLED et Quantum Dots. Cette évolution a permis une augmentation de la luminosité des écrans et d’élargir le spectre des couleurs affichables. -

AN9717: Ycbcr to RGB Considerations (Multimedia)

YCbCr to RGB Considerations TM Application Note March 1997 AN9717 Author: Keith Jack Introduction Converting 4:2:2 to 4:4:4 YCbCr Many video ICs now generate 4:2:2 YCbCr video data. The Prior to converting YCbCr data to R´G´B´ data, the 4:2:2 YCbCr color space was developed as part of ITU-R BT.601 YCbCr data must be converted to 4:4:4 YCbCr data. For the (formerly CCIR 601) during the development of a world-wide YCbCr to RGB conversion process, each Y sample must digital component video standard. have a corresponding Cb and Cr sample. Some of these video ICs also generate digital RGB video Figure 1 illustrates the positioning of YCbCr samples for the data, using lookup tables to assist with the YCbCr to RGB 4:4:4 format. Each sample has a Y, a Cb, and a Cr value. conversion. By understanding the YCbCr to RGB conversion Each sample is typically 8 bits (consumer applications) or 10 process, the lookup tables can be eliminated, resulting in a bits (professional editing applications) per component. substantial cost savings. Figure 2 illustrates the positioning of YCbCr samples for the This application note covers some of the considerations for 4:2:2 format. For every two horizontal Y samples, there is converting the YCbCr data to RGB data without the use of one Cb and Cr sample. Each sample is typically 8 bits (con- lookup tables. The process basically consists of three steps: sumer applications) or 10 bits (professional editing applica- tions) per component. -

12-Bit, Integrated, Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer

12-Bit, Integrated, Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer Data Sheet ADV7403 FEATURES GENERAL DESCRIPTION 4 Noise Shaped Video (NSV)® 12-bit analog-to-digital The ADV7403 is a high quality, single chip, multiformat video converters (ADCs) sampling up to 140 MHz (140 MHz decoder and graphics digitizer. This multiformat decoder supports speed grade only) the conversion of PAL, NTSC, and SECAM standards in the Mux with 12 analog input channels form of composite or S-Video into a digital ITU-R BT.656 format. SCART fast blank support The ADV7403 also supports the decoding of a component Internal antialias filters RGB/YPrPb video signal into a digital YCrCb or RGB pixel output NTSC/PAL/SECAM color standards support stream. The support for component video includes standards 525p/625p component progressive scan support such as 525i, 625i, 525p, 625p, 720p, 1080i, 1250i, and many 720p/1080i component HDTV support other HD and SMPTE standards. Graphic digitization is also Digitizes RGB graphics up to 1280 × 1024 at 75 Hz (SXGA) supported by the ADV7403; it is capable of digitizing RGB (140 MHz speed grade only) graphics signals from VGA to SXGA rates and converting them 24-bit digital input port supports data from DVI/HDMI into a digital RGB or YCrCb pixel output stream. SCART and receiver IC overlay functionality are enabled by the ability of the ADV7403 Any-to-any, 3 × 3 color-space conversion matrix to simultaneously process CVBS and standard definition RGB Industrial temperature range: −40°C to +85°C signals. The fast blank pin controls the mixing of these signals. -

SAA7114 PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb filter, VBI Data Slicer and High Performance Scaler Rev

SAA7114 PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler Rev. 03 — 17 January 2006 Product data sheet 1. General description The SAA7114 is a video capture device for applications at the image port of Video Graphics Array (VGA) controllers. The SAA7114 is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit. It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU 601 compatible color component values. The SAA7114 accepts CVBS or S-video (Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals. An expansion port (X port) for digital video (bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or a video phone codec. At the so called image port (I port) the SAA7114 supports 8-bit or 16-bit wide output data with auxiliary reference data for interfacing to VGA controllers. The target application for the SAA7114 is to capture and scale video images, to be provided as a digital video stream through the image port of a VGA controller, for display via the frame buffer of the VGA, or for capture to system memory. -

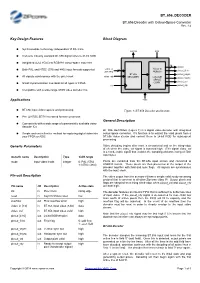

BT 656 DECODER BT.656 Decoder with Colour-Space Converter Key

BT_656_DECODER BT.656 Decoder with Colour-Space Converter Rev. 1.4 Key Design Features Block Diagram ● Synthesizable, technology independent VHDL Core ● Converts industry standard BT.656 digital video to 24-bit RGB ● Integrated 4:2:2 YCbCr to RGB888 colour-space converter ● Both PAL and NTSC (576i and 480i) input formats supported ● All signals synchronous with the pixel clock ● Small implementation size ideal for all types of FPGA ● Compatible with a wide range of SD video decoder ICs Applications ● BT.656 input video capture and processing Figure 1: BT.656 Decoder architecture ● PAL & NTSC SDTV interlaced format conversion General Description ● Connectivity with a wide range of commercially available video decoder ICs BT_656_DECODER (Figure 1) is a digital video decoder with integrated ● Simple and cost-effective method for capturing digital video into colour-space converter. It's function is to extract the valid pixels from a your FPGA or ASIC BT.656 video stream and convert them to 24-bit RGB for subsequent processing. Generic Parameters Video decoding begins after reset is de-asserted and on the rising-edge of clk when the video_val signal is asserted high. (The signal video_val is a clock-enable signal that enables the sampling and processing of each input byte). Generic name Description Type Valid range mode Input video mode integer 0: PAL (576i) Pixels are extracted from the BT.656 input stream and converted to 1: NTSC (480i) RGB888 format. These pixels are then presented at the output of the decoder together with field and sync flags. All signals are synchronous with the input clock. -

10-Bit, 4× Oversampled SDTV Video Decoder with Deinterlacer ADV7280

10-Bit, 4× Oversampled SDTV Video Decoder with Deinterlacer Data Sheet ADV7280 FEATURES APPLICATIONS Worldwide NTSC/PAL/SECAM color demodulation support Smartphone/multimedia handsets One 10-bit analog-to-digital converter (ADC), 4× oversampling Automotive infotainment per channel for CVBS, Y/C, and YPrPb modes DVRs for video security Analog video input channels with on-chip antialiasing filter Media players ADV7280: up to 4 input channels GENERAL DESCRIPTION ADV7280-M: up to 8 input channels Video input support for CVBS (composite), Y/C (S-Video), The ADV7280/ADV7280-M are versatile one-chip, multiformat and YPrPb (component) video decoders. The ADV7280/ADV7280-M automatically detect NTSC/PAL/SECAM autodetection standard analog baseband video signals compatible with worldwide Up to 1.47 V common-mode input range solution NTSC, PAL, and SECAM standards in the form of composite, Excellent common-mode noise rejection capabilities S-Video, and component video. 5-line adaptive 2D comb filter and CTI video enhancement The ADV7280 converts the analog video signals into a YCrCb Adaptive Digital Line Length Tracking (ADLLT), signal 4:2:2 video data stream that is compatible with the 8-bit ITU-R processing, and enhanced FIFO management provide BT.656 interface standard. The ADV7280-M converts the analog mini-time base correction (TBC) functionality video signals into an 8-bit YCrCb 4:2:2 video data stream that is Integrated automatic gain control (AGC) with adaptive output over a mobile industry processor interface (MIPI®) CSI-2 peak white mode interface. Fast switching capability Integrated interlaced-to-progressive (I2P) video output The analog video inputs of the ADV7280/ADV7280-M accept converter single-ended signals. -

YCS 100 N High Quality Digital Decoder with Video Decoder & Encoder Time Base Stabilization N Decodes Composite Video Into S-Video

SIGNAL PROCESSORS YCS 100 n High quality digital decoder with VIDEO DECODER & ENCODER time base stabilization n Decodes composite video into S-video n Encodes S-video into composite video n Simultaneous composite video and S-video output n Buffered loop-throughs for local video monitoring n Compatible with NTSC, PAL, and SECAM video signals n Compact, rack-mountable metal enclosure The Extron YCS 100 is a video transcoder that decodes composite video into S-video, and encodes S-video into composite video. It is ideal for applications requiring video signal conversion, such as conference rooms, classrooms, video production facilities, and residential entertainment systems. www.extron.com DESCRIPTION SPECIFICATIONS (CONT.) The Extron YCS 100 combines a composite video to S-video decoder and an S-video to composite video encoder in a single enclosure. It automatically Minimum/maximum levels ..................... Analog: 0.3 V to 1.5 Vp-p for Y with no offset at detects NTSC, PAL, and SECAM format video signals, and simultaneously unity gain outputs composite video and S-video to allow for recording and display at Impedance ............................................ 75 ohms the same time. The YCS 100 is ideal for applications in conference rooms, Return loss ............................................. -27 dB for Y, -31 dB for C @ 5 MHz Input coupling ........................................ AC coupled classrooms, video production facilities, and residential entertainment systems. Signal processing type ............................ Analog encoding VIDEO The YCS 100 features a high quality digital decoder with time base stabilization to optimize performance with composite video sources, including worn or Video output — encoder porTION multi-generation videotapes, consumer VCRs, and other devices with unstable Number/signal type ............................... -

Design Guide Switchers

System Planning & Design Resource Design Guide Switchers Video Walls Multiviewers Codecs KVM SPECTRUM To Our Valued Customers and Partners, We’re here to help you select the finest equipment that solves your challenges, in an elegant, intuitive, and purpose-built manner. Since 1987, we have been designing and manufacturing innovative solutions for the display, recording and transmission of computer and video signals. With advanced capabilities, proven reliability, and flexible user interfaces, our products are preferred by discriminating customers in commercial, military, industrial, medical, security, energy, and educational markets. In creating this guide, our primary goal is to help simplify the process of choosing the right product for each system. The introductory section includes an overview of current and emerging audiovisual technologies, followed by primers on Networked AV and 4K video technologies, a directory of RGB Spectrum products, case studies, and specifications for all RGB Spectrum products, sample system diagrams, and finally, a glossary of key terms and concepts. RGB Spectrum’s products work together to provide a key part of a system solution — the AV core around which the rest is designed. The case studies illustrate methods to configure both simple and advanced systems. You can expand upon these to meet the requirements of your customers. We are happy to assist our readers to develop better, more effective, and more profitable AV solutions. If you need more assistance, our Design Services team is at the ready to help guide you through the process of determining the optimal RGB Spectrum equipment for your project. Sincerely, Bob Marcus Founder and CEO RGB Spectrum TABLE OF CONTENTS Technology Tutorial . -

AN9644: Composite Video Separation Techniques

APPLICATION NOTE AN9644 Composite Video Separation Techniques Rev. 0.00 Oct 1996 Introduction The most fundamental job of a video decoder is to separate The three analog elements of a composite video signal carry the color from the black and white information for video com- all the information necessary to display a two dimensional posite signals. This task has been achieved many ways since picture on a cathode ray tube (CRT) television. the introduction of color television over 50 years ago. Many different separation methods have been used through the Luminance (a B&W World) years. With the availability of new cost effective technolo- The luminance signal carries the black and white parts of the gies, the consumer has been seeing a gradual improvement picture. This component of the composite video signal in picture quality and detail. Advances in display tube technol- requires the most bandwidth (typically to 5MHz), and signal ogy and semiconductor processes have pushed the techno- integrity, to convey sharp and clear images. Edge informa- logical envelope providing sharper, more robust video. But tion, brightness, and contrast of the image are entirely con- separating the chrominance from the luminance information is tained in the luminance portion of the signal. Until 1947 the especially challenging due to the fact that the signals overlap broadcast video signal was only black and white. To maintain each other in the frequency spectrum. How do you separate compatibility with the installed equipment of the time, color or them, while minimizing display artifacts? chrominance information was added to the luminance signal Composite Signal Construction to create the color composite signal as we know it today. -

TW9966 Data Short

4-Channel Analog Video Decoders and Analog Video Encoder for Automotive Applications TW9966 The TW9966 includes four high quality Provides simultaneous four channel Full D1 NTSC/PAL/SECAM video decoders that convert and CIF time-multiplexed outputs with 54MHz analog composite video signal to digital Integrated five audio ADCs and one audio DAC component YCbCr data for automotive applications. Each channel contains a 10-bit ADC Provides multi-channel audio mixed analog and proprietary clamp and gain controllers and output utilizes a 4H comb filter for separating luminance and chrominance to reduce cross Supports I2S/DSP Master/Slave interface for noise artifacts. The TW9966 adopts the image record output and playback input enhancement techniques, such as IF PCM 8/16 bit and u-Law/A-Law 8-bit for audio compensation filter, CTI and programmable word length peaking. TW9966 also includes one NTSC/PAL video encoder with two 10-bit DAC’s to support Programmable audio sample rate that covers CVBS and YC output. The TW9966 also includes popular frequencies of 8/16/32/44.1/48kHz audio CODEC, which has five audio Supports a two-wire serial host interface Analog-to-Digital converters and one Digital-to-Analog converter. A built-in audio Integrated one video encoder and two 10-bit controller can generate digital outputs for video CMOS DACs recording/mixing and accepts digital input for playback. Integrated clock PLL for 108MHz clock output Ultra low power consumption (Typical Features 666.84mW) Accepts all NTSC(M/4.43) / Automotive Grade -

TVP5158, TVP5157, TVP5156 Four-Channel PAL/NTSC Video

TVP5158, TVP5157, TVP5156 Four-Channel NTSC/PAL Video Decoders With Independent Scalers, Noise Reduction, Auto Contrast, and Flexible Output Formatter for Security and Other Multi-Channel Video Applications Data Manual PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. Literature Number: SLES243G July 2009–Revised April 2013 TVP5158, TVP5157, TVP5156 www.ti.com SLES243G –JULY 2009–REVISED APRIL 2013 Contents 1 Introduction ........................................................................................................................ 8 1.1 Features ...................................................................................................................... 8 1.2 Applications .................................................................................................................. 9 1.3 Description ................................................................................................................... 9 1.4 Related Products ............................................................................................................ 9 1.5 Trademarks ................................................................................................................ 10 1.6 Document Conventions ................................................................................................... 10 1.7 Ordering Information ..................................................................................................... -

SAA7115 NTSC/PAL/SECAM 9-Bit Video Decoder

SAA7115 NTSC/PAL/SECAM 9-bit Video Decoder With adaptive 4-line comb filter, universal VBI slicer, pixel accurate scaler and enhanced Macrovision ® detection COMB FILTER • Universal VBI Slicer • Macrovision ® Philips Semiconductors The SAA7115 provides the front-end digitization and Multistandard video decoding, scaling, processing of analog video inputs for next-generation and data processing on one IC set-top boxes, digital televisions, video projectors, personal video, and DVD recorders.A single-chip 9-bit When a video application demands high quality decoding – flexible Philips Semiconductors video decoder with 2x-oversampling, the SAA7115 scaling and robust data processing – look to the SAA7115 video provides video capture for a range of applications decoder. Highly integrated and supporting worldwide video including advanced large-screen devices such as LCD standards, the SAA7115 is designed to provide a digital video projectors and HDTVs. Decoding NTSC, PAL and stream for any video-input application.This includes input to the SECAM signals using fully automatic standard image port of a VGA controller, for capture to system memory, or detection, the SAA7115 also includes a pixel accurate to provide digital baseband video to any MPEG encoder, LCD H/V scaler, a frame accurate audio clock and an scaler or picture-improvement processor. optional square pixel output rate. The SAA7115 features a two-channel analog preprocessing circuit, Designed with service providers in mind the SAA7115 dual Clock Generation Circuits (CGCs), a digital multistandard complies with Macrovision’s Copy Protection Detect decoder and a high-performance pixel-accurate scaler. It accurately Specification Revision 1.00 and is also well suited for decodes all variations of PAL, SECAM, and NTSC signals into video surveillance systems requiring ultra-fast frame standard ITU-601 compatible component colour values.